Yashwantrao Chavan Maharashtra Open University, Nashik, India

advertisement

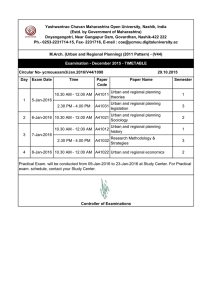

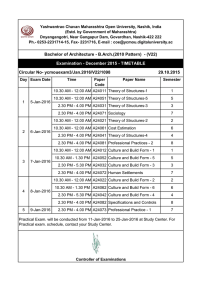

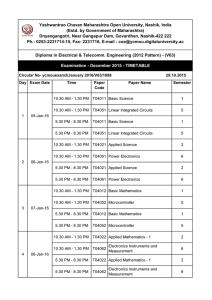

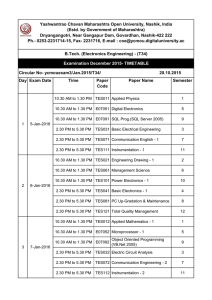

Yashwantrao Chavan Maharashtra Open University, Nashik, India

(Estd. by Government of Maharashtra)

Dnyangangotri, Near Gangapur Dam, Govardhan, Nashik-422 222

Ph.- 0253-2231714-15, Fax- 2231716, E-mail : coe@ycmou.digitaluniversity.ac

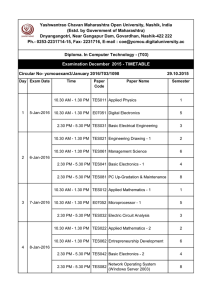

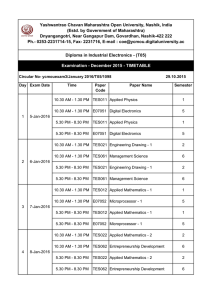

Dip. In Electronics and Telecommunication Engg. {2012 Pattern} - (V63)

Examination December 2015 - TIMETABLE

Circular No- ycmouexam3/Jan.2016/V63/1098

Day Exam Date

1

2

3

Time

Paper

Code

Paper Name

Semester

10.30 AM - 1.30 PM T04011 Basic Science

1

10.30 AM - 1.30 PM T04051 Linear Integrated Circuits

5

2.30 PM - 5.30 PM T04031 Basic Electronics

3

2.30 PM - 5.30 PM T04071 Control System & PLC

7

10.30 AM - 1.30 PM T04021 Applied Science

2

10.30 AM - 1.30 PM T04061 Power Electronics

6

2.30 PM - 5.30 PM T04041 Applied Electronics

4

10.30 AM - 1.30 PM T04012 Basic Mathematics

1

10.30 AM - 1.30 PM T04052 Microcontroller

5

2.30 PM - 5.30 PM T04032 Applied Mathematics - 2

3

Computer Hardware and

Networking

7

10.30 AM - 1.30 PM T04022 Applied Mathematics - 1

2

5-Jan-2016

6-Jan-2016

7-Jan-2016

2.30 PM - 5.30 PM T04072

4

29.10.2015

8-Jan-2016

10.30 AM - 1.30 PM T04062

Electronics Instruments and

Measurements

2.30 PM - 5.30 PM T04042 Digital Electronics

6

4

5

10.30 AM - 1.30 PM T04013 Technical Communication

1

10.30 AM - 1.30 PM T04053 Digital Communication

5

2.30 PM - 5.30 PM T04033 Basic Electrical Engineering

3

2.30 PM - 5.30 PM T04073 Embedded System and Design

7

9-Jan-2016

10.30 AM - 1.30 PM T04023

6

Electronics Components and

Applications

11-Jan-2016 10.30 AM - 1.30 PM T04063 Advance Communication System

2.30 PM - 5.30 PM T04043 Analog Communication

2

6

4

Practical Exam. will be conducted from 14-Jan-2016 to 30-Jan-2016 at Study Center. For Practical

exam. schedule, contact your Study Center.

Controller of Examinations