TMB 2004 Design Table of Contents UCLA High Energy Physics Version 2.02

advertisement

TMB 2004 Design

UCLA High Energy Physics

Version 2.02

June 10, 2004

Table of Contents

CHANGES FROM TMB2001 ..................................................................................................................................................... 3

LIST OF FIGURES ..................................................................................................................................................................... 4

LIST OF TABLES....................................................................................................................................................................... 4

TMB OVERVIEW .................................................................................................................................................................... 5

CATHODE LCT ALGORITHM............................................................................................................................................. 6

CFEB Demultiplex ............................................................................................................................................................ 6

Triad Decode ..................................................................................................................................................................... 6

Layer Staggering................................................................................................................................................................ 6

DiStrip OR......................................................................................................................................................................... 6

Pattern Cell Envelope ........................................................................................................................................................ 6

Priority Enocoding............................................................................................................................................................. 6

DiStrip Patterns.................................................................................................................................................................. 6

DMB Active FEB Signal ................................................................................................................................................... 6

Best 2 LCTs ....................................................................................................................................................................... 6

CLCT Bend Patterns.......................................................................................................................................................... 7

Drift Delay ......................................................................................................................................................................... 7

CLCT Format..................................................................................................................................................................... 7

ALCT+CLCT MATCHING ALGORITHM .......................................................................................................................... 8

Matching Logic.................................................................................................................................................................. 8

LCT Duplication................................................................................................................................................................ 8

LCT Quality....................................................................................................................................................................... 8

MPC Format ...................................................................................................................................................................... 8

VME REGISTERS.................................................................................................................................................................... 9

Addressing Modes ............................................................................................................................................................. 9

Base Address ..................................................................................................................................................................... 9

Register Addresses........................................................................................................................................................... 10

Register Definitions ......................................................................................................................................................... 13

TTC Commands: ............................................................................................................................................................. 43

Embedded Logic Analyzer Scope Channels:................................................................................................................... 44

TMB BOARD STATUS OPERATIONS............................................................................................................................... 47

ID Registers ..................................................................................................................................................................... 47

Digital Serial Numbers .................................................................................................................................................... 47

Power Supply ADC ......................................................................................................................................................... 47

Clock Delays.................................................................................................................................................................... 47

RAT Module Status ......................................................................................................................................................... 48

JTAG Chains ................................................................................................................................................................... 48

DMB READOUT..................................................................................................................................................................... 49

Full-Readout and Local-Readout Format: ....................................................................................................................... 49

Long Header-only Format: .............................................................................................................................................. 50

Short Header-only Format: .............................................................................................................................................. 50

Header Word Descriptions: ............................................................................................................................................. 51

Sample TMB Raw Hits Dump:........................................................................................................................................ 58

TMB SIGNAL SUMMARY ................................................................................................................................................... 59

CCB ................................................................................................................................................................................. 59

Page 1 of 83

06/11/04 1:58 PM

ALCT............................................................................................................................................................................... 60

DMB ................................................................................................................................................................................ 61

CFEB ............................................................................................................................................................................... 61

MPC................................................................................................................................................................................. 62

RPC.................................................................................................................................................................................. 63

VME ................................................................................................................................................................................ 63

JTAG ............................................................................................................................................................................... 63

LEDs................................................................................................................................................................................ 64

TMB Total I/O Count ...................................................................................................................................................... 65

TMB2001 CONNECTORS..................................................................................................................................................... 66

TMB Connector Summary............................................................................................................................................... 66

J0-J4 CFEB0-CFEB4 Connectors.................................................................................................................................... 67

J5 ALCT Cable1 Connector (Receiver)........................................................................................................................... 68

J6 ALCT Cable2 Connector (Transmitter) ...................................................................................................................... 69

J1-J6 SCSI-II 50-Pin Connector Pin Convention............................................................................................................. 70

J7 Xilinx LVDS Xilinx X-Blaster Connector .................................................................................................................. 71

P1 Backplane VME64x J1/P1 Connector ........................................................................................................................ 72

P2A Backplane CCB+DMB Connector........................................................................................................................... 73

P2A Backplane CCB+DMB Connector Continued ......................................................................................................... 74

P2B Backplane DMB Connector ..................................................................................................................................... 75

P3A Backplane MPC Connector ..................................................................................................................................... 76

P3B Backplane RPC+ALCT Connector .......................................................................................................................... 77

Backplane Pin Diagram ................................................................................................................................................... 78

Front Panel Connector Locations..................................................................................................................................... 79

PCB Shunts...................................................................................................................................................................... 80

CCB Front Panel.............................................................................................................................................................. 81

REVISION HISTORY............................................................................................................................................................ 83

Page 2 of 83

06/11/04 1:58 PM

Changes from TMB2001

Old TMB2001

New TMB2004

FPGA

Xilinx XCV1000E

Xilinx XC2V4000

EPROMs

2 x 18V04

4 x 18V04

Clock Delays

2 x PHOS4, 10 channels

Voltage Regulators

Voltage Protection

+3.3V,+1.8V

Not tested for rad tolerance

Zener

3 x 3D3444, 12 channels

with duty cycle correction

+1.8V,+1.5V/+1.2V

Tested rad tolerant

MOSFET

RPC

Not implemented

ALCT Cables

Front panel entry

RAT2004 Transition Module

Receives 4 RPC link boards

RAT2004 Transition Module

and front panel entry

Page 3 of 83

06/11/04 1:58 PM

List of Figures

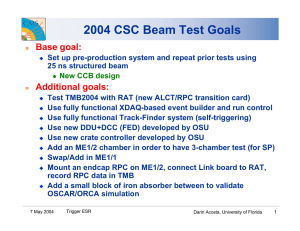

Figure 1 TMB Overview .............................................................................................................................5

Figure 2: 50-Pin PCB Connector (Female) ...............................................................................................70

Figure 3: 50 Pin Cable Connector (Male)..................................................................................................70

Figure 4: 50 Pin PCB Connector Pin Convention .....................................................................................70

List of Tables

Table 1: CCB Signal Summary .................................................................................................................59

Table 2: ALCT Signal Summary...............................................................................................................60

Table 3: DMB Signal Summary ................................................................................................................61

Table 4: CFEB Signal Summary ...............................................................................................................61

Table 5: MPC Signal Summary.................................................................................................................62

Table 6: RPC Signal Summary..................................................................................................................63

Table 7: VME Signal Summary ................................................................................................................63

Table 8: JTAG Signal Summary................................................................................................................63

Table 9: TMB Front Panel LEDs...............................................................................................................64

Table 10: TMB Total I/O Count................................................................................................................65

Table 11: TMB2001 Connector Summary ................................................................................................66

Table 12: J0-J4 CFEB0/4-to-TMB Connectors.........................................................................................67

Table 13: J5 ALCT Cable1 Connector [J10 on ALCT board] .................................................................68

Table 14: J6 ALCT Cable2 Connector [J11 on ALCT board] ..................................................................69

Table 15: J8 Xilinx LVDS X-Blaster Connector.......................................................................................71

Table 16: P1 VME64x Connector .............................................................................................................72

Table 17: P2A Backplane CCB+DMB Connector ....................................................................................73

Table 18: P2B Backplane DMB Connector...............................................................................................75

Table 19: P3A Backplane MPC Connector ...............................................................................................76

Table 20: P3B Backplane RPC+ALCT Connector ...................................................................................77

Page 4 of 83

06/11/04 1:58 PM

TMB Overview

Figure 1 TMB Overview

CFEB0

CFEB1

CFEB2

CFEB3

CFEB4

24 x80MHz

40MHz clock

24 x80MHz

D16

40MHz clock

A24+GA5

46 x40MHz

24 x80MHz

46 x40MHz

40MHz clock

24 x80MHz

VME

CLCT + TMB

Logic

40MHz clock

44 x40MHz

40MHz clock

40MHz clock

CCB

DMB

4 x40MHz

24 x80MHz

32 x80MHz

40MHz clock

1 x80MHz

MPC

28x80MHz+1x10MHz

ALCT

RPC

15x80MHz+5x10MHz

40MHz clock

40 x80MHz

n

8

PROM

1

3 A2

JTAG

Page 5 of 83

06/11/04 1:58 PM

Cathode LCT Algorithm

(documentation incomplete 6/9/2004)

CFEB Demultiplex

(documentation incomplete 6/9/2004)

Triad Decode

(documentation incomplete 6/9/2004)

Layer Staggering

(documentation incomplete 6/9/2004)

DiStrip OR

(documentation incomplete 6/9/2004)

Pattern Cell Envelope

(documentation incomplete 6/9/2004)

Hit pattern LUTs for 1 layer: - = don't care, xxx= any one or more ½-strips hit

Default Cell Envelope

Key on Ly3

------------hs

0123 LUT

ly0 xxx- FEFE

ly1 xxx- FEFE

ly2 xxx- FEFE

ly3 -x-- CCCC

ly4 xxx- FEFE

ly5 xxx- FEFE

Priority Enocoding

(documentation incomplete 6/9/2004)

DiStrip Patterns

(documentation incomplete 6/9/2004)

DMB Active FEB Signal

(documentation incomplete 6/9/2004)

Best 2 LCTs

(documentation incomplete 6/9/2004)

Page 6 of 83

06/11/04 1:58 PM

CLCT Bend Patterns

(documentation incomplete 6/9/2004)

Hit pattern LUTs for 1 layer: - = don't care, x=one ½-strip hit, xx= one hit or the other or both

½-StripID=0123

Layer0

--xLayer1

--xLayer2

-xxLayer3

-x-Layer4

xx-Layer5

x--Pattern 7

-------------hs

0123 LUT

ly0 -x-- CCCC

ly1 -x-- CCCC

ly2 -x-- CCCC

ly3 -x-- CCCC

ly4 -x-- CCCC

ly5 -x-- CCCC

LUT (look-up table contents)

F0F0

F0F0

FCFC

CCCC

EEEE

AAAA

Pattern 6

-------------hs

0123 LUT

ly0 x--- AAAA

ly1 x--- AAAA

ly2 xx-- EEEE

ly3 -x-- CCCC

ly4 -x-- CCCC

ly5 -x-- CCCC

Pattern 5

-------------hs

0123 LUT

ly0 --x- F0F0

ly1 --x- F0F0

ly2 -xx- FCFC

ly3 -x-- CCCC

ly4 -x-- CCCC

ly5 -x-- CCCC

Pattern 4

-------------hs

0123 LUT

ly0 -x-- CCCC

ly1 -x-- CCCC

ly2 -x-- CCCC

ly3 -x-- CCCC

ly4 --x- F0F0

ly5 --x- F0F0

Pattern 3

-------------hs

0123 LUT

ly0 -x-- CCCC

ly1 -x-- CCCC

ly2 -x-- CCCC

ly3 -x-- CCCC

ly4 x--- AAAA

ly5 x--- AAAA

Pattern 2

-------------hs

0123 LUT

ly0 x--- AAAA

ly1 x--- AAAA

ly2 xx-- EEEE

ly3 -x-- CCCC

ly4 -xx- FCFC

ly5 --x- F0F0

Pattern 1

-------------hs

0123 LUT

ly0 --x- F0F0

ly1 --x- F0F0

ly2 -xx- FCFC

ly3 -x-- CCCC

ly4 xx-- EEEE

ly5 x--- AAAA

Drift Delay

(documentation incomplete 6/9/2004)

CLCT Format

(documentation incomplete 6/9/2004)

Page 7 of 83

06/11/04 1:58 PM

ALCT+CLCT Matching Algorithm

(documentation incomplete 6/9/2004)

Matching Logic

(documentation incomplete 6/9/2004)

LCT Duplication

(documentation incomplete 6/9/2004)

// Fill in missing ALCT if CLCT has 2 muons, missing CLCT if ALCT has 2 muons

wire

no_alct = !alct0_vpf;

wire

no_clct = !clct0_vpf;

wire

wire

one_alct = alct0_vpf && !alct1_vpf;

one_clct = clct0_vpf && !clct1_vpf;

wire

wire

two_alct = alct0_vpf && alct1_vpf;

two_clct = clct0_vpf && clct1_vpf;

wire

wire

dupe_alct = one_alct && two_clct;

dupe_clct = one_clct && two_alct;

wire

wire

[MXALCT-1:0]

[MXCLCT-1:0]

alct_dummy = clct0_real[18:17] << 11;

clct_dummy = 0;

// Inserts clct bxn into

// frame for clct_only events

wire

wire

[MXALCT-1:0]

[MXALCT-1:0]

alct0 = (no_alct ) ? alct_dummy : alct0_real;

alct1 = (dupe_alct) ? alct0_real : alct1_real;

// Substitute dummy alct

wire

wire

[MXCLCT-1:0]

[MXCLCT-1:0]

clct0 = (no_clct ) ? clct0_real : clct0_real;

clct1 = (dupe_clct) ? clct0_real : clct1_real;

// Do not

= alct0_vpf || clct0_vpf;

= alct1_vpf || clct1_vpf;

// First muon exists

// Second muon exists

wire first_vpf

wire second_vpf

LCT Quality

(documentation incomplete 6/9/2004)

assign first_nlayers = (alct_first_quality + 3) + clct_first_nhit;

assign second_nlayers = (alct_second_quality + 3) + clct_second_nhit;

// Construct 1st LCT quality

reg

[3:0]

lct_first_quality;

always @(tmb_match or tmb_clct_only or tmb_alct_only or

alct_first_amu or clct_first_hsds or first_nlayers)

begin

if (tmb_match && clct_first_hsds && first_nlayers >= 8)

// ALCT & CLCT match, CLCT ½-strip pattern

lct_first_quality = 4'b1011 + first_nlayers[3:0]-8;

else if (tmb_match && !clct_first_hsds && first_nlayers >= 8)// ALCT & CLCT match, CLCT DiStrip pattern

lct_first_quality = 4'b0110 + first_nlayers[3:0]-8;

else if (tmb_clct_only && clct_first_hsds)

lct_first_quality = 4'b0101;

// CLCT no ALCT, CLCT ½-strip pattern

else if (tmb_clct_only && !clct_first_hsds)

lct_first_quality = 4'b0100;

// CLCT no ALCT, CLCT DiStrip pattern

else if (tmb_alct_only)

lct_first_quality = 4'b0011;

// ALCT only

else if (tmb_match && alct_first_amu)

lct_first_quality = 4'b0010;

else if (tmb_alct_only && alct_first_amu)

lct_first_quality = 4'b0001;

else

lct_first_quality = 4'b000;

end

MPC Format

(documentation incomplete 6/9/2004)

Page 8 of 83

06/11/04 1:58 PM

VME Registers

Addressing Modes

TMB2001 responds to A24D16 VME addressing modes:

Address Modifier 3916, A24 non-privileged mode

Address Modifier 3D16, A24 supervisor mode

It does not respond to byte-addressing modes, so all valid addresses must be even numbers.

Base Address

TMB2001s “base address” bits A[23:19] select which TMB is being addressed by the VME crate

controller. The base address is determined either by 5 VME-slot Geographic Address bits or by the

Local Address set by two on-board hexadecimal rotary switches. Shunt SH62 selects between Geograpic

[1-2] and Local [2-3] modes.

A[23:19] = VME Crate Slot Geographic Address, (Slot= 2 to 21)10

SH62 [1-2]

A[23:19] = Hexadecimal Switch Address SW2x16+SW1

SH62 [2-3]

Multiple TMBs can be addressed simultaneously using a Global Address:

A[23:19] = 2610 Addresses all TMBs in parallel

A[23:19] = 2710 Address all peripheral crate modules

The Hardware Bootstrap Register has a special mode where it can use the Local Address

set by the hexadecimal rotary switches as its Global Address

Page 9 of 83

06/11/04 1:58 PM

Register Addresses

Address

Register Name

Description

ADR_BOOT

Hardware Bootstrap Register

00

02

04

06

ADR_IDREG0

ADR_IDREG1

ADR_IDREG2

ADR_IDREG3

ID Register 0

ID Register 1

ID Register 2

ID Register 3

08

0A

0C

ADR_VME_STATUS

ADR_VME_ADR0

ADR_VME_ADR1

VME Status Register

VME Address read-back

VME Address read-back

0E

10

12

ADR_LOOPBK

ADR_USR_JTAG

ADR_PROM

Loop-back Register

User JTAG

PROM

14

16

18

1A

1C

1E

ADR_DDDSM

ADR_DDD0

ADR_DDD1

ADR_DDD2

ADR_DDDOE

ADR_RATCTRL

3D3444 State Machine Register + Clock DCMs

3D3444 Delay Chip 0

3D3444 Delay Chip 1

3D3444 Delay Chip 2

3D3444 Delay Chip Output Enables

RAT Module Control

20

22

24

26

ADR_STEP

ADR_LED

ADR_ADC

ADR_DSN

Step Register

Front Panel +On-Board LEDs

ADCs

Digital Serials

28

2A

2C

2E

ADR_MOD_CFG

ADR_CCB_CFG

ADR_CCB_TRIG

ADR_CCB_STAT

TMB Configuration

CCB Configuration

CCB Trigger Control

CCB Status

30

32

34

36

38

3A

3C

3E

ADR_ALCT_CFG

ADR_ALCT_INJ

ADR_ALCT0_INJ

ADR_ALCT1_INJ

ADR_ALCT_STAT

ADR_ALCT0_RCD

ADR_ALCT1_RCD

ADR_ALCT_FIFO

ALCT Configuration

ALCT Injector Control

ALCT Injected ALCT0

ALCT Injected ALCT1

ALCT Sequencer Control/Status

ALCT LCT0 Received by TMB

ALCT LCT1 Received by TMB

ALCT FIFO RAM Status

40

ADR_DMB_MON

DMB Monitored signals

Hexadecimal

Add to Base

70000

Page 10 of 83

06/11/04 1:58 PM

42

44

46

48

ADR_CFEB_INJ

ADR_CFEB_INJ_ADR

ADR_CFEB_INJ_WDATA

ADR_CFEB_INJ_RDATA

CFEB Injector Control

CFEB Injector RAM address

CFEB Injector Write Data

CFEB Injector Read Data

4A

4C

4E

50

52

54

56

58

5A

5C

5E

60

62

64

66

ADR_HCM001

ADR_HCM023

ADR_HCM045

ADR_HCM101

ADR_HCM123

ADR_HCM145

ADR_HCM201

ADR_HCM223

ADR_HCM245

ADR_HCM301

ADR_HCM323

ADR_HCM345

ADR_HCM401

ADR_HCM423

ADR_HCM445

CFEB0 Ly0,Ly1 Hot Channel Mask

CFEB0 Ly2,Ly3 Hot Channel Mask

CFEB0 Ly4,Ly5 Hot Channel Mask

CFEB1 Ly0,Ly1 Hot Channel Mask

CFEB1 Ly2,Ly3 Hot Channel Mask

CFEB1 Ly4,Ly5 Hot Channel Mask

CFEB2 Ly0,Ly1 Hot Channel Mask

CFEB2 Ly2,Ly3 Hot Channel Mask

CFEB2 Ly4,Ly5 Hot Channel Mask

CFEB3 Ly0,Ly1 Hot Channel Mask

CFEB3 Ly2,Ly3 Hot Channel Mask

CFEB3 Ly4,Ly5 Hot Channel Mask

CFEB4 Ly0,Ly1 Hot Channel Mask

CFEB4 Ly2,Ly3 Hot Channel Mask

CFEB4 Ly4,Ly5 Hot Channel Mask

68

6A

6C

6E

ADR_SEQ_TRIG_EN

ADR_SEQ_TRIG_DLY0

ADR_SEQ_TRIG_DLY1

ADR_SEQ_ID

Sequencer Trigger Source Enables

Sequencer Trigger Source Delays

Sequencer Trigger Source Delays

Sequencer Board + CSC ID

70

72

74

76

78

7A

7C

ADR_SEQ_CLCT

ADR_SEQ_FIFO

ADR_SEQ_L1A

ADR_SEQ_OFFSET

ADR_SEQ_CLCT0

ADR_SEQ_CLCT1

ADR_SEQ_TRIG_SRC

Sequencer CLCT Configuration

Sequencer FIFO Configuration

Sequencer L1A Configuration

Sequencer Counter Offsets

Sequencer Latched CLCT0

Sequencer Latched CLCT1

Sequencer Trigger Source Read-back

7E

80

82

84

ADR_DMB_RAM_ADR

ADR_DMB_RAM_WDATA

ADR_DMB_RAM_WDCNT

ADR_DMB_RAM_RDATA

Sequencer RAM Address

Sequencer RAM Write Data

Sequencer RAM Word Count

Sequencer RAM Read Data

86

ADR_TMB_TRIG

TMB Trigger Configuration / MPC Accept

88

8A

8C

8E

ADR_MPC0_FRAME0

ADR_MPC0_FRAME1

ADR_MPC1_FRAME0

ADR_MPC1_FRAME1

MPC0 Frame 0 Data sent to MPC

MPC0 Frame 1 Data sent to MPC

MPC1 Frame 0 Data sent to MPC

MPC1 Frame 1 Data sent to MPC

Page 11 of 83

06/11/04 1:58 PM

90

92

94

96

ADR_MPC_INJ

ADR_MPC_RAM_ADR

ADR_MPC_RAM_WDATA

ADR_MPC_RAM_RDATA

MPC Injector Control

MPC Injector RAM address

MPC Injector RAM Write Data

MPC Injector RAM Read Data

98

9A

ADR_SCP_CTRL

ADR_SCP_RDATA

Scope control

Scope read data

9C

9E

A0

A2

A4

ADR_CCB_CMD

ADR_BUF_STAT

ADR_SRLPGM

ADR_ALCT_FIFO1

ADR_ALCT_FIFO2

CCB TTC Command Generator

Buffer Status

SRL LUT Program

ALCT Raw hits RAM Control

ALCT Raw hits RAM data

A6

A8

AA

ADR_ADJCFEB0

ADR_ADJCFEB1

ADR_ADJCFEB2

CFEB Adjacent hs Mask lsbs

CFEB Adjacent hs Mask msbs

CFEB Adjacent ds Mask

AC

AE

B0

B2

B4

ADR_SEQMOD

ADR_SEQSM

ADR_SEQCLCTM

ADR_TMBTIM

ADR_LHC_CYCLE

Sequencer Trigger Modifiers

Sequencer Machine State

Sequencer CLCT msbs

TMB Timing for ALCT*CLCT coincidence

LHC Cycle period, Maximum BXN+1

B6

B8

BA

BC

BE

C0

C2

C4

C6

C8

CA

CC

ADR_RPC_CFG

ADR_RPC_RDATA

ADR_RPC_RAW_DELAY

ADR_RPC_INJ

ADR_RPC_INJ_ADR

ADR_RPC_INJ_WDATA

ADR_RPC_INJ_RDATA

ADR_RPC_BXN_DIFF

ADR_RPC0_HCM

ADR_RPC1_HCM

ADR_RPC2_HCM

ADR_RPC3_HCM

RPC Configuration

RPC Sync Mode Read Data

RPC Raw Hits Delay

RPC Injector Control

RPC Injector RAM Addresses

RPC Injector Write Data

RPC Injector Read Data

RPC BXN Differences

RPC0 Hot Channel Mask

RPC1 Hot Channel Mask

RPC2 Hot Channel Mask

RPC3 Hot Channel Mask

Page 12 of 83

06/11/04 1:58 PM

Register Definitions

Adr 7000016 ADR_BOOT

15

14

13

12

11

R=tdo

R=ready

free

free

/fpga

vme_en

10

/en_fpga

reset_alct

Hardware Bootstrap Register

9

8

7

6

5

4

hard

reset

TMB

hard

reset

ALCT

JTAG

source

vme/fpga

sel3

sel2

sel1

3

2

1

0

sel0

tck

tms

tdi

Bit

Dir

Signal

[ 0]

[ 1]

[ 2]

[ 3]

[ 4]

[ 5]

[ 6]

[ 7]

[ 8]

[ 9]

[10]

[11]

[12]

[13]

[14]

[15]

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R

R

jtag_vme1 (tdi)

jtag_vme2 (tms)

jtag_vme3 (tck)

sel_vme0

sel_vme1

sel_vme2

sel_vme3

vme/usr_en

hard_reset_alct_vme

hard_reset_tmb_vme

/en_fpga_reset_alct

/fpga_vme_en

unassigned

unassigned

vme_ready

jtag_vme0 (tdo)

0

0

0

0

0

0

0

0

0

0

0

0

0

0

x

0

vme tdi

vme tms

vme tck

00XX ALCT JTAG Chain

01XX TMB Mezzanine FPGA + FPGA PROMs Chain

10XX TMB User PROMs JTAG chain

11XX TMB FPGA User JTAG chain

1=JTAG sourced by Bootstrap Register, 0= from FPGA

1=Hard reset to ALCT FPGA

1=Hard reset to TMB FPGA

0=Allow TMB FPGA to hard reset ALCT

0=Allow TMB FPGA to issue VME commands

Available for future use

Available for future use

1=FPGA vme logic indicates ready

vme tdo

[14]

[15]

W

W

unassigned

unassigned

-

No connection on PCB

No connection on PCB

Default

Description

Page 13 of 83

06/11/04 1:58 PM

Adr 00

15

14

0

ADR_IDREG0

13

12

11

0

0

Bits

Dir

[03:00]

[07:04]

[12:08]

[15:13]

R

R

R

R

month

msd2

Typical

ga2

month

msd1

Dir

[07:00]

[15:08]

R

R

month

msd0

month

lsd3

Typical

year

digit3

1

year

digit3

0

fvers3

4

3

2

1

0

fvers2

fvers1

fvers0

ftype3

ftype2

ftype1

ftype0

10

9

month

lsd2

month

lsd1

ID Register 1

8

7

month

lsd0

day

msd3

6

5

4

3

2

1

0

day

msd2

day

msd1

day

msd0

day

lsd3

day

lsd2

day

lsd1

day

lsd0

Description

DD Firmware Version Day

(BCD)

MM Firmware Version Month (BCD)

ADR_IDREG2

13

12

11

year

digit3

2

ga0

5

Firmware type, C=Normal CLCT/TMB, D=Debug loopback

Firmware version code

Geographic address for this board

Unassigned

14

04

Adr 04

15

14

ga1

6

Description

ADR_IDREG1

13

12

11

Bits

year

digit3

3

ga3

C

D

15

0

Adr 02

15

14

month

msd3

ga4

10

ID Register 0

9

8

7

10

year

digit2

3

year

digit2

2

ID Register 2

9

8

7

year

digit2

1

year

digit2

0

year

digit1

3

6

5

4

3

2

1

0

year

digit1

2

year

digit1

1

year

digit1

0

year

digit0

3

year

digit0

2

year

digit0

1

year

digit0

0

Bits

Dir

Typical

Description

[15:00]

R

2002

YYYY Firmware Version Year (BCD)

ADR_IDREG3

13

12

11

10

ID Register 3

9

8

7

rev

code

13

rev

code

10

Adr 06

15

14

rev

code

15

rev

code

14

Bits

Dir

[15:00]

R

rev

code

12

rev

code

11

Typical

rev

code

9

rev

code

8

rev

code

7

6

5

4

3

2

1

0

rev

code

6

rev

code

5

rev

code

4

rev

code

3

rev

code

2

rev

code

1

rev

code

0

Description

Firmware Revcode (as stored in raw hits header)

Page 14 of 83

06/11/04 1:58 PM

Adr 08

15

14

ADR_VME_STATUS

13

12

11

10

TMB

ready

iack

local/

geo

Bits

Dir

[04:00]

[05]

[06]

[07]

[08]

[09]

[10]

[11]

[12]

[13]

[14]

[15]

R

R

R

R

R

R

R

R

R

R

R

R

Adr 0A

15

14

a15

a14

acfail

sysreset

Typical

sysfail

VME Status Register

9

8

7

6

5

sysclk

ds1

as

lword

gap

4

3

2

1

0

ga4

ga3

ga2

ga1

ga0

Description

Crate slot Geographic Address

Crate slot Geographic Address Parity

VME signal lword

VME signal as

VME signal ds1

VME signal sysclk

VME signal sysfail

VME signal sysreset

VME signal acfail

VME signal iack

1=Address mode set to local, 0=Geographic

1=TMB reports ready to boot register

ADR_VME_ADR0

13

12

11

10

VME Address Read-Back

9

8

7

6

5

4

3

2

1

0

a13

a9

a4

a3

a2

a1

lword

a12

a11

a10

a8

a7

a6

a5

Bits

Dir

Typical

Description

[15:00]

R

a[15:0]

VME Address captured at last write cycle {a[15:1},lword}

Adr 0C

15

14

ADR_VME_ADR1

13

12

11

10

TMB

ready

iack

local/

geo

acfail

sysreset

sysfail

VME Address Read-Back

9

8

7

6

5

sysclk

ds1

as

lword

gap

Bits

Dir

Typical

[07:00]

[13:08]

[15:14]

R

R

R

VME Address captured at last write cycle

am[5:0] VME Address modifier

0

Unassigned

4

3

2

1

0

ga4

ga3

ga2

ga1

ga0

Description

a[23:16]

Page 15 of 83

06/11/04 1:58 PM

Adr 0E

15

14

0

ADR_LOOPBK

13

12

11

0

0

0

10

0

0

Bits

Dir

Signal

[00]

[01]

[02]

[03]

[04]

[05]

[06]

[07]

[08]

[09]

[15:10]

R

R

R/W

R

R

R

R

R

R

R

R

cfeb_oe

alct_loop

alct_scsi_rear

alct_oe

rpc_loop

rpc_oe

dmb_loop

dmb_oe

gtl_loop

gtl_oe

--

Adr 10

15

14

tdo

usr

0

gtl_

oe

gtl_

loop

Default

1

0

1

0

0

0

0

0

0

0

0

ADR_USR_JTAG

13

12

11

10

0

Loop-Back Control Register

9

8

7

6

5

4

0

0

0

dmb_

oe

dmb_

loop

rpc_

oe

2

1

0

alct_

oe

alct_

scsi_

rear

alct_

loop

cfeb_

oe

Description

1=CFEB output enable

0=No ALCT loop-back

1=ALCT source=SCSI, 0=RAT module

0=ALCT driver enable

No RPC Loop-back

RPC driver enable

0=No DMB loop-back

0=DMB driver enable

0=No GTL loop-back

0=Enable GTL outputs

Unassigned

User JTAG Register

9

8

7

6

5

0

rpc_

loop

3

sel3

usr

0

sel2

usr

4

3

2

1

0

sel1

usr

sel0

usr

tck

usr

tms

usr

tdi

usr

Bits

Dir

Signal

Description

[00]

[01]

[02]

[06:03]

[14:07]

[15]

R/W

R/W

R/W

R/W

R/W

R

tdi_usr

tms_usr

tck_usr

sel_usr[3:0]

User JTAG Chain TDI (output from FPGA)

User JTAG Chain TMS

User JTAG Chain TCK

User JTAG Chain Select, 0=ALCT,1=Mez,2=UserPROMs,3=UserChain

Unassigned

User JTAG Chain TDO (input to FPGA)

Adr 12

15

14

0

prom_

src

tdo_usr

ADR_PROM

13

12

11

prom1

ce

prom1

oe

prom1

clk

10

prom0

ce

Bits

Dir

Signal

[07:00]

[08]

[09]

[10]

[11]

[12]

[13]

[14]

[15]

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

prom_led[7:0]

prom0_clk

prom0_oe

prom0_ce

prom1_clk

prom1_oe

prom1_ce

prom_src

--

User PROMs Register

9

8

7

6

5

prom0

oe

prom0

clk

Default

CD

0

0

1

0

0

1

0

0

prom_

led7

prom_

led6

prom_

led5

4

3

2

1

0

prom_

led4

prom_

led3

prom_

led2

prom_

led1

prom_

led0

Description

PROM data bus shared with On-Board LEDs

PROM 0 clock

PROM 0 output enable

PROM 0 /chip_enable

PROM 1 clock

PROM 1 output enable

PROM 1 /chip_enable

Data bus 0=on-board LEDs, 1=enabled PROM

Unassigned

Page 16 of 83

06/11/04 1:58 PM

Adr 14

15

14

rpc

lock

dcc

lock

ADR_DDDSM

13

12

11

10

mpc

lock

tmb1

lock

alctd

lock

alct

lock

Bits

Dir

Signal

[00]

[01]

[02]

[03]

[04]

[05]

[06]

[07]

[08]

[09]

[10]

[11]

[12]

[13]

[14]

[15]

R/W

R/W

R/W

R/W

R/W

R/W

R

R

R

R

R

R

R

R

R

R

ddd_start_vme

ddd_clock

ddd_adr_latch

ddd_serial_in

ddd_serial_out

ddd_auto_start

ddd_busy

ddd_verify

lock_tmb_clock0

lock_tmb_clock0d

lock_tmb_clock1

lock_alct_clock

lock_alct_clockd

lock_mpc_clock

lock_dcc_clock

lock_rpc_clock

Adr 16

ADR_DDD0

Bits

Dir

Signal

[03:00]

[07:04]

[11:08]

[15:12]

R/W

R/W

R/W

R/W

delay_ch0[3:0]

delay_ch1[3:0]

delay_ch2[3:0]

delay_ch3[3:0]

Adr 18

ADR_DDD1

Bits

Dir

Signal

[03:00]

[07:04]

[11:08]

[15:12]

R/W

R/W

R/W

R/W

delay_ch4[3:0]

delay_ch5[3:0]

delay_ch6[3:0]

delay_ch7[3:0]

Adr 1A

ADR_DDD2

Bits

Dir

Signal

[03:00]

[07:04]

[11:08]

[15:12]

R/W

R/W

R/W

R/W

delay_ch8[3:0]

delay_ch9[3:0]

delay_ch10[3:0]

delay_ch11[3:0]

3D3444 State Machine Control + DCM Lock Status

9

8

7

6

5

4

3

2

1

0

tmb0d

lock

tmb0

lock

Default

0

0

0

0

0

1

0

1

1

1

1

1

1

1

1

1

ddd

verify

dddsm

busy

auto

start

serial

from

serial

to ddd

adr

latch

ddd

clock

ddd

start

Description

Start DDD State Machine

DDD manual-mode clock

DDD manual-mode address latch

Serial data to DDD chain

Serial data from DDD chain

DDD State Machine autostart state

DDD State Machine busy

DDD data read back verified OK

TMB clock 0 DCM locked

TMB clock 0d DCM locked

TMB clock 1 DCM locked

ALCT rxclock DCM locked

ALCT rxclockd DCM locked

MPC clock DCM locked

DCC clock DCM locked

RPC clock DCM locked

3D3444 Chip 0 Delays, 1 step = 2ns

Default

8

1

2

0

Description

ALCT tx clock, 8 steps = 16ns delay

ALCT rx clock

DMB tx clock

RPC tx clock

3D3444 Chip 1 Delays, 1 step = 2ns

Default

0

0

0

7

Description

TMB1 Clock

MPC Clock

DCC Clock (CFEB duty cycle correction)

CFEB 0 clock

3D3444 Chip 2 Delays, 1 step = 2ns

Default

7

7

7

7

Description

CFEB 1 clock

CFEB 2 clock

CFEB 3 clock

CFEB 4 clock

Page 17 of 83

06/11/04 1:58 PM

Adr 1C

15

14

0

0

[11:00]

[15:12]

10

cfeb

4

cfeb

3

0

R/W

R/W

Adr 1E

15

14

0

ADR_DDDOE

13

12

11

0

0

0

0

0

Dir

Signal

[0]

[1]

[2]

[3]

[4]

[15:5]

R/W

R/W

R/W

R/W

R/W

R/W

rpc_sync

rpc_posneg

rpc_lptmb

rpc_free_tx[0]

rat_dsn_en

--

0

0

10

/tmb

hard

alct

clken

/alct

hard

Bits

Dir

Signal

[00]

[01]

[02]

[03]

[04]

[05]

[06]

[07]

[08]

[09]

[10]

[11]

[12]

[15:13]

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

step_alct

step_dmb

step_rpc

step_cfeb

step_run

cfeb_clock_en0

cfeb_clock_en1

cfeb_clock_en2

cfeb_clock_en3

cfeb_clock_en4

alct_clock_en

/alct_hard_reset_en

/tmb_hard_reset_en

--

cfeb

0

dcc

mpc

0

0

0

0

0

0

0

0

tmb1

3

2

1

0

rpc

tx

dmb

tx

alct

rx

alct

tx

Bit(n)=1=Enable DDD output channel n

Unassigned

RAT Module Control

8

7

6

5

9

Default

ADR_STEP

13

12

11

0

cfeb

1

0FFF

0

Bits

Adr 20

15

14

cfeb

2

ddd_oe[11:0]

Unassigned

ADR_RATCTRL

13

12

11

10

0

3D3444 Chip Output Enables

9

8

7

6

5

4

0

0

0

4

3

2

1

0

rpc

dsn en

rpc

free

rpc

lptm

rpc

posneg

rpc

sync

Description

1=RPC 80MHz sync pattern mode

1=shift RPC data ½ cycle in RAT FPGA + dsn

Not used (for matching rpc_tx array)

Unassigned

1=Enable RAT dsn readout

Unassigned

Clock Single-Step + Hard Resets

9

8

7

6

5

4

3

cfeb4

clken

cfeb3

clken

Default

0

0

0

0

0

1

1

1

1

1

1

1

1

0

cfeb2

clken

cfeb1

clken

cfeb0

clken

step

run

step

cfeb

2

1

0

step

rpc

step

dmb

step

alct

Description

Step ALCT clock

Step DMB clock

Step RPC clock

Step CFEB clock

0=run mode, 1=step clocks

1=enable CFEB0 clock

1=enable CFEB0 clock

1=enable CFEB0 clock

1=enable CFEB0 clock

1=enable CFEB0 clock

1=enable ALCT clock

1=disable ALCT hard reset

1=disable TMB hard reset

Unassigned

Page 18 of 83

06/11/04 1:58 PM

Adr 22

15

14

led

bd7

led

bd6

ADR_LED

13

12

11

10

led

bd5

led

bd2

led

bd4

led

bd3

Front Panel + On-Board LED Register

9

8

7

6

5

4

3

2

led

bd1

led

bd0

VME

NL1A

NMAT

INVP

L1A

CLCT

1

0

ALCT

LCT

Bits

Dir

Signal

Color

Description

[00]

[01]

[02]

[03]

[04]

[05]

[06]

[07]

[08]

[09]

[10]

[11]

[12]

[13]

[14]

[15]

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

led_fp_lct

led_fp_lct

led_fp_clct

led_fp_l1a

led_fp_invp

led_fp_nmat

led_fp_nl1a

led_fp_vme

led_bd0

led_bd1

led_bd2

led_bd3

led_bd4

led_bd5

led_bd6

led_bd7

Blue

Green

Green

Green

Amber

Amber

Red

Green

Blue

Green

Green

Green

Green

Green

Green

Red

LCT TMB matched ALCT+CLCT

ALCT found a muon

CLCT found a muon

L1A level 1 accept

INVP invalid pattern after CSC drift

NMAT no match after ALCT or CLCT triggered

NL1A no L1A after trigger

VME power-up = on, off=vme access flash

Buffer busy[0]

Buffer busy[1]

Buffer busy[2]

Buffer busy[3]

Buffer busy[4]

Buffer busy[5]

Buffer busy[6]

Buffer busy[7]

Adr 24

15

14

0

ADR_ADC

13

12

11

0

0

0

0

Bits

Dir

Signal

[00]

[01]

[02]

[03]

[04]

[05]

[06]

[07]

[08]

[09]

[10]

[15:11]

R

R

R

R

R

R

R/W

R/W

R/W

R/W

R/W

R/W

vstat_5p0v

vstat_3p3v

vstat_1p8v

vstat_1p5v

/t_crit

adc_dout

adc_sclock

adc_din

/adc_cs

smb_clk

smb_data

--

10

9

smb

data

smb

clk

ADC + Power Comparator Register

8

7

6

5

4

3

ADC

/cs

ADC

din

ADC

sclock

ADC

dout

/tcrit

V1.5

2

1

0

V1.8

V3.3

V5.0

Typical Description

1

1

1

1

1

0

0

0

1

0

1

0

1 = 5.0V power supply OK

1 = 3.3V power supply OK

1 = 1.8V power supply OK

1 = 1.5V power supply OK

1 = FPGA and Board Temperature OK

Voltage monitor ADC serial data receive

Voltage monitor ADC serial clock

Voltage monitor ADC serial data transmit

Voltage monitor ADC chip select

Temperature monitor ADC serial clock

Temperature monitor ADC serial data, open drain

Unassigned

Page 19 of 83

06/11/04 1:58 PM

Adr 26

15

14

0

RAT

DSN

Data

ADR_DSN

13

12

11

10

RAT

DSN

Busy

RAT

DSN

Start

RAT

DSN

Init

RAT

DSN

Write

Bits

Dir

Signal

[00]

[01]

[02]

[03]

[04]

[05]

[06]

[07]

[08]

[09]

[10]

[11]

[12]

[13]

[14]

[15]

R/W

R/W

R/W

R

R

R/W

R/W

R/W

R

R

R/W

R/W

R/W

R

R

R/W

tmb_sn_start

tmb_sn_write

tmb_sn_init

tmb_sn_busy

tmb_sn_data

mez_sn_start

mez_sn_write

mez_sn_init

mez_sn_busy

mez_sn_data

rat_sn_start

rat_sn_write

rat_sn_init

rat_sn_busy

rat_sn_data

-

Adr 28

15

14

mez

done

ddd

auto

0

Mez

DSN

Data

Mez

DSN

Busy

Default

ADR_MOD_CFG

13

12

11

10

power

up

Digital Serial Numbers

9

8

7

6

5

led

flash

rate

1

led

flash

rate

0

Bits

Dir

Signal

[00]

[01]

[02]

[03]

[04]

[9:5]

[11:10]

[12]

[13]

[14]

[15]

R/W

R/W

R/W

R/W

R/W

R

RW

RW

R

R

R

led_fp_src_vme

led_fp_cylon

led_flash_on_stop

led_bd_src_vme

led_bd_cylon

cfeb_exists

led_flash_rate[1:0]

power_up

ddd_autostart

mez_done

0

0

0

0

0

0

0

0

0

0

Mez

DSN

Init

Mez

DSN

Write

Mez

DSN

Start

4

3

2

1

0

TMB

DSN

Data

TMB

DSN

Busy

TMB

DSN

Init

TMB

DSN

Write

TMB

DSN

Start

Description

TMB Digital serial SM start

TMB Digital serial write pulse

TMB Digital serial Init pulse

TMB State DSN State Machine busy

TMB State DSN read data

Mez Digital Serial State Machine start

Mez Digital Serial Write pulse

Mez Digital Serial Init pulse

Mez State DSN State Machine busy

Mez State DSN read data

RAT Digital Serial State Machine start

RAT Digital Serial Write pulse

RAT Digital Serial Init pulse

RAT State DSN State Machine busy

RAT State DSN read data

Unassigned

TMB Module Configuration

9

8

7

6

5

4

cfeb4

exists

cfeb3

exists

Default

0

0

1

0

0

1F

0

cfeb2

exists

cfeb1

exists

cfeb0

exists

bdled

cylon

3

2

1

0

bdled

vme

fpled

flash

fpled

cylon

fpled

vme

Description

1=Front Panel LEDs sourced from VME register

1=FP LED Cylon mode, cool

1=Flash Front Panel LEDs on TTT stop_trigger

1=On-Board LEDs sourced from VME register

1=BD LED Cylon mode, cool

CFEB(n) instantiated in this firmware version

LED flash rate in Flash-on-stop mode

Unassigned

Power-up FF

1=3D3444 auto-start enabled

1=Mezzanine FPGA loaded from PROM

Page 20 of 83

06/11/04 1:58 PM

Adr 2A

15

14

ADR_CCB_CFG

13

12

11

10

adb

pulse

async

alct

hard

reset

adb

pulse

sync

tmb

hard

reset

tmb

resout

2

tmb

resout

1

Bits

Dir

Signal

[00]

[01]

[02]

[03]

[04]

[05]

[06]

[08:07]

[11:09]

[12]

[13]

[14]

[15]

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R

R

R

R

R

R

ccb_ignore_rx

ccb_disable_tx

ccb_int_l1a_en

/ccb_status_oe_vme

alct_status_en

clct_status_en

l1accept_vme

tmb_reserved[1:0]

tmb_reserved_out[2:0]

tmb_hard_reset

alct_hard_reset

alct_adb_pulse_sync

alct_adb_pulse_async

ADR_CCB_TRIG

13

12

11

10

l1a

delay

vme7

l1a

delay

vme5

l1a

delay

vme4

tmb

resout

0

tmb

res1

Default

Adr 2C

15

14

l1a

delay

vme6

CCB Configuration

9

8

7

6

l1a

delay

vme3

l1a

delay

vme2

0

0

0

1

1

1

0

tmb

res0

l1a

vme

5

4

3

2

1

0

clct

status

en

alct

status

en

/ccb

status

oe

int

l1aen

disabl

tx

ignore

rx

Description

1=Ignore Received CCB backplane inputs

1=Disble tranmistted CCB backplane outputs

1=Enable internal L1A emulator

1=Enable ALCT+CLCT status to CCB front panel

1=Enable ALCT status GTL outputs

1=Enable CLCT status GTL outputs

1=fire ccb_l1accept oneshot

Future use

Future use

Reload TMB FPGA

Reload ALCT FPGA

ALCT synchronous test pulse

ALCT asynchronous test pulse

CCB Trigger Control

9

8

7

6

5

l1a

delay

vme1

Bits

Dir

Signal

[00]

[01]

[02]

[03]

[04]

[05]

[06]

[07]

[15:08]

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

alct_ext_trig_l1aen

clct_ext_trig_l1aen

seq_trig_l1aen

alct_ext_trig_vme

clct_ext_trig_vme

ext_trig_both

ccb_allow_extbypass

-l1a_delay_vme

l1a

delay

vme0

Default

0

0

1

0

0

0

0

0

7516

0

ccb

exttrig

bypas

ext

trig

both

4

3

2

1

0

clct

ext trg

vme

alct

ext trg

vme

seq

trig

l1aen

clct

ext trg

l1aen

alct

ext trg

l1aen

Description

1=Request ccb l1a on alct ext_trig

1=Request ccb l1a on clct ext_trig

1=Request ccb l1a on sequencer trigger

1=Fire alct_ext_trig oneshot

1=Fire clct_ext_trig oneshot

1=clct_ext_trig fires alct + alct fires clct_trig, DC

1=Allow clct_exttrig_ccb when ccb_ignore_rx=1

Unassigned

Internal L1A delay (not same as sequencer L1A)

Page 21 of 83

06/11/04 1:58 PM

Adr 2E

15

14

ccb

bx0

ADR_CCB_STAT

13

12

11

10

ccb

bcntrs

ccb

res4

ccb

res3

ccb

res2

ccb

res1

Bits

Dir

Signal

[07:00]

[08]

[13:09]

[14]

[15]

R

R

R

R

R

ccb_cmd[7:0]

ccb_clock40_enable

ccb_reserved[4:0]

ccb_bcntres

ccb_bx0

Adr 30

15

14

0

0

0

ccb

res0

alct

res

in4

alct

res

in3

9

Signal

[00]

[01]

[02]

[03]

[06:04]

[11:07]

[15:12]

R/W

R/W

R/W

R/W

R/W

R/W

R/W

cfg_alct_ext_trig_en

cfg_alct_ext_inject_en

cfg_alct_ext_trig

cfg_alct_ext_inject

alct_seq_cmd[2:0]

alct_reserved_in[4:0]

--

0

0

0

0

0

0

Bits

Dir

Signal

[00]

[01]

[02]

[07:03]

[15:08]

R/W

R/W

R/W

R/W

R/W

alct_clear

alct_inject_mux

alct_sync_clct

alct_inj_delay[7:0]

--

4

3

2

1

0

ccb

cmd6

ccb

cmd5

ccb

cmd4

ccb

cmd3

ccb

cmd2

ccb

cmd1

ccb

cmd0

Description

alct

res

in1

alct

res

in0

Default

ADR_ALCT_INJ

13

12

11

10

5

ALCT Configuration

8

7

6

5

alct

res

in2

Dir

ccb

cmd7

6

CCB Command word from TTC

1=TMB 40MHz clock from CCB enabled

Future use

Bunch counter reset from CCB (backplane)

Bunch crossing 0 from CCB (backplane)

1

Bits

Adr 32

15

14

ccb

clock

en

Default

ADR_ALCT_CFG

13

12

11

10

0

CCB Status

9

8

7

1

0

0

0

0

0

0

alct

seq

cmd2

alct

seq

cmd1

4

3

2

1

0

alct

seq

cmd0

assert

alct

ext inj

assert

alct

ext trg

alct

ext inj

en

alct

ext trg

en

Description

1=Enable alct_ext_trig from CCB

1=Enable alct_ext_inject from CCB

1=Assert alct_ext_trig

1=Assert alct_ext_inject

ALCT Sequencer command

ALCT Reserved for future use

Unassigned

ALCT Injector Control

9

8

7

6

5

4

3

2

1

0

inject

delay

4

inject

delay

1

inject

delay

0

link

inject

w clct

start

inject

clear

alct

0

0

Default

0

0

0

816

0

inject

delay

3

inject

delay

2

Description

1=Blank ALCT received data

1=Start ALCT injector State Machine

1=Link ALCT injector with CLCT inject command

Injector delay

Unassigned

Page 22 of 83

06/11/04 1:58 PM

Adr 34

15

14

0

ADR_ALCT0_INJ

13

12

11

10

0

0

1st

bxn

1

1st

bxn

0

1st

key

6

ALCT0 1st Muon To Inject

9

8

7

6

5

4

1st

key

5

Bits

Dir

Signal

[00]

[02:01]

[03]

[10:04]

[12:11]

[15:13]

R/W

R/W

R/W

R/W

R/W

R/W

alct_first_valid

alct_first_quality[1:0]

alct_first_amu

alct_first_key[6:0]

alct_first_bxn[1:0]

--

Adr 36

15

14

0

0

0

2nd

bxn

0

2nd

key

6

2nd

key

5

Dir

Signal

[00]

[02:01]

[03]

[10:04]

[12:11]

[15:13]

R/W

R/W

R/W

R/W

R/W

R/W

alct_second_valid

alct_second_quality[1:0]

alct_second_amu

alct_second_key[6:0]

alct_second_bxn[1:0]

--

0

0

0

0

0

Bits

Dir

Signal

[00]

[02:01]

[04:03]

[08:05]

[15:09]

R

R

R

R

R

alct_cfg_done

seq_status[1:0]

seu_status[1:0]

reserved_out[3:0]

--

1st

key

1

1st

key

0

2nd

key

4

3

st

1

amu

2nd

key

3

1

2

0

6110

1

0

0

1

1st

qualty

0

0

1st

vpf

Description

2nd

key

2

2nd

key

1

2nd

key

0

3

nd

2

amu

2

2nd

qualty

1

1

2nd

qualty

0

0

2nd

vpf

Description

Valid pattern flag

Pattern quality

Accelerator muon flag

Injected ALCT1 key wire-group

Injected ALCT1 bunch crossing number

Unassigned

ALCT Sequencer Control/Status

9

8

7

6

5

4

3

res

out

3

2

1st

qualty

1

Valid pattern flag

Pattern quality

Accelerator muon flag

Injected ALCT0 key wire-group

Injected ALCT0 bunch crossing number

Unassigned

Default

ADR_ALCT_STAT

13

12

11

10

0

1

3

0

7

1

0

1st

key

2

ALCT1 2nd Muon To Inject

9

8

7

6

5

4

Bits

Adr 38

15

14

1st

key

3

Default

ADR_ALCT1_INJ

13

12

11

10

2nd

bxn

1

1st

key

4

res

out

2

res

out

1

res

out

0

seu

stat

1

seu

stat

0

2

1

0

seq

stat

1

seq

stat

0

alct

cfg

done

Typical Description

1

0

0

0

0

ALCT FPGA Configuration done

ALCT Sequencer status

ALCT Single-event-upset status

Future use

Unassigned

Page 23 of 83

06/11/04 1:58 PM

Adr 3A

15

14

0

ADR_ALCT0_RCD

13

12

11

10

0

0

1st

bxn

1

1st

bxn

0

1st

key

6

ALCT 1st Muon Received by TMB

9

8

7

6

5

4

3

1st

key

5

Bits

Dir

Signal

[00]

[02:01]

[03]

[10:04]

[12:11]

[15:13]

R

R

R

R

R

R

alct_first_valid

alct_first_quality[1:0]

alct_first_amu

alct_first_key[6:0]

alct_first_bxn[1:0]

--

Adr 3C

15

14

0

0

0

1st

key

3

1st

key

2

1st

key

1

1st

key

0

2nd

bxn

0

2nd

key

6

2nd

key

5

Dir

Signal

[00]

[02:01]

[03]

[10:04]

[12:11]

[15:13]

R

R

R

R

R

R

alct_second_valid

alct_second_quality[1:0]

alct_second_amu

alct_second_key[6:0]

alct_second_bxn[1:0]

--

1

0-3

0

0-111

0-3

0

alct

data17

alct

data16

2

1st

qualty

1

1

1st

qualty

0

0

1st

vpf

Valid pattern flag

Pattern quality

Accelerator muon flag

Injected ALCT0 key wire-group

Injected ALCT0 bunch crossing number

Unassigned

2nd

key

4

2nd

key

3

2nd

key

2

2nd

key

1

2nd

key

0

nd

2

amu

2

2nd

qualty

1

1

2nd

qualty

0

0

2nd

vpf

Typical Description

1

0-3

0

0-111

0-3

0

Valid pattern flag

Pattern quality

Accelerator muon flag

Injected ALCT1 key wire-group

Injected ALCT1 bunch crossing number

Unassigned

Adr 3E

ADR_ALCT_FIFO

ALCT FIFO RAM Status

(Split with Adr A2 ADR_ALCT_FIFO1 and A4 ADR_ALCT_FIFO2)

15

14

13

12

11

10

9

8

7

6

5

4

0

1

amu

ALCT 2nd Muon Received by TMB

9

8

7

6

5

4

3

Bits

alct

wdcnt

10

st

Typical Description

ADR_ALCT0_RCD

13

12

11

10

2nd

bxn

1

1st

key

4

alct

wdcnt

9

alct

wdcnt

8

alct

wdcnt

7

alct

wdcnt

6

alct

wdcnt

5

alct

wdcnt

4

alct

wdcnt

3

alct

wdcnt

2

3

2

1

0

alct

wdcnt

1

alct

wdcnt

0

alct

RAM

done

alct

RAM

busy

Bits

Dir

Signal

Description

[00]

[01]

[12:02]

[14:13]

[15]

R

R

R

R

R

alct_raw_busy

alct_raw_done

alct_raw_wdcnt[10:0]

alct_raw_rdata[17:16]

--

ALCT raw hits FIFO busy writing ALCT data

ALCT raw hits ready for VME readout

ALCT raw hits word count stored in RAM

ALCT raw hits data MSBs

Unassigned

0

Page 24 of 83

06/11/04 1:58 PM

Adr 40

15

14

0

ADR_DMB_MON

13

12

11

10

0

0

2nd

bxn

1

2nd

bxn

0

2nd

key

6

DMB Monitored Signals

9

8

7

6

5

2nd

key

5

Bits

Dir

Signal

[02:00]

[03]

[08:04]

[11:09]

[15:12]

R

R

R

R

R

dmb_cfeb_calibrate[2:0]

dmb_l1a_release

dmb_reserved_out[4:0]

dmb_reserved_in[2:0]

dmb_rx_ff[3:0]

Adr 42

15

14

inj

start

inj

mask

3

inj

mask

2

2nd

key

3

2nd

key

2

2nd

key

1

4

2nd

key

0

3

nd

2

amu

2

2nd

qualty

1

1

2nd

qualty

0

inj

mask

1

inj

mask

0

9

inj

febsel

4

0

0

0

0

0

CFEB Injector Control

8

7

6

5

inj

febsel

3

inj

febsel

2

inj

febsel

1

inj

febsel

0

4

3

2

1

0

mask

all

cfeb4

mask

all

cfeb3

mask

all

cfeb2

mask

all

cfeb1

mask

all

cfeb0

Dir

Signal

Default

Description

[04:00]

[09:05]

[14:10]

[15]

R/W

R/W

R/W

R/W

mask_all[4:0]

inj_febsel[4:0]

injector_mask[4:0]

inj_trig_vme

111112

0

111112

0

1=Enable, 0=Turn off all CFEBn inputs

1=Select CFEBn for RAM read/write

Enable CFEBn for injector trigger

Start pattern injector

0

0

ADR_CFEB_INJ_ADR

CFEB Injector RAM Address

13

12

11

10

9

8

7

6

5

4

3

2

1

0

inj

adr

7

inj

ren

0

inj

wen

2

inj

wen

1

inj

wen

0

inj

adr

6

inj

adr

5

inj

adr

4

Bits

Dir

Signal

[02:00]

[05:03]

[13:06]

[15:14]

R/W

R/W

R/W

R/W

inj_wen[2:0]

inj_ren[2:0]

inj_rwadr[7:0]

--

Adr 46

15

14

inj

wdata

15

inj

wdata

14

2nd

vpf

DMB calibration

DMB test

DMB future use

DMB future use

DMB received

Bits

Adr 44

15

14

0

Typical Description

ADR_CFEB_INJ

13

12

11

10

inj

mask

4

2nd

key

4

inj

adr

3

inj

adr

2

inj

adr

1

Default

0

0

0

0

inj

adr

0

inj

ren

2

inj

ren

1

Description

1=Write enable injector RAMn (Ly01,23,45)

1=Read enable Injector RAMn

Injector RAM read/write address

Unassigned

ADR_CFEB_INJ_WDATA CFEB Injector Write Data

13

12

11

10

9

8

7

6

5

4

inj

wdata

13

inj

wdata

12

inj

wdata

11

inj

wdata

10

Bits

Dir

Signal

[07:00]

[15:08]

R/W

R/W

inj_wdata[7:0]

inj_wdata[15:8]

inj

wdata

9

inj

wdata

8

inj

wdata

7

Default

0

0

inj

wdata

6

inj

wdata

5

inj

wdata

4

3

2

1

0

inj

wdata

3

inj

wdata

2

inj

wdata

1

inj

wdata

0

Description

Triad bit for addressed Tbin Ly0 (or 2,4)

Triad bit for addressed Tbin Ly1 (or 3,5)

Page 25 of 83

06/11/04 1:58 PM

Adr 48

15

14

inj

rdata

15

ADR_CFEB_INJ_RDATA CFEB Injector Read Data

13

12

11

10

9

8

7

6

5

4

inj

rdata

14

inj

rdata

13

inj

rdata

12

inj

rdata

11

inj

rdata

10

Bits

Dir

Signal

[07:00]

[15:08]

R

R

inj_rdata[7:0]

inj_rdata[15:8]

Adr 4A

15

14

ly1

distrip

7

ly1

distrip

6

ly1

distrip

4

inj

rdata

8

inj

rdata

7

Default

ADR_HCM001

13

12

11

ly1

distrip

5

inj

rdata

9

ly1

distrip

3

0

0

inj

rdata

5

inj

rdata

4

3

2

1

0

inj

rdata

3

inj

rdata

2

inj

rdata

1

inj

rdata

0

Description

Triad bit for addressed Tbin Ly0 (or 2,4)

Triad bit for addressed Tbin Ly1 (or 3,5)

CFEB0 Ly0,Ly1 Hot Channel Mask

9

8

7

6

5

4

3

10

ly1

distrip

2

inj

rdata

6

ly1

distrip

1

ly1

distrip

0

ly0

distrip

7

ly0

distrip

5

ly0

distrip

4

ly0

distrip

3

2

1

0

ly0

distrip

2

ly0

distrip

1

ly0

distrip

0

Bits

Dir

Signal

[07:00]

[15:08]

R/W

R/W

cfeb0_ly0_hcm[7:0]

cfeb0_ly1_hcm[7:0]

Adr 4C

ADR_HCM023

R/W cfeb0_ly2_hcm[7:0]

R/W cfeb0_ly3_hcm[7:0]

CFEB0 Ly2,Ly3 Hot Channel Mask

111111112 1=Enable DiStrip[7:0] Layer 2

111111112 1=Enable DiStrip[7:0] Layer 3

ADR_HCM045

R/W cfeb0_ly4_hcm[7:0]

R/W cfeb0_ly5_hcm[7:0]

CFEB0 Ly4,Ly5 Hot Channel Mask

111111112 1=Enable DiStrip[7:0] Layer 4

111111112 1=Enable DiStrip[7:0] Layer 5

[07:00]

[15:08]

Adr 4E

[07:00]

[15:08]

Adr 50

15

14

ly1

distrip

7

ly1

distrip

6

Default

ly0

distrip

6

ADR_HCM101

13

12

11

ly1

distrip

5

ly1

distrip

4

ly1

distrip

3

1=Enable DiStrip[7:0] Layer 0

1=Enable DiStrip[7:0] Layer 1

CFEB1 Ly0,Ly1 Hot Channel Mask

9

8

7

6

5

4

3

10

ly1

distrip

2

111111112

111111112

Description

ly1

distrip

1

ly1

distrip

0

ly0

distrip

7

ly0

distrip

5

ly0

distrip

4

ly0

distrip

3

2

1

0

ly0

distrip

2

ly0

distrip

1

ly0

distrip

0

Bits

Dir

Signal

[07:00]

[15:08]

R/W

R/W

cfeb1_ly0_hcm[7:0]

cfeb1_ly1_hcm[7:0]

Adr 52

ADR_HCM123

R/W cfeb1_ly2_hcm[7:0]

R/W cfeb1_ly3_hcm[7:0]

CFEB1 Ly2,Ly3 Hot Channel Mask

111111112 1=Enable DiStrip[7:0] Layer 2

111111112 1=Enable DiStrip[7:0] Layer 3

ADR_HCM145

R/W cfeb0_ly4_hcm[7:0]

R/W cfeb0_ly5_hcm[7:0]

CFEB1 Ly4,Ly5 Hot Channel Mask

111111112 1=Enable DiStrip[7:0] Layer 4

111111112 1=Enable DiStrip[7:0] Layer 5

[07:00]

[15:08]

Adr 54

[07:00]

[15:08]

Default

ly0

distrip

6

111111112

111111112

Description

1=Enable DiStrip[7:0] Layer 0

1=Enable DiStrip[7:0] Layer 1

Page 26 of 83

06/11/04 1:58 PM

Adr 56

15

14

ly1

distrip

7

ly1

distrip

6

ADR_HCM201

13

12

11

ly1

distrip