Architecture for Ultra-low Power Multi-channel Resonators Arun Paidimarri

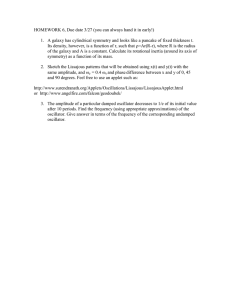

advertisement