Testabi Tree Circuits ent

advertisement

© 1996 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media,

including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution

to servers or lists, or reuse of any copyrighted component of this work in other works.

IEEE TRANSACTIONS ON COMPUTERS. VOL. 45, NO. 8, AUGUST 19%

950

ent Tree Circuits

Testabi

R.D. (Shawn) Blanton, Member, /€E€, and John P. Hayes, Fellow, /E€€

Abstract-The testing properties of a class of regular circuits called convergent trees are investigated. Convergent trees include

such practical circuits as comparators, multiplexers, and carry-lookahead adders. The conditions for the testability of these tree

circuits are derived for a functional fault model. The notion of L-testability is introduced, where the number of tests for a plevel tree

is directly proportional to p , rather than exponential in p . Convergent trees that are C-testable (testable with a fixed number of tests,

regardless of the tree's size) are also characterized. Two design techniques are also introduced that modify arbitrary tree modules in

order to achieve L- and C-testability. Finally, we apply these techniques to the design of a large carry-lookahead adder.

Index Terms-Testability, design-for-testability, synthesis-for-testability. C-testability, test generation, regular circuits, iterative logic

arrays, tree circuits, functional testing.

1 INTRODUCTION

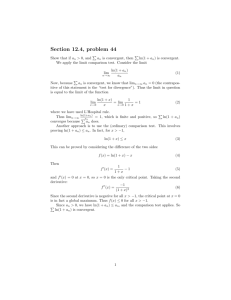

testing of digital circuits is a hard problem, in gen- fanout, but fanout is not allowed among the modules. A

eral, but some circuits are very easy to test. For exam- tree may have multiple outputs and modules interconple, the 8-bit ripple-cany adder of Fig. l a requires only nected by multiple-bit buses. Fig. 2a is an example of an 8eight easily-derived tests to detect all functional faults that bit single-output panty tree constructed from 2-bit EXCLUaffect any one of the full-adder (FA) modules. This testing SIVE-OR modules. A more complex example of a tree-like

property holds regardless of the size of the adder, a prop- circuit is the carq-lookahead adder of Fig. lb.

erty known as C-testability [ 8 ] . The same is not true for the

carry-lookahead adder of Fig. lb. This adder is constructed

from several different module types. It has a test set that

increases with the size of the adder and is hard to derive,

even when the faults are restricted to the single

" stuck-line

(SSL) type.

The ripple-carry adder is an example of a regular circuit

called an (iterative logic) aruay, that is, a circuit composed of

B5-gP - 7

identical modules interconnected as a one-dimensional ar4

' ;

GP

ray. Such circuits are easier to test than their irregular

B4-counterparts because

A,- 9

--

T

HE

~

1) the testing requirements for the circuit's modules are

identical, and

2) the array interconnections pennits tests for one module to be used on other modules.

Array circuits also have other advantages in that they are

easy to scale and lay out for VLSI implementation.

The testing properties of one-dimensional arrays like the

ripple-carry adder have been studied extensively [8], 191,

[141, [161,[17], 1181. Much less attention has been paid to the

more general class of regular circuits known as trees, which

includes the one-dimensional array as a special case. A tvee

is a circuit constructed from identical modules interconnected in a regular fashion so that there is only one signal

path between any two points. The modules or cells used to

construct a tree circuit can have internal reconvergent

2m

2

c-

IEP

* R.D. (Shawn) Blanton is with the Centev for Electronic Design Automation,

ECE Department, Carnegie Mellon University, Pittsburgh, P A 15213.

E-mail: blanton@ece.cmu.edu.

John P. Hayes, is at the Advanced Compute? Architectuve Laboratory,

EECS Department, University of Michigan, A n n Avbor, MI 48109-2122.

Manuscript received Nov. 30,1993; revised July 14,1994.

For information on obtaining reprints of this article, please send e-mail to:

transcomQcompufer.org,and reference IEEECS Log Number C96145.

(4

Fig. 1. Two tree implementations of an 8-bit adder: (a) ripple-carry, (b)

carry-lookahead.

0018-9340196505 00 Q1996 IEEE

BLANTON AND HAYES: TESTABILITY OF CONVERGENT TREE CIRCUITS’

-u

P

(a)

(b)

Fig. 2. Examples of an uncontrolled and a controlled convergent tree:

(a) 8-bit parity circuit, (b) 8-to-1 multiplexer.

It is useful to extend the notion of a tree to make a distinction between data and control inputs. A tree with both

data and control lines is called a controlled tree. The multiplexer circuit of Fig. 2b constructed from 2-to-1 multiplexer

modules is such a circuit; it has three control lines So, SI,

and S2. Both trees of Fig. 2 are convergent, because as one

moves from the input modules to the output module, the

number of (data) signal lines in the circuit decreases. We

will view the array structure of Fig. l a as a special case of a

convergent tree (one that has zero convergence).

A few results have been reported on the testing properties of trees. Kodandapani and Seth [lo] describe a method

for detecting a restricted set of functional faults in tree circuits constructed from AND, OR, NOT, EXCLUSIVE-OR,

and majority gates. Bhattacharya and Hayes 151 present a

design method called level separation for making the number of tests required by tree-like circuits (circuits composed

of multiple convergent trees) proportional to the number of

levels in the circuit. This method applies to circuits composed of multiple trees only. Abraham and Gajski [l] present a recursive algorithm to generate test sets for uncontrolled convergent trees constructed from single-output

modules. The size of the test set generated is proportional

to the number of modules in the tree. Thus, trees that have

much smaller test sets are disadvantaged by this approach.

Because we wish to exploit the regular circuit’s testing

properties in a built-in self-test (BIST) environment, we are

particularly interested in characterizing the conditions required for lowering the number of tests required by regular

circuits, in general, and tree circuits specifically.

Lombardi and Sciuto [ll]have studied the conditions for

C-testability in certain types of uncontrolled convergent trees;

we have shown [61 that their conditions are not always sufficient. In [6],we use a general functional fault model that subsumes the widely used SSL fault model, which may be inadequate for some circuits [2], [15], 1131. Using this fault

model, we analyzed tree circuits in terms of a set of overlapping arrays covering the trees and showed how the circuits

can be efficiently tested by testing these arrays.

Necessary and sufficient conditions were derived in [61

for convergent trees to be C-testable for a given set of faults,

and for trees to be C-testable with the minimum number of

tests. This paper extends these results by presenting necessary and sufficient conditions for convergent trees to be C-

951

testable for all functional faults. In addition, conditions are

presented that characterize the testability of convergent tree

circuits, including trees with control inputs. The notion of

L-testability, that is, testing a convergent tree one level at

time, is also introduced and characterized. Design techniques are presented that allow tree modules to be modified in order to increase their testability by reducing the

number of tests they require.

The remainder of this paper is organized as follows.

Section 2 presents our notation for convergent trees and

shows how they are modeled as overlapping onedimensional arrays. We derive testability conditions for

uncontrolled and controlled convergent trees in Section 3.

In Section 4, we introduce L-testability and also characterize the conditions required for C-testability. Section 5 discusses techniques to make arbitrary tree circuits both Land C-testable. In Section 6, we apply our results to the design of a large carry-lookaheadadder.

2 PRELIMINARIES

We now define our notation for the structure and function

of convergent trees. An n-ary p-level convergent tree C(n, p )

is a circuit constructed from identical modules M arranged

in p levels 1, 2, ..., p. Each level I can have up to n” modules denoted M,,,, M2,,, . ..,Mnt-l Each Ml,l has n state in,I

.

put buses Xf,,,X1:,, ... ,Xr,,

an optional level-control input

bus Zl, and a state output bus Xl,ll;see Fig. 3a. (Subscripts i,

1 will only be used when the corresponding module name is

ambiguous.) The term state bus comes from the iterative

array model of sequential circuits [3]. The word size for

each X’and X is n, and the word size for Z , is n,. Thus, the

set of values that can be assigned to each X’ is

I , = (0, 1, . .., 2”. - 11, where each n,-bit value is denoted

by a decimal number. Similarly, the set of values for Z , is

I , = {O, 1, ..., 2nz- 11. The set of possible output values

that can be produced at the state output

2 is also I,.

Xn’

(a)

(b)

Fig. 3. (a) A general n-ary convergent tree module, (b) the module

redrawn for a one-dimensional array.

The output function of a module Mt,l is denoted 20.A

truth table T is used to define 80.Each row k in T defines

an input combination and output value pair (iv, vk), where

ivkis an ordered set of input values (vo,vl, ..., vn). Here, vo

denotes a control input value, the ordered set vl, v2,..., vn

IEEE TRANSACTIONS ON COMPUERS. VOL. 45, NO. 8, AUGUST 19%

952

denotes a state input vector, and v, denotes the state output

value produce when iv, is applied. The truth-table row k

thus defines the fault-free mapping denoted iv, -+ v, or,

equivalently, 2(ivk1 = v k .

Fig. 4 illustrates the foregoing concepts in the case of a

two-to-one multiplexer module. The multiplexer has n = 2

data inputs X' and X' and a data output 2;these are the

state input-output buses. The select input is the control

The bus widths of n, = 2 and nz = 1 imply that

input Z,.

I, = {O, 1, 2, 3 ) and 1, = {O, 1).Fig. 4b shows the familiar binary-encoded truth table of the multiplexer, while Fig. 4c is

a decimal-encodedversion of the same table.

- 6 33

'

'2,322

'2,2

1'

Array 1 of Type A

Xk.3 3

'

'3,3

2'

'12

z1

Array 2 of Type B

:,'3

'1,3 2'

3

'

Array 3 of Type B

Control input

a4.3 2'

xi,3 3

'

Array 4 of Type A

(b)

Fig. 5. (a) A covering of a 3-level binary ( n = 2) tree with four arrays of

two different types A and 5. (b) The identified arrays redrawn.

xi x'

R

0

0

0

0

0

00 00

00 01

00 10

00 11

01 00

00

01

1

1

1

1

1

10 11

11 00

11 01

11 10

11 11

10

11

11

11

- 4

.. .

2,

10

11

00

11

xi x'

2

00

0

1

2

0

0

0

0

0

02

03

10

3

1

1

1

23

30

31

2

3

1

32

3

3

1

33

3

01

.. ..

0

Fig. 4. (a) Two-to-one multiplexer module Mi,/;(b) binary-encoded truth

table for Mi,,; (c) decimal-encoded truth table for Ad,,)

A contvolled convergent tree CC(n, p ) has a level-control

input bus Z, for each M,,, in level 1, where 1 I 1 < p. A convergent tree is uncontrolled if no Z , exists. If a convergent

tree has

modules on every level 1, then the tree is complete, otherwise it is incomplete. Here, we only consider

complete trees, but our results apply to incomplete trees as

well. An example of a controlled convergent tree that further illustrates our notation is shown in Fig. 5a.

A closer examination of the convergent tree module depicted in Fig. 3a shows that it can be interpreted as the

module of a one-dimensional iterative array; see Fig. 3b.

One state input XI of the n-ary tree module serves as the

module's horizontal state input, while the n - 1 remaining

state inputs and the optional control input are treated as

vertical inputs. The horizontal input XI can be any one of

the n state inputs, gving rise to n different avray types for an

n-ary tree module. A convergent tree can then be viewed as

composed of overlapping one-dimensional arrays of its n

array types. Fig. 5a marks these arrays with rectangles in a

3-level binary (n = 2) controlled convergent tree. The four

arrays of the two types, arbitrarily named A and B, are redrawn separately in Fig. 5b. Type-A arrays have X' as the

horizontal input, while Z , and X' form the vertical inputs.

The type-B array is similarly defined with X' as the horizontal input.

We use the very general functional fault model that assumes only a single module can become faulty. (We later

extend this model slightly for controlled convergent trees.)

A functional fault can change the function of a module to

any other combinational function. Suppose a fault f,

changes the response to input pattern iu,from ul to vi; we

denote this by iv, + (vl,v;) and refer to it as an input pattern fault. The pair of distinct state values (v],u ; ) denoting

the good and faulty output values is the corresponding erYOY. In general, a functional fault is a set of input pattern

faults F = {f,,f2, . . ., fk). The number of input pattern faults is

K(W- 1)for an n-ary module with an input bus width of n,

where W = ZnX and K = 2nnx.1

1.For a controlled convergent tree module K = 2n'nx+"z

.

BLANTON AND HAYES: TESTABILITY OF CONVERGENT TREE CIRCUITS’

xi 2

i

00

01

02

03

10

11

12

13

20

21

22

23

30

31

32

33

0

0

0

0

0

1

2

2

2

2

2

2

2

2

2

xi 2

x

00

01

02

03

10

11

12

13

20

21

22

23

30

31

32

33

0

0

0

1

2

2

2

2

2

2

3

3

3

3

x’x‘

x

00

01

02

03

10

11

12

13

20

21

22

23

30

31

32

33

0

2

0

0

0

0

0

0

1

2

3

2

2

2

2

2

3

2

3

953

rows of the truth table give rise to 16 . 3 = 48 different

input pattern faults since there are 22- 1 = 3 incorrect

output values for each of the 16 input combinations. 0

3 UNCONTROLLED

TREES

First, we examine the testability conditions for uncontrolled

convergent tree circuits of arbitrary size. A regular circuit is

testable for all functional faults if each module of the circuit

can have every possible input combination applied, and

any generated error can be propagated to a primary output

of the circuit. We will show that the testability of convergent tree circuits can be characterized in terms of the testing

properties of their n one-dimensional array types: The testability of the latter was first considered in [91. Below we

define the properties that characterize array testability and

then show how they relate to convergent tree testability.

DEFINITION

1. A module is surjective if its state output function

20 assumes the set of all possible state values IF

DEFINITION

2. A sensitizing vector for an error (vu,V J on input

X’is a set of input values (vl, v,,...,

v’+~,

..., v,) suck

that

x(v,,v 2 r ... 211-1

r

I

vb, vj+lr f . . I

11’11).

EXAMPLE2. From Fig. 6 we see that GP, and GP, are both

surjective, since each value of I, = (0, 1, 2, 3) appears

in the output column 2 of their corresponding truth

tables. GP, is not surjective because the state output

value 3 cannot be produced. The input pattern fault

00 -+(0,3) can affect all three GP implementations. The

fault’s corresponding error (vu,vb) = (0,3) when present

on X’ can be propagated through any of the modules

by applying the sensitizing vector X’ = 1, because

2(1,0) + 2(1,3). The state value 1 is also a sensitizing

vector for the error (0,3) on XI, since 8(0, 1) # 2(3, 1).

LEMMA1 191. A one-dimensional array is testable if and only if

the module is surjective and there is a sensitizing vector for

each possible error (vu,vb) occurring on the module‘s state

input.

We can now give necessary and sufficient conditions for

uncontrolled trees to be testable.

1.An n-ary p-level uncontrolled convergent tree C(n,p )

THEOREM

is testable for any p > 1 if and only if all its n array types

are testable.

EXAMPLE1. Fig. 6 shows three different (decimal-encoded) PROOF.First we show the necessity of the conditions. Astruth tables for the 2-input group generate/propagate

sume that C(n, p ) is testable but there is a array type

(GP) module used for carry-lookahead addition.

called type-j that is not testable, where a type-j array

(They differ only in certain don’t-care values that do

is one in which the state input X’ is the array’s horinot affect the overall addition process.) Suppose a

fault F changes the truth table of a GP module from

GP, to GP,. This fault produces three erroneous responses that can be described by the set of input pattern faults 113 + (2,3), 31 + (2,3), 33 + (2,3)}.The 16

zontal input. By Lemma 1, the type-j array is not testable only if

1) the module is not surjective or

2) there is no sensitizing vector for some error present

on state input X’.

IEEE TWNSACTIONS ON COMPUTERS, VOL 45. NO. 8. AUGUST 1996

954

If the module is not surjective then there is some state

value v, E I, that cannot be generated at the module’s

output 2 . As a result, no internal tree module MI, for

1 < p can have an input combination ivI applied that

has state value nj E iv,. Thus, module sujectivity is

necessary for testability. Now assume there is no sensitizing vector for an error (v,,vj) on state input X’. It

has already been shown that each module must produce every state value u, E I,. Thus, there is at least

one possible input pattern fault that generates an error (v’, n ; ) . In order for C(n, p ) to be testable, there

there are no input combinations that produce the output value 3. From Theorem 1, we know that a convergent tree constructed from modules that are not surjective cannot have every input combination applied

to it. For example, a tree constructed from GP, modules cannot have the state value 3 applied to any of its

intemal modules. Fig. 7a illustrates this problem for a

2-level tree. On the other hand, the GP modules GP,

and GP, are both surjective, therefore, we only need

to check if the required sensitizing vectors exist in order to determine if trees constructed from these modules are testable.

must be a sensitizing vector that propagates this error,

otherwise all modules MI,,for I > 1 cannot be tested

for the fault that produces ( v l ,v ; ). Thus, each possible

I must have a sensitizmg vector

error for state input X

for C(n, p) to be completely testable. This condition

along with module surjectivity implies that the type-j

array is testable (Lemma 1).This must be true for all n

array types, which means that each array type must

be testable for C(n,p ) to be testable.

We turn next to the sufficiency part of the theorem.

Assume all n array types of C(n,

are testable. This

implies that the module is surjective and that there

are sensitizing vectors that will propagate any single

error present on any one of the n state inputs X’, X’,

X3, ..., X“. These conditions insure that any module in

an arbitrarily large tree can have any input combination applied. This follows from the fact that the inputs

to module M,,I in the tree are independent. The proof

is completed by showing the sufficiency of the conditions for error observation. Consider a module M,, af-

p)

fected by an input pattern fault

tu1

-+

( v I ,~ 1 ; ) . M , , is

Error cannot 1

be propagated

be applied

(a)

(b)

Fig. 7. Two-level tree constructed from (a) GP, and (b) G f , modules.

The error-propagation characteristics of a tree module

can be conveniently described by means of a state-pair

graph 181.

DEFINITION

3. A state-pair graph for a module’s state input X’

has an m o r vertex (vr,v,) for every ordered pair of state

values v, # us.A directed edge from (vr,v,) to (vu,vw),labeled with the input combination (vl, u2, ..., vlPl, ur, ilfl,

. .., v,,), exists for every sensitizing vector such that:

X ( q , u2, ...

vr,nl+l, .. . ,nn)= v,

and

controlled by an l-level tree which, as shown, can

A(u*,v2, vl-l, vs,V1+lI .. I v n ) = v,.

have any iul applied if the module is surjective. In reThe state-pair graphs for the n state inputs graphically

sponse to the application of i ~ ;M,,

, will generate the indicate the sensitizing vectors required to propagate ererror ( n l I u ; ) .An error on any module input XL,,-, rors. For example, there is no sensitizing vector that will

must follow a unique path to the tree output. The re- propagate the errors (2, 3) or (3, 2) when present on the X‘

maining state inputs Xk for all k # j , for each module input of the GP, module defined in Fig. 6. This is indicated

by the absence of emanating edges from the corresponding

along the error path are fed by disjoint, independent

subtrees. The independence of these subtrees allows error vertices in the state-pair graph of Fig. 8b. This means

that arrays where X’ is the array’s horizontal input are not

modules along the error path to be simultaneously

Thus, a fault such as 33 -+ (3,2) that affects M,,of

testable.

controlled to input values that will propagate the erFig.

7b cannot be detected. The two state-pair graphs for the

ror. Since each error has a sensitizing vector for every

GP, module (Fig. 9) indicate that every error has a sensitizstate input, the original error ( v ] ,v;) generated by Mz,,

ing vector. The two array types of the GP, module comcan be propagated to the output of an arbitrarily large pletely satisfy Lemma 1, and therefore meet the conditions

convergent tree. Thus, an arbitrary module MI,,in the of Theorem 1. Hence, an arbitrarily large convergent tree

tree is testable for any input pattern fault, so a C(n, p ) constructed from GP, modules is completely testable.

satisfying the conditions of the theorem is completely

3.1 Controlled Trees

testable for all functional faults.

Testing a controlled convergent tree is difficult because the

EXAMPLE3. Reconsider the G P truth tables of Fig. 6. Because arrays that determine a tested module’s sensitization and

each module has n = 2 inputs, there are two array error propagation conditions are no longer independent

types. The two array types of GP,are not testable be- due to the control lines. The following example illustrates

cause the corresponding module is not surjective; this point.

...I

9

BLANTON AND HAYES: TESTABILITY OF CONVERGENT TREE CIRCUITS'

955

03

(a)

Fig. 8. (a) X' state-pair graph, and (b)

x' state-pair graph for GP,.

(a)

Fig. 9. (a) X' state-pair graph, and (b)

2 state-pair graph for GP,.

EXAMPLE4. Fig. 10 shows a 2-level controlled tree con- the tree must be testable for all its input pattern faults, and

structed from 3-input AND modules, with one input each level 1 must be testable for all of the control input

of each module treated as a control line. Consider the faults of the form ZJv,. Notice that the single fault asinput pattern fault 011 + (0, 1). Testing module M,,? sumption is still made, in that only a single input pattern

for this fault requires that a 0 be applied to Z,. This fault or a single control bus fault can occur.

The next result gives sufficient conditions for the test1

= 0 which prevents the error (0, 1) from beforces

ability of controlled convergent trees. Let A ( Z , = a,) be a

ing propagated through M,,,. Thus, the fault 011 + (0, l) partial state output function that only allows input combiis untestable because the control value Z , = 0 required nations that have the control input value 71,.

for fault sensitization prevents the application of senTHEOREM2. An n-ary p-level controlled convergent free CC(n, p )

sitizing vectors for error propagation.

is testable for any p > 1if

z*-0

Z1,=?

1) all its n array types are testable and

2) for each distinct pair of control values v, and vb:

8(Z, = va)f 2 ( Z , = vb),and there exists a state input

= 8(a,,Sc) = v, for each

vector S,such that A(aUII,SC)

state value vcE I,.

Faulty module

This error cannot

be propagtaed

PROOF.

Assume that the conditions of the theorem are satisfied. We first consider the testability of the input patFig. 10. A 2-level controlled convergent tree composed of 3-input AND

tern faults. Because each k(Z, = v z ) is surjective

modules.

(implied by the satisfaction of condition 2), a module

Ml,,

can be controlled via state input values to produce

Controlled tree testing is also complicated by faults on

any state output value, independent of the control

the control input Z,, Z,, . . ., Z,. We assume that each control

value applied to Z,. This means the subtrees controlinput Z, (1 I1 5 p ) can be affected by a set of "stuck-at"

ling the sensitization and error propagation of a given

faults, each of which is denoted Z,/v,, where v, E I , is some

module are, in effect, independent, as in the case of

control input value. A fault Z,/v, causes the control input Z ,

the uncontrolled convergent tree. Consequently, the

of all modules M,,

in level 1 to be stuck-at v,. Because it afremaining

part of the proof concerning input pattern

fects more than one module, the fault Z J v , is not covered

fault testability is similar to that of Theorem 1 and is

by the functional fault model. Thus, for a controlled connot discussed here.

vergent tree to be completely testable, each module Mi,,

in

IEEE TRANSACTIONS ON COMPUTERS. VOL. 45, NO. 8, AUGUST 1996

956

Next we turn to the testability of the control input

faults. Consider an arbitrary control input fault

Z,/v,. If condition 2 is satisfied, there must be a

control input value vug# v, and a state input rector S,

= vl, v2, . . ., v, such that X ( v

cause

0

,S1 ) = X(vL';,S , ) = z 1 7 , be-

2 ( ~= ,vo) # 2 ( ~= ,v,)

for every pair of con-

trol values vo and v,. Applying vo to Z , and So to any

module MI,,will sensitize the fault Z,/z=and cause an

error, say (na,Vb). We have shown that So can be applied to any Ml,!. We have also shown above that a

CC(n, p ) satisfying the conditions of the theorem is

testable for any input pattem fault. This means every

error has a sensitizing vector that will propagate it

through a module. Satisfying condition 2 guarantees

the existence of a SI such that k(q,,S,)= X?(v=,S?) = V,

for every vl E I,. Hence, we can apply fault-free sensitizing vectors to the error path of the generated error (va,vb),which insures that it can be propagated to

the output of an arbitrarily large CC(n, p ) . Thus, a

CC(n, p ) satisfying the conditions of theorem is completely testable for the control input faults as well.

EXAMPLE5. A multiplexer circuit is an example of a useful

controlled convergent tree. The partial functions

X(Z, - 0) and X ( Z , = 1) of the multiplexer module of

Fig. 4 are both surjective. The multiplexer module

also has sensitizing vectors for each possible error for

both state inputs X' and X'. Also note for each state

value vl E I, = (0, 1, 2, 31, there is an ordered set of

state input values S such that k(0,S ) = 20, SI, i.e.,

X ( 0 , 00) = 0 = X(1, OO), k(0, 11) = 1 = 20,ll),

X ( 0 , 22) = 2 = 2(1,221,

and X ( 0 , 33) = 3 = k(l, 33). Thus, the multiplexer

module satisfies the conditions of Theorem 2. Hence,

a controlled convergent tree of any slze constructed

from these multiplexer modules is testable for all input pattern and control input faults. In fact, any controlled convergent tree constructed from wary multiplexer modules is testable.

The conditions of Theorem 2 are not necessary for CC(n,p )

to be testable. We saw in Example 4 that a controlled AND

tree is not testable because the control value Z , = 0 prevents

the application of state values required for error propagation. Suppose we add another signal line to Z,, thus making

a 2-bit control bus. This provides two new control values

that can be used to propagate errors. For example, one

control value can insure that any value applied to the X'

state input is routed to the module output, while the other

' state input. This

control value acts similarly for the X

makes the controlled AND tree completely testable without

satisfying the conditions of Theorem 2. This property of

some controlled convergent trees makes it difficult to find

both necessary and sufficient conditions for testability.

4

c- AND L-TESTABILI-I-Y

In the worst case, the size of a test set is proportional to the

number of modules in the tree under test. For example, consider testing a tree constructed from the GP, module (Fig. 6)

for the input pattem fault f = 22 -+ (2,3).The state-pair graphs

of Fig. 9 show that the error (2,3 ) can only be propagated as (2,

3) and that the input combination 22 does not propagate this

error. Hence, no other module in the error path of the tested

module can be tested for the same fault. Furthermore, several

modules on different paths cannot be simultaneously tested

for f, since the propagated errors (2, 3) will collide at some

module and block error propagation. Consequently, only one

module at a time can be tested for f. The total number of tests

required in this case is equal to the total number of modules in

the tree, which for an n-ary ylerel tree is

P

1

p

1=1

1- np

1-n

='

The number of tests required for a convergent tree circuit can be reduced if the module satisfies certain conditions. Of particular interest are the cases where the test set

size is constant (C-testability)or proportional to the number

of levels in the tree; we refer to the latter as L-testability.

We first examine the L-testability characteristics of convergent tree cirmits. A fault is level-testable (L-testable) in an n-ary

p-level convergent tree if the number of tests required to detect

all single occurrences of the fault is proportional to the number

of levels p . A tree is L-testable if it can be completely tested

with a test set whose size is proportional to p. Below we intuitively describe conditions that insure L-testability, and then

formally state and prove the validity of the conditions.

Each module MI,,on a given level I in a (complete) convergent tree is controlled by identical, independent subtrees

or primary inputs. Thus, it is quite easy to apply the same

input combination to every M,,l, hence we can sensitize all

level4 modules to any given fault simultaneously. If any

error generated by a single module in level I can be propagated to the tree output, regardless of the size of the tree, Ltestability is achieved. A module function that has this

property is an identity function. Ml,l implements an identity

function if it generates an identity value v, E I, only when

all its state values are the same. Fig. 11 gives an example of

a three-input identity function with vl = 0. We now show

that a module that implements an identity function has the

required characteristics for L-testability.

Kl

100

101

Fig. 11. A module that implements an identity function with

VI=0.

THEOREM

3. An n-ary p-level uncontrolled convergent tree C(n, p )

is L-testable if the module's function

tity function and surjective.

k0 is both an iden-

957

BLANTON AND HAYES: TESTABILITY OF CONVERGENT TREE CIRCUITS'

PROOF.The surjectivity condition guarantees that all modules M,,! on a given level 1 can have an arbitrary input

pattern ivI applied simultaneously. We now use induction on the number of levels to show that the

identity function condition is sufficient for error

propagation. Consider the 2-level tree C(n, 2). We can

every ivl to the Output (level-')

M1~l

with K = 2""xtests. Error propagation for this module

is immediate. The n level-2 modules can have each

input pattern ivl applied simultaneously with K more

tests. If none of these n modules are faulty, then the

output values generated are all identical, and the output module M,,, will produce the identity output

value, say vl. If any single level-2 module is faulty for

any iv], the output module M,,, will produce a corresponding output value vk # vl, thereby insuring error

detection. Thus, C(n, 2) is L-testable with K tests per

level.

Assume that the p-level tree C(n, p ) is L-testable. A

( p + 1)-level tree C(n, p + 1) can be viewed as n independent copies of C(n, p ) , each of which feeds the

common output module M,,,. In order to conclude

that C(n, p + 1)is L-testable, we have to show that M1,,

can be tested and that any error resulting from testing

the C(n, p)s can be propagated to the output. The surjectivity property insures that all input patterns ivl can

be applied to M,,,, thus it can be tested. Suppose a

complete test set Tof level tests is applied to each of

the C(n, p)s, so that they always produce identical

outputs. If no module is faulty in the C(n, p ) subtrees,

then M,,, will always have identical inputs when the

subtrees are L-tested one level at a time with identical

input patterns. Consequently, the output value vl will

always be produced. If there is a single faulty module

in one of the subtrees, the output module of that subtree will produce a faulty value for at least one test

pattern, because we have assumed that the subtrees

are L-testable. The remaining n - 1 subtrees will produce a fault-free value because only one module is assumed to be faulty. Module

will receive different

inputs and indicate an error at its output. Thus, the

entire ( p + 1)-level tree C(n, p + 1) is level-testable. By

0

induction, all trees with p > 1are L-testable.

EXAMPLE6. The identity function of Fig. 11 satisfies the

conditions of Theorem 3, hence a tree constructed

from this module is level-testable. A p-level tree C(3, p )

can be level-tested with at most p . K tests, where

K = 2nnx.This is the number of tests for any tree constructed from a module that meets the conditions of

Theorem 3.

The conditions of Theorem 3 are not necessary for C(n,p)

to be L-testable. One reason why is that all C-testable convergent trees are also L-testable and, as we will see later, do

not necessarily have to be constructed from a module that

implements an identity function.

A tree circuit is C-testable for a set of faults if it can be

tested with a constant number of tests regardless of its size.

In [6], we presented necessary and sufficient conditions for

a set of faults to be C-testable in a convergent tree. Here, we

consider the case where the set of faults includes all functional faults. This generalization allows for a new characterization of convergent tree C-testability based on the

properties of the n array types found within the tree. First,

we give the necessary and sufficient conditions for Ctestability of one-dimensional arrays [B], and then restate

the conditions from [61 for C-testability for a set of faults F

in a convergent tree.

LEMMA2 181. A fault iv, + (v,,v;) is C-testable in an array if

and only if there is a sequence of module input combinations SI = (iv,, iv2, ..., ivk)where

1) the application of SI to modules 1 through k allows iv,

to be reapplied at module k + 1 and

2) the repeating sequence R*= RRR ... propagates (v,, v i )

indefinitely, where R = (iv2,iv,, ..., ivk,ivJ.

LEMMA3 [6].An n-ay p-level uncontrolled convergent tree C(n, p )

is C-testable for a set of input pattern faults F if and only if

there is a test set %(F) of constant size for each array of

type j , for 1 I j I n, that tests for a given maximal set of

faults F.

Lemma 3 allows F to include all input pattern faults,

hence it characterizes the C-testability of convergent trees

under the functional fault model.

THEOREM

4. An n-ary p-level uncontrolled convergent tree C(n,p )

is C-testable if and only if all its n array types are C-

testable.

PROOF.We begin by showing the necessity of the conditions. Assume C(n, p ) is C-testable for all input pattern

faults, but there is some fault iv, -+ (v,, v;) that is not

C-testable in some type-j array, for some 1 I j 5 n. C(n,

p ) has a single type-j array of p modules. If C(n, p ) is to

be completely C-testable and p is allowed to be arbitrarily large, there must exist a test pattern that tests a

large number of modules for the fault iv, + (v,,v;)

in the type-j array that is p modules long. Such a test

must contain a sequence of input patterns that satisfy

the conditions of Lemma 2 for array C-testability.

Therefore, all faults must be C-testable in all n array

types for the corresponding C(n, p ) to be C-testable.

We now use induction on the number of levels to

show sufficiency. If the n array types of C(n, p ) are Ctestable, then there is a finite test set %that tests every

module in array type j (1 I j In) for all functional

faults. Test set % can be partitioned into subsets of

tests, each say of size k(i), that test the array's output

module for a fault iv, + (v,,vl'). The number of test

subsets is equal to the number of input pattern faults.

In the 2-level tree C(n, 2) there are n arrays, each of

a different type. Consider some fault iv, -+ ( V ~ , V ; ) .

The array tests that test the output module of a 2module array can be applied to the n arrays of the 2level tree with k(a),tests, where k(a)]2 k(a),for all i f j

and 1 5 i, j 2 n. This can be repeated for each module

IEEE TRANSACTIONS ON COMPUTERS. VOL. 45. NO. 8, AUGUST 1996

958

---

--

c(b)

(c)

Fig. 12. Two-bit comparator module: (a) truth table, (b) X’ state-pair graph, and (c)

fault. After the application of these tests, C(n, 2) is

completely tested for all faults. Assume that the plevel tree C(n, p ) is C-testable. The tests for C(n, p ) are

array tests that can be extended to the ( p + 1)-level

modules of C(n, p + 1) as follows. Construct C(n, p + 1)

from C(n, p ) by replacing each of its p-level modules

with a copy of C(n, 2). Since C(n, 2) and C(n, p ) are

covered by the same array types, the tests for C(n, 2)

can be combined with the tests for C(n, p) in order to

test the overall (p + 1)-level tree. By the induction hypothesis, these conditions are true for all p > 1.

EXAMPLE7. The truth table for a 2-bit comparator module

taken from [71 is shown in Fig. 12a. The module comx,) and (yi-,, yJ. The

pares two 2-bit operands (x,+~,

least significant bits of the operands are applied to X’,

while the most significant bits are applied to X’.

Module outputs 00 and 11 both indicate (x,+’,x,) =

(Y,+~,

yJ, while 10 indicates (xi+’, x,) > (y,+],yJ, and 01

indicates (x,+’,x,) < (y,+’,yJ. Figs. 12b and 12c show

the state-pair graphs for the comparator module. The

X’ state-pair graph indicates that neither of the input

combinations 11 or 22 propagates any error. From

Lemma 2, we know that input pattern faults involving input combinations 11 or 22 cannot be C-testable

in arrays where X’ is the horizontal input. Hence, according to Theorem 4, a comparator constructed from

these 2-bit comparator modules cannot be C-testable.

2 state-pair graph.

x’ Y

i

00

01

02

03

10

11

12

13

20

21

22

23

30

31

32

33

0

2

3

1

2

0

1

3

3

1

0

2

1

3

2

0

Fig. 13. A module that implements a completely sensitizing function.

EXAMPLE8. The module truth table for a completely sensitizing function is shown in Fig. 13. (Each input combination iz; of a completely sensitizing function [6]

propagates any single error (vu,zlb) on any state input

X’for 1 < j 5 n.) The n = 2 array types of a tree constructed from this module are both C-testable for all

input pattern faults with K = 16 tests. Thus, a convergent tree of arbitrary size constructed from this module is C-testable with 16 tests.

BLANTON AND HAYES: TESTABILITY OF CONVERGENT TREE CIRCUITS

5 DESIGNFOR TESTABILITY

In this section, we present design methods for lowering the

number of tests required by convergent tree circuits. One

technique introduces L-testability while the other introduces C-testability. Both techniques modify a convergent

tree’s basic module by adding a single control line. The modified tree now becomes a controlled tree if it is originally uncontrolled. If the original tree is controlled, the modification

increases the width of each control bus Zl by one.

We now characterize L-testability for a controlled convergent tree CC(n, p). Let 8 ( Z , = vz) be a partial module

function that includes only input combinations that have

the control input value v,.

THEOREM

5. An n-ary p-level controlled convergent tree CC(n, p )

is L-testable if there exist control values v, and vb such that

X ( Z , = va) is surjective and X(Z, = vb) is an identity

function.

PROOF.First we consider the testability of input pattern

faults. As before, the surjective condition insures that

each input combination can be applied to every module on a given level simultaneously. Thus, we can apply all ivI to all modules in a convergent tree one level

at a time. Since there is a control value vb E & that

changes the operation of the module to an identity

function, we can apply vb to all control inputs following the tested level in order to propagate any generated error. This is the same situation encountered for

input pattern faults in the proof of Theorem 3, and the

remainder of the proof here is similar.

We show next that the given conditions are sufficient for detecting the control input stuck-at faults. If

we assume that there is only one vb E 1, such that

X(Z,= vb) is an identity function, then for each v, E 1,

959

nonidentity value being produced at

kl,l.

0

Theorem 5 shows how an arbitrary module can be altered

in order to achieve L-testability: Introduce a single control

line that changes the operation of the module from its original function to an identity function that is also surjective.

EXAMPLE9. Fig. 14 illustrates how any GP function of Fig. 6

can be modified to make it L-testable. The identity

function results from a bitwise EXCLUSIVE-OR of corresponding signal lines of the inputs X’ and X’. The

state output value 0 indicates that all applied inputs are

identical. A 2-to-1 multiplexer under the control of an

added control line Z, is used to switch operation between the GP and identity functions; XCZ, = 0) is the

GP function while k(Z, = 1) is the identity function.

Notice also that 8 ( Z , = 1) is sujective and that both

surjectivity and the identity property can always be introduced simultaneously with a single control value.

x’x‘

jt

00

01

02

03

10

11

12

13

20

21

22

23

30

31

32

33

0

1

2

3

1

0

3

2

2

3

0

1

3

2

1

0

(v,# vb)there must exist two different n-element sets

of state input values S, and S, such that

A(vb,S1) + k(vb,S2) and X(vc,S1) = X(vc,S2). The

fault z//vb can be detected by applying S1 to all but

one of the level4 modules, S, to the remaining module, v, to Z,, and vb to all control inputs Z , for k < 1. If

fault Z,/vb exists there will be a single pair of adjacent

modules that produce different output values. The

application of U b to all control inputs Z , for k < I will

cause a nonidentity value to be produced at the output module Ml,l. If Zl/vb does not exist, then the

identity value will be produced. The fault Z l / v ,

(where v, f vb) can be detected by applying Ub to all

control inputs Zkfork 5 2, with the remaining state input values applied as before. If Z J v , exists, then all

modules will produce identical values and the identity value will be produced at the output kl,l of the

(b)

Fig. 14. Level-testable GP module: (a) partial truth table X(Z, = 1)

and (b) a logic implementation.

5.1 C-Testability

Next we consider how to make a convergent tree C(n, p ) Ctestable. From Theorem 4, we know that complete Ctestability is achieved when all faults are C-testable in each

of C(n, p)’s n array types. Methods for achieving Ctestability in one-dimensional arrays are presented in [8],

[14], [17]. The method of 1141 is generalized here to an n-ary

convergent tree. We first state sufficient conditions for inmodule M,,,, i.e., at the tree’s primary output. If Z l / v c suring C-testability in the n array types of a convergent tree

does not exist, there will be a single pair of modules module, and then show how any module’s function can be

that produce different output values, and result in a modified to meet the stated conditions.

lEEE TRANSACTIONS ON COMPUTERS. VOL. 45 NO. 8, AUGUST ?996

960

hpul

THEOREM

6. An n-ay p-level uncontrolled convergent tree C(n,p )

is C-testable if all the following conditions are true for

lljln:

1) Each possible input combination iv, propagates a single

error present on each input X’.

2 ) Each state-pair graph j is strongly connected.

3) Each array type j has an input vector S , that connects

each state vk E I, in a single cycle.

4 ) Each array type j has a sensitizing vector S, = (vl, u2,

vj+l, ..., v,) suck that

...,

X(v,, v2, . . . ,

vd

=

uI,vj+,,

. . . I

vJ

X(v1,zJ2,... ,vj-p;,vj+l,

= uc

...I

XI

u1

u2

us

.. .

VN-1

VN

‘u1

v2

Input

v3

XZ

Original function

output values

PIN-l

VN

Input

f

X’

I

u,J

where v’f is any state value not equal to v:.

PROOF.In order to show that a tree constructed from a

module that satisfies the theorem’s conditions is Ctestable, we need to show that all faults of each array

type are C-testable. Consider an arbitrary fault io, +

(va,vb)for some array type j . From condition 1, we

know that each input combination propagates at least

one error present on input X’.Let (vl, vJ be the error

propagated by iv, on state input X’,and let (ua, vc)be

the resulting error at the module output. If condition

3 is satisfied, repeated application of S, will propagate

and ( u f , v i ) ,

both (va,v,) and (v,,v,) to errors (vr,v;)

,

.

respectively, where vi does not have to be same for

both errors. From condition 4, the application of S2

will propagate both errors (vf,v;) to (vc,vd). Since the

state-pair graph is strongly connected (condition 2),

(vc,vd)can be propagated to (vl,v,), the error propagated by iv, using some sequence of input combinations, say X. Now observe that the sequence of input

combinations (ina,P, P, ..., P, Q, X) (where P is the input combination formed from s, and Q is the input

combination formed from S,) satisfies the conditions

for C-testability for the fault iv, + (v,, ub) in a onedimensional array (Lemma 2). Thus, any fault in any

array type is C-testable, so each array type is Ctestable. Hence, a tree constructed from a module

satisfying all the theorem’s conditions is C-testable.

Fig. 15 shows how a binary (n = 2) convergent tree module

can be made C-testable by adding a single control line Z,. The

module output values for Z , = 1 are chosen to meet the conditions of Theorem 6. State value ul connects each vjE I, into a

single cycle in both array types (condition 3), while state values vl and v, together strongly connect both state-pair graphs

(condition2). State value v3 satisfies condition 4, where uf= v,=

v, and vd= v,. Similar modifications can be made to n-ary tree

modules. The technique is applicable only to modules that

satisfy condition 1 of Theorem 6 and have at least four state

input values, i.e., lIxl = 4. (Later, we will demonstrate how to

deal with modules that do not meet this restriction.)

(b)

Fig. 15. Achieving C-testabilityby adding a single control line 2,:partial

and (b) X(Z, = 1).

truth tables for (a) X(Z, = 0 )

A new condition must be satisfied to guarantee Ctestability in a controlled convergent tree. Modules on a

given level must have the same control value, which constrains the input combinations that can be applied to the

various arrays covering the tree. In order to meet this restriction, state value vN is used to connect each vj E I, to

itself, that is, X(1, vN,vj)= vi = g(1,vi, vN). This allows a

test for any fault in a particular array type to be arbitrarily

extended so that modules being tested for a particular fault

occur at equal distances froin the previously tested module.

Earlier we stated that this design method for Ctestability was only applicable to modules that are testable

and have at least four state input values. The module must

satisfy condition 1 of Theorem 6 because the modification

of Fig. 15 does not insure that input combinations with Z, = 0

propagate at least one error on every input X’. This problem

is easily handled by adding a new state value that makes

each input combination propagate at least one error on

every input. The existence of four state values can also be

guaranteed by adding the additional number of states required. After the module is altered, the modification of

Fig. 15 can be used to achieve C-testability.

In [ l l ] ,a method for modifying a tree module to produce C-testability is described. It introduces three new state

values that require a new state input line be added to the

module. In order to maintain the tree structure, each state

input vector X’ must have the same number of signal lines.

Thus, test input lines for an n-ary input module must be

added n at a time. Consider making the tree C(3, 4), constructed from a multiple-output module, C-testable. There

are 34-1= 27 modules on level 4 of C(3,4 ), so the method of

[ l l ]requires 3 27 = 81 extra test input lines. Our approach

requires far fewer test inputs. If the original module is assumed to satisfy condition 1 of Theorem 6, only p = 4 extra

test input lines are needed to achieve C-testability.

BLANTON AND HAYES: TESTABILITY OF CONVERGENT TREE CIRCUITS'

961

56

'41

I

+

co

Fig. 16. A 56-bii: carry-lookahead adder.

b

'42

'43

'44

'45

'45

'47

'48

962

IEEE TRANSACTIONS ON COMPUTERS. V O L 45. NO. 8, AUGUST 1996

Input

6 CASE STUDY: CARRY-LOOKAHEAD

ADDER

We now apply the design-for-testability (DFT) techniques

discussed above to the implementation of a high-speed adder based‘ on the 56-bit carry-lookahead adder of the

microprocessor [12]. For clarity, we have rearry-select ripple-carry adders of I121 by simple

ripple-carry adders. This change does not affect the testability properties of the original circuit. The adder, which is

shown in Fig. 16, is a scaled-up version of the 8-bit adder of

Fig. lb. It produces the sum of two 56-bit input operands

A = a,, u2, ..., aS6and B = b,, b,, ..., b,, using four different

module types. The gp modules produce the generate/propagate bit values g,p, from individual operand bits

a,b,. The GP modules use the set of signals g,p, - g,pI to produce group generate/propagate values G,,PiI . Carry (C)

modules use G,,P,, values and a carry input to produce a

carry output cJ that is used by the full adder (FA) modules

to compute the sum.

Becker [4] has studied the test requirements for a carrylookahead adder similar to the one in Fig. 16. Considering

only the modules’ input and output (pin) SSL faults, he

shows that the minimum number of tests required is logarithmic in N, the word size of the operands to be added.

Becker’s adder is not fully testable under the functional

fault model because the errors (2, 3) and (3, 2) from the GP

modules cannot be propagated through the C modules. If

only the detectable functional faults are considered, the

required number of tests for any similar carry-lookahead

adder becomes linear in N. The extra tests are needed to

detect functional faults in the convergent trees composed of

the GP modules. (Such faults were discussed in Section 4,

where it was shown that the fault f = 22 + (2, 3) requires a

separate test for each GP module.) The number of tests required for the GP convergent trees can be reduced by using

the GP function of Fig. 14. This makes the GP trees, as well

as the overall adder, L-testable. Because a slmilar technique

for achieving L-testability was applied to carry-lookahead

adders in I51, we focus on making the adder C-testable.

The adder of Fig. 16 is made C-testable by redesigning

the GP module. As noted earlier, any of the modules GP,,

GP,, or GP, of Fig. 6 can be used to implement the group

generate/propagate (GP) operation. The reason that all

three are valid can be understood by examining the function of the C module, which produces a carry output of 1

whenever the group generate output G,, = 1. Consequently,

the (decimal-encoded) values G,,, P,, = 2,3 are indistinguishable to the C module. (The different GP functions of

Fig. 6 were obtained by interchanging the output values 2

and 3.) The functions implemented by the g p module are

p , = a, + b, and gt = a, b,. Function pi can be replaced by a, 0b,

without altering the adder’s overall outputs, hence all input

combinations with P,, = 3 are don’t cares. This is depicted in

Fig. 17a, where don’t care outputs are marked 4.

Fig. 1% shows how the don’t care outputs of the GP

module can be defined to make both of its array types Ctestable. The resultant GP function will make a convergent

tree of GP modules C-testable. However, as a subcircuit of

the adder, the GP trees are not C-testable because the g p

module is not surjective since it cannot produce the value 3.

X’

0

0

Input

x2

0

1 0

1

0

2 3

2 4

1 2

2 0 1 2

3 4 4 4

4

4

4

(4

Input

X’

0

1

2

3

0 1 0 0 2 11

I

I

Input

x2 2 0 1 2 3

312 3 1 01

(b)

Fig. 17. (a) GP module showing the possible don’t care outputs. (b) GP

module modified for C-testability.

Also, as already stated, the C modules cannot distinguish the

values 2 and 3. We solve these two problems by adding a

single control line z,to all the gp modules, and another control line z2to all the C modules. The modified g p functions are

gi = z;. (ai , b,) + z1. ai and pi = z;. (ai 0bi) -tz1. bi, and the

modified C function is ci+l = z; . (GiZi+ qZjci-l) + z2 . P .

7 CONCLUSIONS

We have precisely characterizedthe testing coinditions for both

uncontrolled and controlled convergent trees with respect to

the functional fault model. We have also obtained conditions

for convergent trees to be testable with a test set size that is

proportional to the number of levels (L-testability) in the circuit or is constant (C-testability).DFT techmques were then

introduced that allow the modification of arbitrary modules in

order to achieve either L- or C-testability. We demonstrated

the practicality of these DFT methods by developing a Ctestable design for a carry-lookahead adder. We can apply a

similar DFT approach to other tree-like circuits found in microprocessors, such as multifunction ALUs.

ACKNOWLEDGMENT

This research was supported by the National Science Foundation under Grant Nos. MIP-9200526 and MIP-9503463,

REFERENCES

[l] J. Abraham and D. Gajski, ”Design of Testable :StructuresDefined

[21

131

[41

[51

by Simple Loops,” I E E E Trans. Computers, vol. 30, pp. 875-883,

1981.

M. Abramovici, ”Dos and Don’ts in Computing Fault Coverage,”

Proc. 1993 Int’l Test Conf., p. 594,1993.

M. Abramovici, M.A. Bi-&e, and A. D. Friedman, Digitul Systems

Testing and Testable Design. Potomac, Md.: (Computer Science

Press, 1990.

B. Becker, ”Efficient Testing of Optimal Time Adders,” IEEE

Trans. Computers, vol. 37, pp. 1,113-1,120,1988,

D. Bhattacharya and J.P. Hayes, ”Designing for High-Level Test

Generation,” IEEE Trans. Computer-Aided Design, vol. 9, pp. 752766,1990.

BLANTON AND HAYES: TESTABILITY OF CONVERGENT TREE CIRCUITS‘

161 R.S. Blanton and J.P. Hayes, ”Efficient Testing of Tree Circuits,”

Proc. 23rd Int’l Symp. Fault-Tolerant Computing, pp. 176-185, June

1993.

W.T. Cheng, ”Testing and Error Detection in Iterative Logic Arrays,” PhD thesis, Technical Report no. UILU-ENG-85-2234 CSG44, Univ. of Illinois at Urbana-Champaign, 1985.

A.D. Friedman, ”Easily Testable Iterative Systems,” IEEE Trans.

Computers, vol. 22, pp. 1,061-1,064,1973.

W.H. Kautz, ”Testing for Faults in Cellular Logic Arrays,” Proc.

Eighth Symp. Switching and Automation Theory, pp. 161-174,1967.

K.L. Kodandapani and S.C. Seth, ”On Combinational Networks

with Restricted Fanout,” lEEE Trans. Computers, vol. 27, pp. 309318,1978.

F. Lombardi and D. Sciuto, ”Constant Testability of Combinational Cellular Tree Structures,” 1. Electronic Testing: Theory and

Applications, vo1.3, pp. 139-148, May 1992.

T. Lynch and E.E. Swartzlander, “A Spanning Tree Carry Lookahead Adder,” IEEE Trans. Computers, vol. 41, pp. 931-939,1992.

P.C. Maxwell, ”Let’s Grade All the Faults,” Proc. 2993 Int’l Test

Conf., p. 595, Oct. 1993.

R. Parthasarathy and S. Reddy, “A Testable Design of Iterative

Logic Arrays,” i E E E Trans. Circuits and Systems, vof28, pp. 1,0371,045,1981.

J.M. Soden and C.F. Hawkins, ”Quality Testing Requires Quality

Thinking,” PYOC.1993 Int’l Test Conf., p. 596, Oct. 1993.

T. Sridhar and J.P. Hayes, ”Design of Easily Testable Bit-Sliced

Systems,” I E E E Trans. Computers, vel. 30, pp. 842-854,1981.

1171 c . w u and P. Cappello, “Easily Testable Iterative Logic Arrays,”

IEEE Trans. Computers, vol. 39, pp. 640-652,1990,

[I81 y . you and J.P. Hayes, ”Implementation of VLSI Self-Testing by

Regularization,” IEEE Trans. Computer-Aided Design, vel. 8, pp. 1,2611,271,1989.

963

R.D. (Shawn) Blanton (S93-M’95) received the

Bachelor’s degree in engineering from Calvin

College in 1987, a Master’s degree in electrical

engineering in 1989 from the University of Arizona, and a PhD degree in computer engineering and science from the University of Michigan,

Ann Arbor, in 1994. In 1995, he joined the Department of Electrical and Computer Engineering, Carnegie Mellon University, Pittsburgh,

Pennsylvania,where he is currently an assistant

professor. HIS research interests include the

computer-aided design of VLSl circuits and systems, fault-tolerant

computing and diagnosis, verification and testing, and computer architecture. Dr. Blanton IS a member of the IEEE.

John P. Hayes (S67-M’7O-SM’81-F85) received the BE degree from the National University of Ireland, Dublin, in 1965, and the MS and

PhD degrees from the University of Illinois, Urbana-Champaign, in 1967 and 1970, respectively, all in electrical engineering. While at the

University of Illinois, he participated in the design of the ILLIAC 111 computer. In 1970, he

joined the Operations Research Group at the

Shell Benelux Computing Center in The Hague,

the Netherlands. where he worked on mathematical programming. From 1972 to i982, Dr. Hayes was a faculty

member in the Departments of Electrical Engineering-Systems and

Computer Science at the University of Southern California, Los Angeles. Since 1982, he has been a professor in the Electrical Engineering

and Computer Science Department of the University of Michigan, Ann

Arbor. He was the founding director of the University of Michigan’s

Advanced Computer Architecture Laboratory. He was technical program chairman of the 1977 International Conference on Fault-Tolerant

Computing, Los Angeles, and the 1991 International Computer Architecture Symposium, Toronto, Canada. Dr. Hayes is the author of more

than 150 technical papers and five books, including Computer Architecture and Organization (second edition, McGraw-Hill, 1988), Layout

Minimization for CMOS Cells (Kluwer, 1992, coauthored with R.L.

Maziasz), and lntroducfion to Digifal Logic Design (Addison-Wesley,

1993). He has served as editor of various technical journals, including

the /€E€ Transactions on Parallel and Distributed Systems and the

Journal of Electronic Testing. Dr. Hayes’s current research interests

are in the areas of computer architecture; computer-aided design,

verification, and testing; VLSl design; and fault-tolerant embedded

systems. He is a fellow of the IEEE and a member of the Association

for Computing Machinery and Sigma Xi.