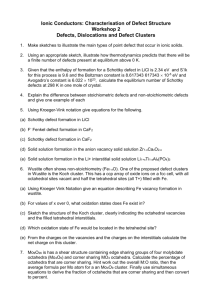

Physically-Aware Analysis of Systematic Defects in Integrated Circuits

advertisement

Physically-Aware Analysis of Systematic Defects in Integrated Circuits Wing Chiu Tam Nvidia Corporation R. D. Blanton Carnegie Mellon University diagnosis data in the context of the design layout. The Editor’s notes: methodologies developed Design-induced systematic defects are serious threats to the semiconducinclude evaluating the effector industry. This paper develops novel techniques to identify and prevent tiveness of DFM (design-forsuch defects, which facilitate to evaluate the effectiveness of DFM rules and improve the manufacturing process and design for yield enhancement. manufacturability) rules [1] VQiang Xu, City University of Hong Kong in systematic-defect prevention, identifying and understanding systematic defects h THE RELENTLESS SCALING of CMOS technolo- [2] to guide process improvement effort, formulate gies tremendously decreases device sizes and in- new DFM rules [3] or identify targets for test [4], [5], creases complexity of the resulting circuits. As more and creating a framework for fast and accurate defect and more devices are placed in the silicon real simulation [6] to validate these and other emerging estate, our ability to observe and understand defects test/yield learning methodologies (e.g., [7]). Figure 1 shows how this work addresses is diminishing. IC test, traditionally used to screen problems (shaded bubbles with associated acrofor failures for quality control purposes, now serves an added function of understanding and monitoring nyms) in a yield improvement flow in the industrial defects in the process. By diagnosing and mining the setting. Conventionally, test structures and SRAM test fail data, valuable insight can be obtained con- testing are heavily used to debug and monitor the cerning the reasons that chips fail. After the defects manufacturing process for yield learning purpose, are identified and their failure mechanisms are as shown in the left subflow of Figure 1. By understood, actions can be taken to prevent their analyzing test-structure data and SRAM test results, future occurrence to improve yield. In addition, the fabrication process can be characterized to specific tests can be generated to screen for these improve design, test and yield. Unfortunately, both SRAM (being highly regular) and test structures defects to improve product quality. This paper addresses the problem of information (being limited in volume) cannot capture all layout extraction from volume diagnosis data in order to geometries. Therefore, increasing attention has provide feedback to the designers for product yield been turned to the analysis of IC failure data to improvement. More specifically, this work tackles supplement the yield learning process, as shown in issues in this area by performing analysis of IC the right subflow of Figure 1. Here the failure data can be either generated by simulation or gathered from the real fabrication facilities. The advantage of Digital Object Identifier 10.1109/MDT.2012.2211093 having virtual failure data is that the defect Date of publication: 02 August 2012; date of current version: characteristics are known, which enables evalua23 October 2012. tion and debugging of the follow-on methodologies. September/October 2012 Copublished by the IEEE CEDA, IEEE CASS, IEEE SSCS, and TTTC 0740-7475/12/$31.00 B 2012 IEEE 81 © 2012 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works. ITC Special Section DFM rule evaluation In this section, the methodology for DFM rule evaluation is described. Background and related work DFM (design for manufacturability) refers to a wide spectrum of activities that are performed on the design prior to manufacturing in order to improve yield. DFM is necessary in nanoscale technology because of the formidable challenges encountered in manufacturing. To have acceptable yield, potential manufacturing difficulties must be anticipated Figure 1. Yield-improvement flow developed in this work. and then remedied using appropriate design compensations. One approach is to Using the failure data, the effectiveness of the DFM remove/reduce the offending layout features that rules for systematic-defect prevention can be are susceptible to failures. To achieve this goal, evaluated, which allows designers to prioritize these features must be communicated to the future DFM rule adherence. Despite tremendous designers. The common approach is to use DFM DFM effort, systematic defects still can occur [8], rules. DFM rules are very similar to regular design [9]. Therefore, failure data should be analyzed for rules, except that many of them are often not identifying systematic defects as well. For any strictly enforced. This is because the cost-benefit systematic defects that are confirmed to signifi- tradeoff for adhering/violating a particular rule is cantly affect yield, new DFM rules can be formu- not well understood [11]. This prevents designers lated to prevent occurrence of the offending layout from reaping the full benefit of DFM. Prior work [4], features in future designs, a technique which [9], [12], [13] in this area focuses on identifying or augments DFM rule generation based on test testing for systematic issues, our work focuses on understanding the economic benefit of applying a structures [10]. The rest of the paper is organized as follows: DFM particular set of DFM rules and ranking them rule evaluation describes our DFM rule evaluation according to their relative contribution to yield methodology that we call Rule Assessment of enhancement. Defect-Affected Regions (RADAR). This is followed by a description of our approach for systematic Approach and uniqueness defect identification that we call Layout Analysis for To achieve this goal, a methodology (called Systematic Identification using Clustering (LASIC) in RADARVRule Assessment of Defect-Affected ReSystematic defect Identification. In Mixed-signal gions) has been developed to evaluate DFM rules defect simulation, we describe the defect simu- using diagnosis-implicated regions of failed ICs [1]. lation framework Simulation of Layout-Injected Figure 2 shows the flow diagram of the RADAR Defects for Electrical Responses (SLIDER) which is methodology. The flow starts with diagnosing a large used to generate populations of virtual failure data. number of IC failures. This diagnosis-driven apHere we use SLIDER-generated data to evaluate proach is substantially different from traditional LASIC and RADAR. Finally, this work is summarized approach in which test structures are used to evalin Summary. uate DFM rules [14], [15]. The outcome of diagnosis 82 IEEE Design & Test of Computers is a set of suspect signal lines or cells where the defect is believed to reside. The corresponding area in the layout is examined to collect measures of effectiveness (i.e., the number of times a rule is violated/adhered) for each DFM rule of interest. In addition, for control purposes, the nets for the rest of the circuit, where failure does not occur, are sampled and examined in the same way. Using the information collected, statistical analysis is then performed to determine: 1) if there is strong evidence to indicate that the violation of a DFM rule is associated with the observed failures; 2) which rule is more important in terms of their ability to prevent failures (e.g., if violations of rule A cause more failures than violations of rule B, then rule A is more important than rule B); and 3) the amount of yield loss that would be recovered if a certain percentage of violations of a specific rule is corrected. To detect association of rule violations and yield loss, hypothesis testing is used. This technique is commonly used in the medical communities to determine if certain chemicals/activities have an effect on the health of an individual (e.g., is smoking associated with lung cancer?). To determine the relative importance of a rule, the relative risk is estimated for each rule. In the context of RADAR, relative risk is simply the ratio of the failure rate given rule violation to the failure rate given rule adherence. From the definition, it is clear that relative risk measures the increase in likelihood of failure when a rule is violated. Thus, calculating the relative risks can reveal the relative importance of each rule. Additionally, the failure rate given rule violation is also estimated for all the DFM rules of interest using an EM (expectation-maximization) approach [16], [17]. After the relative risk and failure rate given rule violation are estimated, the failure rate given rule adherence can be estimated as well since relative risk is simply a ratio of the two failure rates. Having the estimates of these two failure rates, in turn, allows the estimation of yield loss before and after addressing a certain amount of rule violations. The difference measures the resulting yield impact of addressing the violation and thus can also be used as a measure to indicate importance of a rule in a given set of rules. Results and contributions RADAR helps the designers better understand the cost-benefit tradeoff and allows them to adjust future designs to improve yield at the same technology node. Table 1 shows the result of applying RADAR to a commercial Nvidia GPU that is manufactured using a TSMC 90 nm process. The chip is nearly 9 mm 9 mm, contains over 12 million gates and 700 K flip-flops, and is tested with over 4,000 test patterns. Nearly 9,000 failing GPUs are diagnosed to generate candidates for each failure. For this experiment, via-enclosure rules (e.g., M8.ENC. 1R, M7.ENC.2R) and metal-density rules (e.g., M23. WD.4R) are evaluated. The rule names are shown in column 1. Hypothesis testing using Pearson’s 2 test (columns 2) shows that a majority of the DFM rules Figure 2. Overview of the RADAR methodology. September/October 2012 83 ITC Special Section Table 1 Summary of DFM rule evaluation results for an Nvidia GPU design. is associated with yield loss. (A green entry in column 2 denotes association while a red entry denotes independence). The associated p-values (i.e., the probability of observing more extreme data than the current one) are shown in column 3. Both relative risk and yield impact are then calculated for each rule, which are shown in columns 4 and 5, respectively. The rules have been sorted in decreasing order of relative risk. The order shows that contact enclosure rules are more effective than density rules. This suggests that via issues may cause more yield loss than planarity/density problems for this particular process/design. It is also clear from columns 4 and 5 that the ordering of yield impact for a given set of rules is not the same as the ordering of relative risk. This is expected because yield impact takes into account the amount of rule violations specific to a design while relative risk does not. In practice, the number of rules of interest can be much more than what is used in this experiment and will include frontend rules as well. This experiment setup thus reduces the generality of the results. However, it should be emphasized that this is not a limitation of RADAR itself. Rather, this issue arises due to the unavailability of rules and failure data because of their confidential nature. Systematic defect identification In this section, the methodology for systematic defect identification is described. 84 Background and related work Defects inevitably occur in a semiconductor manufacturing process and can be classified into two categories, namely random and systematic defects. The former arise because of random contamination particles that affect the structure of a circuit, thus altering its functionality. In contrast, systematic defects happen because of design-process interactions, i.e., part of the design is sensitive to manufacturing in certain process corners and has an increased likelihood of failure. Unlike random defects, systematic defects can happen repeatedly in places with similar layout geometries. Identification of systematic defects immediately leads to yield improvement. Since systematic defects are becoming a significant source of failures in nanoscale technologies, the need to identify them becomes more important than ever. In the last several years, there has been a growing amount of work on systematic defect identification. In [12], [18], [19], expected failure rates are computed for layout features/nets. This information is combined with volume diagnosis data to identify outliers (i.e., systematic defects). Work in [20] applies clustering techniques to test-response data collected from a large number of failing ICs to identify common failure signatures. Last, the work described in [21], [22] performs extensive lithography simulation on the entire layout to identify hotspots. Layout snippets containing these hotspots are extracted and clustered to form DFM rules. The aforementioned work has the goal of identifying systematic defects, and undeniably, they have a certain degree of success, as evidenced by experiment results. Unfortunately, past approaches [12], [18]–[20] fall short of automatically extracting similar layout features that may underlie many of the failures. The work in [21], [22], while capable of automatic layout feature extraction, relies entirely on simulation, which is known to be inaccurate and too conservative. Relying on simulation alone also means that no systematic defects are identified for failing mechanisms that are not modeled. Approach and uniqueness To identify systematic defects, a diagnosis-driven methodology (called LASIC) is developed [2]. The LASIC flow is illustrated in Figure 3. LASIC uses the following four steps: 1) volume diagnosis; 2) layoutsnippet extraction; 3) snippet clustering; and 4) defect IEEE Design & Test of Computers validation. Similar to the RADAR flow, LASIC starts by applying diagnosis to a large sample of chips, or is continually applied to failures. The outcome of diagnosis is a set of suspect signal lines or cells where the defect is believed to reside. Snippet images are then extracted from the corresponding layout region for each suspect. Clustering, such as K-means, is then applied to group similar snippet images together for identifying any commonalities. (To speed Figure 3. Overview of the LASIC methodology. up the clustering process, the snippet images are represented using discrete cosine transform (DCT) so that only The layout snippets that correspond to the snipthe dominant DCT coefficients are used in the pet images are fed to Optissimo for lithography clustering process.) Layout features identified by simulation. Figure 5 shows an example of a LASIC can then be analyzed using a process lithography-induced hot spot (i.e., insufficient consimulator (such as the lithography tool Optissimo tact coverage) identified by Optissimo. There are [23]) to confirm the existence of a systematic defect, altogether 20 hotspots identified in the metal-1 layer. and/or physically analyzed using Physical Failure If these hotspots are confirmed to cause significant Analysis (PFA). yield loss, then DFM rules can be formulated to preIn contrast to [12], [18]–[20], LASIC identifies vent their future occurrence. For example, the insufproblematic layout features automatically. In addi- ficient coverage of the contact in Figure 5 can be tion, since the methodology analyzes real IC failures, resolved by increasing the metal-1-to-contact encloit does not suffer from the false negatives that may sure requirement. plague the approaches described in [21], [22]. Mixed-signal defect simulation Results and contributions The methodology has been implemented and tested on two industrial data. Specifically, two commercial designs, namely a LSI testchip in 130 nm technology and an Nvidia graphic processing unit (GPU) in 90 nm technology, with real failure data are used to validate the methodology. Figure 4 shows example images from two different metal-1 clusters after LASIC has been applied. Figure 4a shows four snippet images from a cluster in metal-1, while Figure 4b shows four snippet images from another metal-1 cluster. Figure 4 shows that geometries in the same cluster resemble each other but are not exactly the same while geometries in different clusters exhibit substantial differences. This example clearly demonstrates that LASIC is able to extract from diagnosis data images that have similar layout features. September/October 2012 In this section, the methodology for mixed-signal defect simulation is described. Figure 4. Illustration of clustered snippet images: (a) from one cluster and (b) a second cluster. 85 ITC Special Section Figure 5. Illustration of a hotspot identified using lithography simulation. Background and related work All test-fail driven yield/test learning methodologies should be validated to ensure their correctness. Unfortunately, this is easier said than done because of unavailability of test fail data and the corresponding PFA data, which are often foundry confidential. To circumvent this difficulty, the concept of virtual failure data creation was proposed in [24]. The idea is to simulate failures by injecting faults/defects in the circuit. The virtual data generated can then be used to evaluate the effectiveness and accuracy of the yield/test learning methodology under investigation. This approach also has the advantage that the ‘‘correct’’ answer (i.e., the injected defect) is known and can be precisely controlled and thus it enables debugging and refinement of the methodology under evaluation. Figure 6. Block diagram of the SLIDER framework. 86 Approach and uniqueness While previous work (e.g., [24]–[27]) has considered this topic before, the innovation here centers on three aspects: i) accuracy resulting from defect injection taking place at the layout level; ii) speedup resulting from careful and automatic partitioning of the circuit into digital and analog domains for mixed-signal simulation; and iii) complete automation that involves defect injection, design partitioning, netlist extraction, mixed-signal simulation, and test-data extraction [6]. The defect simulation framework developed is called SLIDER. Figure 6 shows the key components of SLIDER. It is composed of an analog block generator (ABG), a digital block generator (DBG), a mixed-signal simulator (MSS), and a result parser (RP). The blocks in pink are implemented in SLIDER. The MSS used in SLIDER is Cadence AMS designer [28], [29]; however, any other mixed-signal simulator can be easily used instead. The inputs to the framework are the design database, a description of the defects to be injected into the layout or a set of options to direct the defect generation process, and test patterns. The design database must contain both the layout and the logiclevel netlist. The defect description specifies the geometry of one or more defects (i.e., coordinates, size, polygon, layer, etc.). If the defect description is not specified, then options must be specified to direct the defect generation process. The supported defect types include: open, resistive via, signal bridge, supply bridge, and various kinds of cell defects that include the ‘‘nasty polysilicon defect’’ [30], transistor stuckopen, and transistor stuckclosed. The test patterns mimic the tester stimulus that would be applied to the circuit during production testing. Using these inputs, SLIDER starts by automatically partitioning the design into its respective analog and digital blocks, which is accomplished by ABG and DBG, respectively. The analog block contains all the cell instances and nets that are required to produce accurate circuit-level simulation of defect behavior, while the digital block IEEE Design & Test of Computers contains everything that remains. Defects are then injected into the analog block at the layout level. The modified layout is then extracted to produce the circuit-level netlist of the analog block. The analog block, the digital block, and their connections form the design under test (DUT), as illustrated in blue in Figure 6. A transient analysis is then performed on the DUT by the MSS using the test patterns as inputs. To capture the DUT’s response, RP samples the output waveform at the frequency defined by the test clock. During simulation, the MSS automatically takes care of the cross-domain signals through the use of connection modules [29], an analog-to-digital (digital-to-analog) convertor for a signal that crosses from the analog (digital) domain to the digital (analog) domain. Besides allowing the users to directly specify the defects directly, SLIDER supports several defectgeneration modes, as shown in Figure 7. SLIDER can generate defects that mimic random contaminations that follow a defect density and size distribution (DDSD) (Figure 7a). SLIDER can also generate systematic defects that share a common layout pattern (Figure 7b). In this mode, SLIDER provides a layout pattern (which can be user-defined or automatically generated) to a commercial pattern matching tool [31] to find all locations that mimic the given pattern. The identified locations then serve as defect injection sites as illustrated in Figure 7b. Finally, Figure 7c illustrates the third mode of SLIDER. This mode allows the user to explore different defectinjection scenarios at a given location for improving diagnosis. Results and contributions Because of the scalability enhancement, SLIDER can be applied in other settings that include diagnosis resolution improvement, defect localization, and fault model evaluation. Three set of experiments are performed to demonstrate scalability and usage of SLIDER. Run-time experiment. First, a run-time experiment is performed. Specifically, eleven benchmark circuits are placed-and-routed using Cadence Encounter. For each circuit, 100 random defects are layout-injected and simulated. The results are averaged and summarized in Figure 8. Figure 8a compares the total number of gates and the number of gates in the analog block for each circuit. It is clear that the size of the analog block does not scale, even when the circuit size increases tremendously. This property provides the basis for the scalability of SLIDER, i.e., the amount of effort needed for circuitlevel simulation remains relatively constant. Figure 8b shows the total runtime normalized by the pattern count. It is clear that the normalized runtime is in the order of seconds for all the benchmark circuits. Last, Figure 8c shows that SLIDER adds a negligible Figure 7. Three defect generation modes are supported in SLIDER that include: (a) random; (b) systematic; and (c) diagnostic. September/October 2012 87 ITC Special Section Figure 8. Runtime results that demonstrate the scalability of the SLIDER framework. overhead to the total runtime, which is dominated by the simulation time. LASIC evaluation. In the second experiment, the accuracy of LASIC is evaluated using the virtual failure data generated by SLIDER. Specifically, two failure populations, each of size 100 are generated for both random and systematic defects, using DDSD and systematic defect generation modes of SLIDER, respectively. The failures are then randomly sampled from both populations to form a single population. This process is repeated to get failure populations with different proportions of random and systematic defects. The goal is to evaluate how much random ‘‘noise’’ can be tolerated by LASIC. The experiment is performed using eight ISCAS benchmarks. Four types of defects are injected into these benchmarks: metal-2 bridge, metal-2 open, metal-3 bridge, and metal-3 open. The result is averaged over the eight benchmarks. In addition, to isolate the ‘‘noise’’ that occurs due to inaccuracies/ ambiguities in diagnosis, this experiment is performed for two scenarios: ideal and actual diagnosis. Ideal diagnosis means that diagnosis correctly pinpoints the faulty line with no ambiguity while 88 real diagnosis can be inaccurate (i.e., omitting the defect completely) or low in resolution (i.e., additional suspects are reported along with the actual defect location). Comparing the two scenarios provides insight about how LASIC performs under various scenarios. After applying LASIC to the virtual data, clusters of layout images of the suspect net are generated. The cluster that contains the underlying pattern of the injected systematic defects is called the correct cluster. For each scenario, the averaged rank of the correct cluster is plotted against the percentage of systematic defects injected. The data is summarized in Figure 9 for both ideal and real diagnoses. It is clear from Figure 9 that the average rank of the correct cluster improves (a smaller numeric value of the rank indicates that the cluster is ranked higher) as the percentage of systematic defects increases for both ideal and real diagnoses. This result is expected because the size of the correct cluster should increase as the number of systematic defects present increases. It is also evident that the technique is effective in both ideal and real diagnoses because the correct cluster is present in the top 40 ranked clusters (top 3%) even when the IEEE Design & Test of Computers population only consists of 20% systematic defects. As expected, performance of LASIC is worse for actual diagnosis due to inaccuracies/ambiguities in diagnosis. To mimic how LASIC should be used in practice, another experiment involving multiple systematic sources of defects and random defects are also performed. Specifically, five different systematic populations are generated to mimic the presence of five different sys- Figure 9. LASIC tematic issues for each benchmark circuit. The random population is also included to mimic the presence of random defects. The defects from these populations are randomly sampled and mixed in different proportions. Table 2 summarizes the amount of sampling from each population for each scenario (40 systematic defects are sampled from the ‘‘Systematic 2’’ population under the linear scenario, for example). The same sampling procedure is performed for each benchmark circuit. Four different scenarios are considered in this experiment that includes: 1) ‘‘Equal’’ (column 2) where the number of defects from each systematic population is equal; 2) ‘‘Linear’’ (column 3) where the number of defects is linearly decreasing for each systematic population; 3) ‘‘Dom1’’ (column 4) where one systematic population contributes substantially more defects than the rest; and 4) ‘‘Dom2’’ (column 5) where two of the systematic populations contribute substantially more defects than the rest. In each scenario, 70 random defects are included to mimic the presence of random defects (row 7 of Table 2). LASIC is applied to each of the four scenarios for each benchmark circuit. Here, the goal is to evaluate whether LASIC is able to identify all five systematic defect types. Therefore, the number of systematic issues correctly identified is plotted against the number of top-ranked clusters considered, which is varied from 5 to 55. In contrast to the previous experiment, only real diagnosis is used in this experiment in order to mimic how LASIC would be deployed in practice. Again, the experiment is repeated four times to inject four types of defects into September/October 2012 evaluation for (a) ideal and (b) real diagnoses. the benchmark circuits: metal-2 bridge, metal-3 bridge, metal-2 open, and metal-3 open. The results for each of the four defect types are averaged over the eight circuits and are shown in Figure 10a–d. It is clear from Figure 10 that the number of systematic issues correctly identified increases rapidly to the ideal value of five as the number of top-ranked clusters considered increases. As demonstrated in Figure 10, LASIC is able to identify over 90% (i.e., 4.5/5.0) systematic defects in the top 55 clusters for all defect types considered under all four scenarios. The results clearly show that LASIC is effective even when there are multiple systematicdefect types and random defects present. RADAR evaluation. In the third experiment, the accuracy of RADAR is evaluated using the SLIDERgenerated virtual failure data. A set of eight virtual DFM rules is handcrafted. In addition, for the evaluation of each DFM rule, two patterns are defined, namely the adherence pattern and the Table 2 Multiple systematic defect creation for LASIC evaluation. 89 ITC Special Section Figure 10. LASIC evaluation for multiple systematic defects for: (a) metal-2 bridge; (b) metal-3 bridge; (c) metal-2 open; and (d) metal-3 open. Figure 11. Hypothesis testing evaluation showing the trend for each DFM rule in terms of: (a) statistic T in Pearson 2 test and (b) the relative risk when the amount of violated-rule failures varies. 90 violation pattern. The adherence pattern defines the scenario when the rule is adhered, while the violation pattern defines the scenario when the rule is violated (i.e., the rule itself). Both patterns have to be defined for virtual failures to be created in both scenarios. Similar to the LASIC experiment, two failure populations, each of size 100, are generated for both adherence and violation patterns for each rule, using the systematic-defect generation mode of SLIDER. Again, the failures are then randomly sampled from both populations to form a single population. This process is repeated to generate failure populations with a different proportion of adherence and violation patterns. The goal is to evaluate how the statistic used in hypothesis testing and the relative risk change as the proportion of violated-rule defects varies. Seven ISCAS designs are used in the evaluation. The results are averaged over the designs. To examine how the effectiveness of RADAR changes as the amount of violated-rule failures varies, the statistic T (for Pearson 2 test) and the relative risk are plotted against the percentage of violated-rule failures in the failure population, as shown in Figure 11a and b, respectively. Figure 11a clearly shows that, as the percentage of violated-rule failures increases, the statistic T increases, indicating the increasing association of rule violations and failures, as expected. The associated p-value (not shown in Figure 11) also decreases, indicating the increasing confidence that the IEEE Design & Test of Computers association is valid. Figure 11b Table 3 Multiple violated-rule failures creation for RADAR evaluation. shows that the relative risk increases as the amount of violated-rule failure increases, which indicates that the failure rate given violation is increasingly higher than the failure rate given adherence, as expected. Similar to LASIC evaluation, another experiment involving different violated-rule failures is performed to evaluate the accuracy of the rule known, the exact yield impact can be evaluated to ranking. Using a similar experiment setup, several provide the ‘‘golden’’ reference point for comparison. different sets of virtual failure populations are Again, the results are averaged over the seven created and summarized in Table 3. Each row benchmark circuits used in this experiment. Figure 12 shows the results in the form of a norcorresponds to a scenario while each column specifies the number of injected rule-violation malized bar chart for the yield impact. Each bar in failures. For example, in the ‘‘Linear’’ scenario, 90 Figure 12 has a label in the y axis that consists of two violated-rule failures are selected for rule 1, 80 parts, namely the scenario and the data source. The failures are selected for rule 2, etc. In addition, there scenario refers to one of the failure scenarios defined are 80 adhered-rule failures (ten for each of the eight in Table 3 while the data source can be ‘‘golden,’’ rules) for each scenario. The adhered-rule failures ‘‘ideal diagnosis,’’ and ‘‘real diagnosis.’’ Figure 12 are labeled as unknown because in the estimation shows that the yield impact, agrees very well with the of Pk ðLjR 0 Þ, only rule-violations found in failing actual data for both ideal and real diagnosis. The layout regions are considered. The adhered-rule percentage error (i.e., the absolute difference failures instead of random failures are included to between the estimate value and the actual value ensure a nonzero entry in the adherence count, divided by the actual value) are 18.61% and 26.44% which is necessary for relative risk estimation. In this for ideal and real diagnoses, respectively. The experiment, five scenarios are considered and defined in a similar manner as in the case of LASIC evaluation experiment. Since failures due to different rule violations exist in the same population, diagnosis accuracy and resolution become very important. (A misdiagnosed candidate can lead to a rule violation being incorrectly attributed as the cause, for example.) To isolate the ‘‘noise’’ that can happen due to inaccuracies/ambiguities in diagnosis, this experiment is performed under two controls: ideal diagnosis and real diagnosis, which are defined in the same manner as the LASIC evaluation experiment. Since the exact numbers of violated-rule Figure 12. Rule ranking evaluation in terms of yield impact under and adhered-rule failures are five different failure scenarios. September/October 2012 91 ITC Special Section accuracy of yield impact is expectedly worse in the real-diagnosis scenario than in the ideal-diagnosis scenario because of the diagnosis inaccuracy. As a side note, the initial results were different from what are shown Figures 10 and 12 when LASIC and RADAR were first evaluated. Bugs were discovered and both techniques were improved. This would be difficult without the use of the virtual failure data generated by SLIDER. [8] B. Kruseman et al. ‘‘Systematic defects in deep sub-micron technologies,’’ in Int. Test Conf., 2004, pp. 290–299. [9] R. Turakhia et al. ‘‘Bridging DFM analysis and volume diagnostics for yield learningVA case study,’’ in Proc. IEEE VLSI Test Symp., 2009, pp. 167–172. [10] C. Tabery et al. ‘‘Process window and device variations evaluation using array-based characterization circuits,’’ in Proc. Int. Symp. Quality Electron. Des., THIS WORK DESCRIBES a comprehensive methodology that addresses the prevention and identification of systematic defects. Particularly, RADAR measures the effectiveness of the DFM rules in systematic defect prevention, and therefore enables designer to prioritize DFM rule adherence in future designs. Identification of systematic defects using LASIC enables an understanding of the systematic issues for improving the process and the design. The SLIDER framework enables fast and accurate defect simulation so that virtual failure data can be created to evaluate test/yield learning methodologies. 2006, pp. 6–265. [11] M. Nowak and R. Radojcic, ‘‘Are there economic benefits in DFM?’’ in Proc. Des. Automat. Conf., 2005, pp. 767–768. [12] J. Jahangiri and D. Abercrombie, ‘‘Value-added defect testing techniques,’’ IEEE Des. Test of Comput., vol. 22, no. 3, pp. 224–231, 2005. [13] K. Dongok et al. ‘‘Defect diagnosis based on DFM guidelines,’’ in Proc. IEEE VLSI Test Symp., 2010, pp. 206–211. [14] A. A. Kagalwalla et al. ‘‘Design-of-experiments based design rule optimization,’’ in Proc. SPIE, 2012, pp. 832709-8. Acknowledgment The authors would like to thank Mr. Bruce Cory from Nvidia for providing the GPU design and failure data, and the LSI Corporation for providing design and failure data. [15] Y. Zhang et al. ‘‘32 nm design rule and process exploration flow,’’ in Proc. SPIE, 2008, pp. 71223Z-12. [16] B. Benware et al. ‘‘Determining a failure root cause distribution from a population of layout-aware scan diagnosis results,’’ IEEE Des. Test of Comput. vol. 29, no. 1, pp. 8–18, 2012. [17] C. M. Bishop, ‘‘Mixture models and EM,’’ in Pattern h References [1] W. C. Tam and R. D. Blanton, ‘‘To DFM or not to DFM?’’ in Proc. Des. Automat. Conf., 2011. [2] W. C. Tam, O. Poku, and R. D. Blanton, ‘‘Systematic defect identification through layout snippet clustering,’’ in Proc. Int. Test Conf., 2010, pp. 13.2. [3] W. C. Tam, O. Poku, and R. D. Blanton, ‘‘Automatic DFM rule discovery through layout snippet clustering,’’ in Proc. Int. Workshop on Des. Manufacturabil. Yield, 2010. [4] K. Dongok et al. ‘‘Testing for systematic defects based on DFM guidelines,’’ in Proc. Int. Test Conf., 2007, pp. 1–10. [5] X. Yu et al. ‘‘Controlling DPPM through volume diagnosis,’’ in Proc. IEEE VLSI Test Symp., 2009, pp. 134–139. [6] W. C. Tam and R. D. Blanton, ‘‘SLIDER: A fast and New York: Springer-Verlag, 2006, pp. 423–460. [18] K. Martin et al. ‘‘A rapid yield learning flow based on production integrated layout-aware diagnosis,’’ in Proc. Int. Test Conf., 2006, pp. 1–10. [19] M. Sharma et al. ‘‘Efficiently performing yield enhancements by identifying dominant physical root cause from test fail data,’’ in Proc. Int. Test Conf., 2008, pp. 1–9. [20] L. M. Huisman, M. Kassab, and L. Pastel, ‘‘Data mining integrated circuit fails with fail commonalities,’’ in Proc. Int. Test Conf., 2004, pp. 661–668. [21] J. Ghan et al. ‘‘Clustering and pattern matching for an automatic hotspot classification and detection system,’’ in Proc. SPIE, 2009, pp. 727516-11. [22] N. Ma et al. ‘‘Automatic hotspot classification using accurate defect simulation framework,’’ in Proc. IEEE pattern-based clustering,’’ in Proc. SPIE, 2008, VLSI Test Symp., 2011, pp. 172–177. pp. 692505-10. [7] Y.-T. Lin et al. ‘‘Physically-aware N-detect test pattern selection,’’ Des. Autom. Test Eur., pp. 634–639, 2008. 92 Recognition and Machine Learning, 1st ed. [23] The Optissimo User Manual, 6.0 ed. San Jose, CA: PDF Solutions Inc., 2001. IEEE Design & Test of Computers [24] T. Vogels et al. ‘‘Benchmarking diagnosis algorithms with a diverse set of IC deformations,’’ in Proc. Int. Test Conf., 2004, pp. 508–517. [25] A. Jee and F. J. Ferguson, ‘‘Carafe: An inductive fault analysis tool for CMOS VLSI circuits,’’ in Proc. IEEE VLSI Test Symp., 1993, pp. 92–98. Wing Chiu (Jason) Tam is a senior hardware engineer with Nvidia Corporation working on inhouse DFT tools development. His research interests are in the areas of CAD for design for manufacturing and IC testing. He is a student member of the IEEE and ACM. [26] W. Meyer and R. Camposano, ‘‘Fast hierarchical multi-level fault simulation of sequential circuits with switch-level accuracy,’’ in Proc. Des. Automat. Conf., 1993, pp. 515–519. [27] W. C. Tam, O. Poku, and R. D. Blanton, ‘‘Automated failure population creation for validating integrated circuit diagnosis methods,’’ in Proc. Des. Automat. Conf., 2009, pp. 708–713. [28] The Virtuoso AMS Designer Environment User Guide. San Jose, CA: Cadence Design Systems Inc., 2009. R. D. (Shawn) Blanton is a professor of electrical and computer engineering at Carnegie Mellon University, Pittsburgh, PA, where he also serves as a Director at the Center for Silicon System Implementation, and leader of the Advanced Chip Testing Laboratory (ACTL). His research interests include test and diagnosis of integrated heterogeneous systems. [29] K. Kundert and O. Zinke, The Designer’s Guide to Verilog-AMS, 1st ed. New York: Springer, 2004. [30] R. D. Blanton et al. ‘‘Fault tuples in diagnosis of deep-submicron circuits,’’ in Proc. Int. Test Conf., 2002, pp. 233–241. [31] The Calibre Pattern Matching User Manual, 1.0 ed. Wilsonville, OR: Mentor Graphics Corporation, 2010. September/October 2012 h Direct questions and comments about this article to Wing Chiu Tam, Nvidia Corporation, Nvidia Corporation Building D, 2701 San Tomas Expressway, Santa Clara, CA 95050; phone (408)-486-4981; jtam@nvidia.com. 93