Computer Architecture Instructor: CSE 5381/7381

advertisement

CSE 5381/7381

Computer Architecture

Instructor:

Prof. Peter-M. Seidel

CSE 5381/7381

Computer Architecture

Spring 2007

1

Structure

I.

Introduction

II.

Quantitative Methods

III. ISA Interface & Simple Architectural Choices

IV. Interrupt Handling

V.

Floating-Point & Extended Instruction Sets

VI. Advanced Pipelining & ILP

VII. Memory System Design

VIII. Multiprocessing

CSE 5381/7381 Computer Architecture

Spring 2007

2

IV. Interrupt Handling

CSE 5381/7381

Computer Architecture

Spring 2007

3

Why Interrupts ?

Is there anything that MIPS ISA (48 instructions) can not compute?

What are Interrupts?

In which situations are Interrupts used/do they occur?

Could these situations be handled without interrupts?

CSE 5381/7381 Computer Architecture

Spring 2007

4

Interrupts

Interrupts are events that change the control flow of the program

other than branch instructions

Triggered by event signals ev(j) for j=0,1,2,3…

index j

0

1

2

3

4

5

6

6+I

name

reset

illegal instruction

misaligned memory access

page fault on fetch

page fault on load/store

trap

arithmetic overflow

external I/O

symbol

reset

ill

mal

pff

pfls

trap

ovf

exi

Activation of event signal ev(j) results in procedure call of exception

handler routine (or ISR) H(j)

Takes care of the problem signaled by ev(j)

CSE 5381/7381 Computer Architecture

Spring 2007

5

Interrupts

Types of interrupts:

• Internal interrupts versus External interrupts

– internal interrupts are generated by CPU or memory system

• Maskable versus Non-maskable interrupts

– maskable interrupts can be ignored under software control

• After interrupt of instruction I the program can be resumed in

three ways:

– repeat instruction I

– continue with instruction I+ which would follow I in the uninterrupted

execution of the program

– abort the program

CSE 5381/7381 Computer Architecture

Spring 2007

6

Interrupts

Classification of interrupts:

index j

0

1

2

3

4

5

6

6+I

symbol

reset

ill

mal

pff

pfls

trap

ovf

exi

external

yes

no

no

no

no

no

no

yes

maskable

no

no

no

no

no

no

no

yes

resume

abort

abort

abort

repeat

repeat

continue

continue/abort

continue

Priorities due to their index:

– the lower the index the higher the priority of the interrupt

– only an ev(j) with higher priority j<j’ can interrupt handler H(j’)

CSE 5381/7381 Computer Architecture

Spring 2007

7

Interrupts

Definition based on pipelined DLX design

– procedure call of ISR H(j) based on event ev(j)

– define SISR to be start address of ISR H(j)

– resume (previous table) with machine configuration before interrupt

restored

Additional requirements:

– extension of DLX machine language (handout MP p.178)

– Mechanism to collect return addresses and parameters

– Mechanism capable of forcing the address (SISR) into (PC)

CSE 5381/7381 Computer Architecture

Spring 2007

8

Interrupts

Extension of Instruction set Architecture:

–

–

–

–

ISA specification in Table 5.4 on page 178

Addition and subtraction instructions are extended to signal overflows

additional special move instructions: movs2i, movi2s

Additional control instructions: trap, rfe

Interrupt convention

– The active event line ev(j) of an external interrupt is only turned off once

interrupt j received service

– Interrupt j receives service as soon as the ISR is started with interrupt

level j’ with j’=j or (j’<j and interrupt j’ is of type abort)

CSE 5381/7381 Computer Architecture

Spring 2007

9

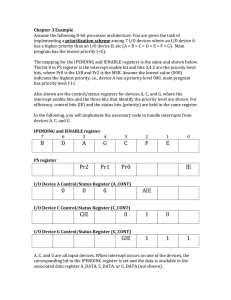

Hardware Extension I - Cause Register

Cause register (non-visible to the user):

– catches event signals ev[j] which become active during execution

of instruction Ii

• If j is an internal interrupt, it is caught in the same instruction, i.e.

CA[j]i = 1

• If j is an internal interrupt, it is caught in the same or next

instruction, i.e.

CA[j]i = 1

CA[j]i+1 = 1

CA[j] stays active until interrupt j receives service.

In any other situation

OR

CA[j]i = 0.

CSE 5381/7381 Computer Architecture

Spring 2007

10

Interrupts

Hardware extensions:

– Additional Cause register CA non-visible to assembler programmer

• Used for catching events ev[j]

– DLX architecture extended by 7 new registers, 6 visible to the assemble

programmer -> SPR [5:0] of new special purpose register SPR

address

0

1

2

3

4

5

name

SR

ESR

ECA

EPC

EDPC

Edata

meaning

status register

exception status register

exception cause register

the exception PC

the exception delayed PC

exception data register

– Content can be copied between GPR and SPR by special move instructions

move i2s and moves2i

CSE 5381/7381 Computer Architecture

Spring 2007

11

Interrupts - Masking

Interrupt masks stored in the status register SR

– For maskable interrupts j, bit SR[j] stores the mask of interrupt j:

• SR[j]=0 --> interrupt j is disabled (masked)

• SR[j]=1 --> interrupt j is enabled (unmasked)

Masked Cause Register MCA derived from cause register CA and

status register SR:

CA[ j ]i

MCA[ j ]i =

CA[ j ]i ∧ SR[ j ]i −1

if interrupt j non-maskable

if interrupt j is maskable

! Causes from Ii are masked with masks valid after instruction Ii-1

CSE 5381/7381 Computer Architecture

Spring 2007

12

Interrupts - Jump to ISR

Jump to the interrupt service routine ISR:

generation of signal JISR (jump to interrupt service routine):

31

JISRi = ∨MCA[ j ]

j =0

Activation of signal JISRj =1 triggers jump to interrupt service routine

Interrupt service routine is treated as part of instruction Ij

There are different register values to consider for each register X

– Xi : value of register X after (interrupted) execution of instruction Ij

– Xi” : value of register X after (uninterrupted) execution of instruction Ij

CSE 5381/7381 Computer Architecture

Spring 2007

13

Interrupts - Jump to ISR (Cont’d)

Jump to the interrupt service routine ISR:

Effect of JISR for instruction Ij :

choose caught, non-masked interrupt with highest priority:

ili = min { j MCA[ j ]i = 1}

effect depends on type of chosen interrupt (can be continue, repeat

or abort) on registers:

X i −1 if ili is of type repeat

Xi =

X i " otherwise

on program counter (SISR is start address of ISR):

( PC )i = ( SISR )

CSE 5381/7381 Computer Architecture

Spring 2007

14

Interrupts - Jump to ISR (Cont’d)

Jump to the interrupt service routine ISR (saving values):

Return addresses for interrupt service routine are saved as

( PC )i −1 if ili is of type repeat

( EPC )i = ( PC )i " if ili is of type continue

(*,*)

if ili is of type abort

Exception data register stores a parameter for the exception handler

sext (imm)i for trap interrupts

EDATAi =

for pf or misa during load/store

eai

Exception cause register ECA stores the masked interrupt cause

ECAi = MCAi

Maskable interrupts are masked by SR=0 and old masks are saved as

SRi −1 if ili is of type repeat

ESRi = SRi " if ili is of type continue

*

if ili is of type abort

CSE 5381/7381 Computer Architecture

Spring 2007

15

Interrupts - Jump to ISR (Cont’d)

Jump to the interrupt service routine ISR (saving values):

Processing on interrupt service routine

returning with a rfe instruction

rfe instruction restores saved register and special register values

CSE 5381/7381 Computer Architecture

Spring 2007

16

Precise Exceptions

Precise Exception Handling:

Exceptions caused by instruction Ii take effect on machine

configuration after completion of instructions up to Ii-1

(like in the case of sequential processing)

…I

Problems in pipeline:

i-3

I

i-2

I

i-1

I

i

Ifetch

I

i+1

I

i+2

…

Reg

Exec

Mem

Wr

Ifetch

Reg

Exec

Mem

Ifetch

Reg

Exec

Wr

Mem

Wr

If the pipeline can be stopped so that the instructions just before the

faulting instruction are completed and those after it can be restarted

from scratch

Î The pipeline has precise exceptions

Page fault exception at MEM stage, which instruction to restart ? Which

one(s) to complete?

IF

CSE 5381/7381 Computer Architecture

ID

EX MEM WB

Spring 2007

17

Implementing Precise Exceptions for the MIPS Integer Pipeline

Stage

Exceptions

IF

Page fault; misaligned memory access; memory

protection violation

ID

Undefined or illegal opcode

EX

Arithmetic exception

MEM

Page fault; misaligned memory access; memory

protection violation

WB

None

CSE 5381/7381 Computer Architecture

Spring 2007

18

Implementing Precise Exceptions for the MIPS Integer Pipeline

LW

IF

ADD

ID

EX

MEM

WB

IF

ID

EX

MEM

WB

Multiple exceptions may occur in the same cycle

–

–

–

–

LW Æ page fault

ADD Æ arithmetic exception

First, handle page fault, and restart

The second exception will reoccur

CSE 5381/7381 Computer Architecture

Spring 2007

19

Out-of-order Occurrences of Exceptions

LW

IF

ADD

ID

EX

MEM

WB

IF

ID

EX

MEM

WB

Precise exceptions requires us to first handle LW exception and then

ADD exception.

Exception is recorded in a status vector associated with that

instruction

– Control signals are turned off (register or memory writes)

The status vector is carried along with the instruction

At the WB stage, the status vector is checked

CSE 5381/7381 Computer Architecture

Spring 2007

20

Instruction Set Complications

MIPS:

– Commit stage:

• The end of the MEM stage or the beginning of the WB stage

Some processors, IA-32 architecture

– Autoincrement addressing mode

– State is updated in the middle of the instruction execution

CSE 5381/7381 Computer Architecture

Spring 2007

21

Application to OOO Execution

Avoid the state update before the instruction commit

– Implemented by reorder stage for OOO processors

– Store results in reorder buffer and update store in program

sequence

– Causes stalls if there is dependence on the updated state

CSE 5381/7381 Computer Architecture

Spring 2007

22

Interrupts - ISR for nested Interrupts

Nested Interrupts can be handled by a software protocol

• maintaining a interrupt stack IS consisting of frames

• Each frame can hold a copy of all general purpose registers

and all special purpose registers (32+6=38 words)

• IS.TOP is top frame on interrupt stack.

interrupt stack pointer ISP saves base address in reserved

general purpose register

ISP=GPR[30]

CSE 5381/7381 Computer Architecture

Spring 2007

23

Interrupts - ISR for nested Interrupts

Notation: exception handling registers

EHR = (ESR,ECA,EDPC,EPC,EDATA)

Portion of frame F of the interrupt stack reserved for register R:

F.R

Portion of frame F of the interrupt stack reserved for copies of all exception

handling registers EHR:

F.EHR

Portion of all frames on the interrupt stack reserved for copies of all

exception handling registers EHR:

IS.EHR

CSE 5381/7381 Computer Architecture

Spring 2007

24

Interrupts - ISR for nested Interrupts

Steps of the interrupt service routine for nested interrupts:

SAVE (save status):

{

}

a) Determine current interrupt level: il = min j ECA[ j ] = 1

b) Update interrupt stack: intialize for abort, push new frame otherwise:

ISP = ISP + frame_size

c) Save exception handling registers:

IS.TOP.EHR = EHR

d) Unmask all maskable interrupts j < il:

SR = (031-il,1il )

Exception Handler H(il):

a)

b)

c)

d)

(can be interrupted by interrupts of higher priority)

Save values of general purpose registers that will be used to IS.TOP

branch to start of proper routine for interrupt il

after returning from routine: restore saved general purpose registers from IS.TOP

Mask al maskable interrupts by single special move instruction: SR = GPR[0]

RESTORE (restore status):

a) restore registers from stack:

EDPC = IS.TOP.EDPC;

EPC = IS.TOP.EPC; ESR = IS.TOP.ESR

b) pop top frame from stack:

ISP = ISP - frame_size

c) end interrupt service routine with an rfe instruction

25

Interrupts - Admissible Interrupt Service Routines

Intention:

Interrupts should behave like procedure calls

This is generally not guarantueed.

Several pitfalls possible like, e.g.:

Manipulation of IS.TOP.EDPC in ISR allows to jump everywhere

If interrupt stack is not on permanent memory page,

each interrupt (even page fault interrupts) can lead to page faults

we define Admissible Interrupt Service Routines

have to satisfy certain conditions (not to use certain hacks)

=> our interrupt mechanism behaves like a procedure call and return

(proof in MP pages 181-190)

CSE 5381/7381 Computer Architecture

Spring 2007

26

Interrupts - Admissible Interrupt Service Routines

Set of constraints for Admissible Interrupt Service Routines:

Data structures of the interrupt mechanism must be used in a restructed manner:

•

•

interrupt stack pointer ISP is only written by SAVE and RESTORE

segments of an IS frame reserved for the EHR registers only updated by SAVE

The ISR must satisfy the following constraints:

•

•

•

•

instruction rfe can only be used as the last instruction of the ISR

code segments SAVE and RESTORE avoid any non-maskable

internal interrupt 0 <j < 6

every handler avoids non-maskable internal interrupts i with priority

if handler uses special move SR = R, then bit R[i]=0 for any i ≥ j

i≥ j

The interrupt priorities are assigned such that

1. Non-maskable external interrupts are of type abort and have highest priority

2. Maskable external interrupts are of type continue with lower priority than any

internal interrupt

3. If an instruction can cause several internal interrupts at the same time

=> highest priorized of all the caused interruts must be of type repeat or abort

CSE 5381/7381 Computer Architecture

Spring 2007

27

Interrupts - Hardware for Interrupt support

Hardware Extensions required:

–

–

–

–

Special purpose register file SPR

register S for that buffers data read from SPR

Circuitry for collecting interrupt events CAenv

ISR call mechanism which for active interrupt event (JISR=1):

• Forces interrupt parameters into SPR register file

• Writes

(SISR) to (PC)

– Recovery mechanism to implement rfe

– Control realizing additional instructions from table 5.4

CSE 5381/7381 Computer Architecture

Spring 2007

28

Interrupts - Hardware for Interrupt support

Data path of prepared sequential design with interrupt support:

CSE 5381/7381 Computer Architecture

Spring 2007

29

Register file environment RFenv

Consisting of

General Purpose Register file

and

Special register file of size 6x32 containing registers:

address

0

1

2

3

4

5

name

SR

ESR

ECA

EPC

EDPC

Edata

CSE 5381/7381 Computer Architecture

meaning

status register

exception status register

exception cause register

the exception PC

the exception delayed PC

exception data register

Spring 2007

30

Cause Environment CAenv

Consisting of two parts:

Cause Collection (circuit CAcol):

(see table 5.5, page 203)

– Instruction memory provide ipf and imal flags

– Data memory provides dpf and dmal flag

– Trap and illegal instruction detected by control, indicated by ill and

trap flags

– ALU provides overflow flag ovf (only checked if flag ovf? Is activated

by control for addo, aubo, addio, subio)

Cause Processing (circuit CApro): generating jisr and repeat flags

CA.3'[i ] ∧ SR[i ] if i ≥ 6

mca[i ] =

otherwise

CA.3'[i ]

31

jisr = ∨mca[i ]

i =0

repeat = mca[0] ∨ mca[1] ∨ mca[2] ∧ (mca[3] ∨ mca[4])

CSE 5381/7381 Computer Architecture

Spring 2007

31

Interrupts - Control Unit

Components of the control unit:

Control automaton generating

control signals based on FSD

Stall engine scheduling instruction execution

Stall engine of the prepared sequential DLX

supporting interrupts:

if reset

10000

full[4 : 0] = cls ( full ) if CE ∧ reset

full

otherwise

ue[4 : 0] = full[4 : 0] ∧ CE ∧ reset

Jump to ISR if instruction in stage 4 causes interrupt

JISR = jisr 4 ∧ full[4]

CSE 5381/7381 Computer Architecture

Spring 2007

32

Interrupts

FSD of prepared sequential DLX with interrupt handling:

CSE 5381/7381 Computer Architecture

Spring 2007

33

Interrupts - Pipelined Design

Three Changes:

• Modified PC environment

• Extensive hardware for result forwarding and hazard detection

• Modified stall engine

CSE 5381/7381 Computer Architecture

Spring 2007

34

Interrupts - pipelined design - Forwarding

Forwarding and Interlocking:

General purpose environment

– same as without interrupts

– also works for writing to SPR in movei2s

Special purpose environment

(we need to look at additional sources and destinations )

– sources:

• SPR[Sas] for movs2i in decode stage

• Interrupt mask SR for cause environment in memory stage

• Two exception PCs for rfe during decode stage

– destinations

• SPR[Sad] for movi2s in WB stage

• SR by rfe

• All SPRs updated by JISR (no forwarding necessary, because following

instructions in the pipeline are not considered)

CSE 5381/7381 Computer Architecture

Spring 2007

35

Interrupts - Cost and Delay Analysis

Cost analysis of pipelined DLX with interrupts:

environment

pipelined DLX

pipelined DLX with INTERRUPTS

increase

EX

3315

3795

14%

RF

4066

7257

78%

PC

1906

2610

37%

CA

471

buffer FORW

408

812

2064

1624

406%

100%

DP

Control

13010

830

20610

1283

58%

44%

total

13840

21893

58%

Delay analysis of pipelined DLX with interrupts (without memory paths):

environment

pipelined DLX

pipelined DLX with INTERRUPTS

ID/A/B

72

72

CSE 5381/7381 Computer Architecture

ID/PC

89

89

EX

WB

66

66

Spring 2007

DP

33

33

CON

89

89

57

57

36