Architectural Implications of Brick and Mortar Silicon Manufacturing

advertisement

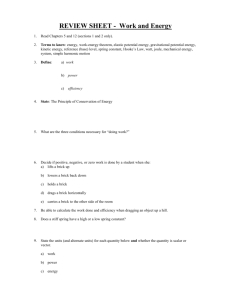

Architectural Implications of Brick and Mortar Silicon Manufacturing Martha Mercaldi Kim Mark Oskin Mojtaba Mehrara Todd Austin University of Washington University of Michigan Cost of Production Production Cost Standard Cell ASIC Product Volume [www.edn.com] 2 Cost of Production Production Cost Standard Cell ASIC FPGA Product Volume [www.edn.com] 3 Cost of Production Production Cost Standard Cell ASIC FPGA Brick & Mortar Goal Product Volume [www.edn.com] 4 Brick and Mortar Chips 1. Bricks • • • Mass-produced ASICs Standard interface Fixed set of functions 5 Brick and Mortar Chips 3DES uP MPEG ETH DMA USB VGA SRAM 1. Bricks • • • Mass-produced ASICs Standard interface Fixed set of functions 5 Brick and Mortar Chips 3DES uP MPEG ETH DMA USB SRAM VGA Interconnect 1. Bricks • • • Mass-produced ASICs Standard interface Fixed set of functions 2. “Mortar” • • • Mass-produced ASIC Standard interface Single, interconnect function 6 Brick and Mortar Chips 1. Bricks • • • Mass-produced ASICs Standard interface Fixed set of functions 2. “Mortar” • • • Mass-produced ASIC Standard interface Single, interconnect function 3. Assembly • • Alignment • e.g. robotics, fluidic Bonding • e.g. flip-chip, proximity 7 Benefits of Brick and Mortar • Chip manufacture: mask-free, fab-free, improved yields • Chip performance: mostly ASIC • Chip design: uses today’s SoC design flow 8 Why Should Architects Care? • Good architecture essential for viability • • Brick function and form-factor Inter-brick interconnect design 9 Outline • Brick and Mortar Chips • • • Definition Potential Architectural Questions • Brick and Mortar Architecture • • Bricks Interconnect • Brick and Mortar Assembly • • Options Interaction with architecture 10 Brick Form Factor Interconnect Interface Functional Block flipchip pad: 25 um pitch, 2.5 Gbps • Each brick . . . • • • is square has 15% of area reserved for extra circuitry has one surface covered with flipchip pads 11 Brick Architecture Synopsys DC Ultra HDL opencores.org, etc. area (um2) Artisan memory compiler max freq. (MHz) Function Description Area (um2) Max Freq. (MHz) USB 1.1 Physical Layer 2,201 2941 JPEG Decoder 625,457 629 RISC Core + 256K Cache 3,111,025 1087 12 Multiple Brick Sizes .5 mm 1 mm Interconnect Interface Functional Block 2 mm 13 Brick Size Selection Function Description 256 K SRAM (single-ported) JPEG Decoder VGA/LCD Controller • Circuit Area Max Freq. (um2) (MHz) Freq. Range at Brick Size Small Medium Large 2,729,344 2315 No Space No Space N/A - 2315 625,457 629 No Space N/A - 629 No Benefit 4,301 1219 N/A - 1046 N/A - 1219 No Benefit Smallest brick to fit circuit, unless bandwidth severely constrained 14 Outline • Brick and Mortar Chips • • • Definition Potential Architectural Questions • Brick and Mortar Architecture • • Bricks Interconnect • Brick and Mortar Assembly • • Options Interaction with architecture 15 Interconnect Dilemma time Architecture Design Chip Design process steps 1. Brick Functions 2. Brick Size 3. Interconnect Design 1. Brick Selection 2. Brick Arrangment Execution Static Communication 1. Input Data Dynamic Communication • General purpose interconnect facilities • • Communication known at design time configurable wires Dynamic communication packet-switched net 16 Outline • Brick and Mortar Chips • • • Definition Potential Architectural Questions • Brick and Mortar Architecture • • Bricks Interconnect • Brick and Mortar Assembly • • Options Interaction with architecture 17 Brick and Mortar Chips 1. Bricks • • • Mass-produced ASICs Standard interface Fixed set of functions 2. “Mortar” • • • Mass-produced ASIC Standard interface Single, interconnect function 3. Assembly • • Alignment • e.g. robotics, fluidic Bonding • e.g. flip-chip, proximity 18 Assembly Alternatives • Alignment • • • • Robotic • • • Flip-chip Self-Assembly Martha + tweezers ... • Bonding Proximity ... 19 Assembly Alternatives • Alignment • • • • Robotic $$$, but fast Self-Assembly $, but slow • • • Flip-chip Martha + tweezers ... • Bonding Proximity ... 19 Assembly Alternatives • Alignment • • • • Robotic $$$, but fast Self-Assembly $, but slow • • • Flip-chip Martha + tweezers ... • Bonding Proximity ... 19 Assembly Alternatives • Alignment • • • • Robotic $$$, but fast Self-Assembly $, but slow • • • Flip-chip medium-density, but more robust connection Proximity high-density Martha + tweezers ... • Bonding ... 19 Assembly Alternatives • Alignment • • • • Robotic $$$, but fast Self-Assembly $, but slow • • • Flip-chip medium-density, but more robust connection Proximity high-density Martha + tweezers ... • Bonding ... 19 Alignment: Fluidic Self Assembly template (active silicon) • Template - brick communication via proximity communication • • Brick type check, BIST, speed grade Polymer on template can grip or eject bricks 20 Alignment: Fluidic Self Assembly • Washington EE experimental system 21 Assembly Time v. Number of Bricks • Statistical simulator driven by experimentally derived rates of assembly and disassembly 22 Assembly Time v. Number of Bricks 250 75 10 bricks 10 bricks 20 bricks 22 Assembly Time v. Kinds of Bricks 23 Assembly Time v. Kinds of Bricks 23 Assembly Time v. Kinds of Bricks 23 Assembly Time v. Kinds of Bricks 23 Assembly Time v. Brick Arrangement Slack 24 Evaluating Slack: Design Size 25 Evaluating Slack: Brick Kinds 26 Evaluating Slack: Brick Kinds 26 Assembly and Architecture • Architecture can assist assembly by • Reducing the number of kinds of bricks • • i.e., two brick kinds v. one slightly reconfigurable circuit Accommodating variable assemblies 27 Conclusion • Brick and Mortar process offers ASIC-like chips without the masks and fabs • Architecture is crucial to meet the performance goals of the process • With low-cost assembly techniques, can meet the economic goal as well 28