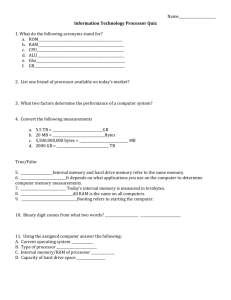

lec 3.0 - 8085 internal architecture

advertisement

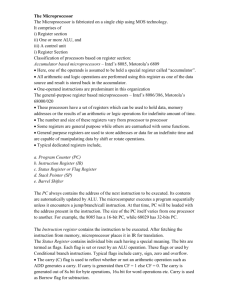

8085 INTERNAL ARCHITECTURE Upon completing this topic, you should be able to: • State all the register available in the 8085 • • • • microprocessor and explain their function Explain the function of stack Depict the ALU subsystem List and describe the function of control logic signal in the processor Elaborate the process of de-multiplexing data bus and address bus 2 3 4 6 x 8-bit registers with addresses B, C, D, E, H & L Can be concatenated to form 3 x 16-bit registers with addresses BC, DE & HL. Note : 16-bit register HL used as a memory pointer with many 8085A instructions. • e.g MOV A, M which copies the contents of the memory location whose address is specified by the contents of the HL register pair to the CPU register A • Note the assembly language instruction format MOV <destination> <source> 16-bit register SP. It contains the address of the memory location of the top of the stack area of memory. It is automatically controlled by the processor but can be initialized by software. 16 – bit register PC. It contains the address of the memory location from where the CPU is to fetch the next instruction byte. 5 The program counter is a 16-bit CPU register. The program counter always contains the address of the memory location from where the CPU is to fetch the next instruction byte. The program counter is automatically incremented every time the CPU fetches an instruction byte. Instructions are thus executed in the sequence they are loaded into program memory. The contents of the program counter can be overwritten by execution of certain instructions e.g. jmp, call, ret etc. The program counter is initialized to 0000H after processor reset or on power-up. 6 The stack is a reserved area of memory. It operates as a lastin first-out bank of registers. The memory locations, which constitute the stack, are used to store binary information temporarily during program execution. The stack can be located anywhere in read/write memory, but is usually defined such that it neither interferes with the program memory space or the data memory space. The start address of the stack is specified at the initialisation stage of the program by loading the 16-bit CPU register, called the stack pointer, with the desired address of the start of the stack. • e.g LXI SP, data 16 7 Data from CPU register pairs are stored in the stack area of memory when the processor executes a push rp instruction. The contents of the program counter is automatically stored in the stack area of memory whenever the processor executes a call or restart (rst n) instruction. Data stored in the stack area of memory are returned to processor register pairs when the processor executes a pop rp instruction. Data is automatically transferred from the stack area of memory to the program counter whenever the processor executes a return (ret) instruction. 8 To execute the instruction push HL assuming initial SP contents is 2099 H. The stack pointer is decremented by 1 (SP=2098) and the contents of H are written to this location. The stack pointer is decremented by 1 (SP=2097) and the contents of L are written to this location. Note : When data is written to the stack the stack pointer is first decremented and then the data is written 9 To execute the instruction pop BC assuming initial SP contents is 2097 H. The contents of the memory location at the address specified by the contents of SP is moved to register C and SP is incremented. The contents of the memory location at the address specified by the contents of SP is moved to register B and sp is incremented. Note : When data is read from the stack the data is read first and then the stack pointer incremented. 10 11 12 The ALU itself is a group of combinatorial logic circuits that can perform 8-bit arithmetic and logical operations. Included are :- add, sub, and, or, xor The accumulator ( reg A ) is an 8-bit general purpose register that holds one of the source operands of an ALU operation. The result of the operation is also returned to the accumulator. The temporary accumulator is an 8-bit register that holds the second operand used in a ALU operation. It is inaccessible to the user. The decimal adjust unit allows the ALU to perform BCD arithmetic. (rarely used as it is usual to use binary, as opposed to BCD, arithmetic) 13 The flag register is a collection of eight, single bit registers. It reflects outcomes of arithmetic or logical operations. • The Sign Flag (S) reflects the contents of bit-7 of the accumulator • The Zero Flag (Z) is set to ‘1’ if the accumulator contains all zero’s • The Auxiliary Carry (AC) is a ‘1’ if the arithmetic operation caused a carry out from the bit-3 to the bit-4 position. (The auxiliary carry flag is used in BCD arithmetic) • The Parity Flag (P) is a ‘1’ if the accumulator has an even number of ‘1’s • The Carry Flag (CY) is set if the arithmetic operation caused a carry overflow (from addition) or a borrow (from subtraction). 14 Example: ADD B register A register B register A S=0 Z=0 AC = 1 P=1 CY = 1 ; A contains 88 (H) B contains 99 (H) 10001000 10011001 136 153 _____________ _____ 100100001 289 decimal decimal decimal Bit D7 = 0 after addition The accumulator contains other than zero after addition There is a carry out of bit D3 to bit D4 during addition The accumulator contains an even number of ‘1’s after addition There is an overflow as a result of the addition 15 The control logic subsystem of a microprocessor is a configurable sequential state machine. It is configured by the instruction decoding circuitry to enable execution of a particular instruction. It has associated with it a number of inputs and outputs, both from other subsystems of the CPU and from external devices. It operates with respect to a stable clock reference signal provided by a crystal source. Typical clock frequencies for an 8085A microprocessor are in the order of 5-MHz. The internal clock for the control logic is half the frequency of the external crystal source (i.e internally the crystal source clock is divided by 2) 16 17 RD (o) A logic ‘0’ specifies the processor will read the data on the data bus. WR (o) A logic ‘0’specifies that the processor has placed data (write) onto the data bus for an external device to read. S0 S1 IO / M (o) A 3-bit status code that specifies the operation the processor is performing. (e.g 110 specifies the processor is fetching an opcode from program memory). reset out (o) A logic ‘1’ on the reset in input to the processor causes the program counter to be reset to 0000H. To indicate the processor has been reset a logic `1’, synchronized to the processor clock, is placed on this output. 18 CLK out (o) Is a buffered version of the internal master clock of the 8085A. It is half the crystal frequency. HOLD (i) HLDA (o) An external device can request use of the system ALE (o) busses by driving the HOLD input to logic ‘1’. The 8085A acknowledges the request by asserting the HLDA output to logic ‘1’. It only does after it has relinquished control of the bus structure. When this signal is logic ‘1’ the processor specifies that it has valid address information on the CPU pins AD07 RDY (i) When this signal is logic ‘0’ the processor suspends execution of an instruction. It permits slow peripheral devices more time to access or load data. 19 The 8085A microprocessor uses only 16 connections to interface the 8-bit data bus and 16-bit address bus. Address bus lines A are time multiplexed with data 07 bus lines D 07 3/24/2016 20 Peripheral devices ( memory and IO ) require stable address data throughout a read or write operation. The processor only provides A0 - A7 during the period ALE is in the logic ‘1’ state after which the multiplexed lines AD0 AD7 assume the role of the data bus. ( D0 - D7 ) To provide external devices with stable address data throughout a read or write operation it is necessary to latch the low byte of the address using the ALE control signal. By this mechanism it is possible for the 8085A computer system to have a 16-bit address bus and an 8-bit data bus whilst only using 16 processor connections ( AD0 - AD7 and A8 - A15 ) 21 Note : See through latches ( eg 74LS573 ) are the preferred type of latch. When clk (ALE) is logic ‘1’ the latch outputs follow the inputs and on the negative edge of clk the data is latched. 3/24/2016 22