Lecture_11-Synchronous_Sequential_Design

advertisement

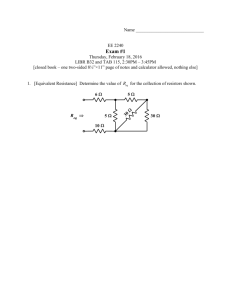

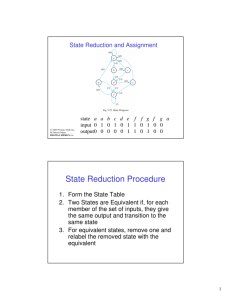

DESIGN OF SEQUENTIAL CIRCUITS by Dr. Amin Danial Asham References Digital Design 5th Edition, Morris Mano State Reduction Sequential circuit analysis starts with circuit diagram and ends by obtaining state table and state diagram. Sequential circuit design or synthesis starts with the required specifications and ends by obtaining the circuit diagram. Two sequential circuit may have the same input output behavior but have different internal states. Reducing the number of FF’s in a sequential circuit is called state reduction, while keeping the same number of inputs and outputs. Reducing the number of FF’s and logic gates saves the cost of the circuit. 𝑚 FF’s generate 2𝑚 states, hence reducing the number of states may or may not reduce the number of FF’s. Sometimes reducing the number of FF’s produces more combinational gates to produce the next state and output logic. State Reduction (continue) In sequential circuits the input and output sequences are important and the internal state role is just to produce these sequences. As an example, a sequential circuit with the following state diagram: o The states are denoted by letter since the binary values are not important. o Using the state diagram we get the output sequence corresponding to the input sequence 01010110100. o This sequential circuit has 7 internal states: 𝑎, 𝑏, 𝑐, 𝑑, 𝑒, 𝑓, 𝑔 State Reduction (continue) If input-output is considered, two sequential circuits with different number of FF’s are considered equivalent if each input sequence applied to the two circuits produces the same output sequence. “Two states are said to be equivalent if, for each member of the set of inputs, they give exactly the same output and send the circuit either to the same state or to an equivalent state.” If there are two equivalent states, one of them can be removed without changing the input-output relations. Now to reduce the number of states, the state table will be used and searching for equivalent states. State Reduction (continue) Equivalent states. They both go to states 𝑎 and 𝑓 and have outputs of 0 and 1 for x = 0 and x = 1, respectively State Reduction (continue) Since the two states 𝑒 and 𝑔 are equivalent, one of them can be removed. Replacing the removed state with its equivalent in the table. Equivalent states. They both go to states 𝑒 and 𝑓 and have outputs of 0 and 1 for x = 0 and x = 1, respectively State Reduction (continue) Since the two states 𝑑 and 𝑓 are equivalent, one of them can be removed. Replacing the removed state with its equivalent in the table. State Assignment To design a sequential circuit the states are coded in a binary coded form. If we have 𝑚 states we use 𝑛 bits code such that 2𝑛 ≥ 𝑚. Examples of the assignments: 3 FF’s 3 FF’s 5 FF’s State Assignment (continue) The reduced 5 states in our example are coded using binary code. Three bits can be used to code 8 states, we used 5 states and the other 3 states are considered don’t care. The state table using the binary assignment is sometimes called the transition table to be distinguished from the state table with symbolic names for the states. Design Procedure 1. From the word description and specifications of the desired operation, derive a state diagram for the circuit. 2. Reduce the number of states if necessary. 3. Assign binary values to the states. 4. Obtain the binary-coded state table. 5. Choose the type of flip-flops to be used. 6. Derive the simplified flip-flop input equations and output equations. 7. Draw the logic diagram. Example Design a circuit that detects a sequence of three or more consecutive 1’s in an input stream. The state diagram of this detector can be as shown. o There are four states S0, S1, S2, and S3, which represents 0 at input, single 1, two consecutive 1’s, or three or more consecutive 1’s respectively. o The output of this detector is 1 when 3 or more consecutive 1’s are detected. Example – D FF implementation The four states are assigned binary codes 00,01,10,11 and hence two FF’s 𝐴 and 𝐵 are needed. The state table is: The characteristic equations are: 𝐴 𝑡 + 1 = 𝐷𝐴 𝐵 𝑡 + 1 = 𝐷𝐵 From the table we find: 𝑨 𝒕 + 𝟏 = 𝑫𝑨 𝑨, 𝑩, 𝒙 = (𝟑, 𝟓, 𝟕) 𝑩 𝒕 + 𝟏 = 𝑫𝑩 𝑨, 𝑩, 𝒙 = (𝟏, 𝟓, 𝟕) Input Equations Example – D FF implementation (continue) Output equation is: 𝑦(𝐴, 𝐵, 𝑥) = (6,7) Example – D FF implementation (continue) Since the input and output equations are written down as sum of minterms, therefore the these equation can be simplified using K-maps. Example – D FF implementation (continue) Excitation Tables To design Sequential circuits with 𝐽𝐾 and 𝑇 FF’s, tables that list the required inputs for a given change of state are needed. These tables are called excitation tables. Excitation tables are used to drive the input equations. + + Design using 𝑱𝑲 FF An example to design a sequential circuit specified with the following state table. + From the excitation table of 𝐽𝐾 FF: we can get the FF input for state transitions as follows: Design using 𝑱𝑲 FF (continue) Input Equations are derived using K-maps. 𝐾𝐵 = 𝐴𝑥 + 𝐴′ 𝑥 ′ = (𝐴⨁𝑥)′ Design using 𝑱𝑲 FF (continue) Logic Diagram Design using 𝑻 FF An Example of design 3 bit counter which has the following state diagram. This counter counts from 0 to 23 − 1. Form the stat diagram there are three FF’s that will be named 𝐴2 , 𝐴1 , and 𝐴0 Therefore, the state table is as follows: Using excitation table we get the FF inputs. + 0 Excitation Table Design using 𝑻 FF Input Equations are derived using K-maps 0 Design using 𝑻 FF Logic Diagram Thanks