EE 5342 Lecture

advertisement

Semiconductor Device

Modeling and Characterization

EE5342, Lecture 30

Spring 2003

Professor Ronald L. Carter

ronc@uta.edu

http://www.uta.edu/ronc/

L30 01May03

1

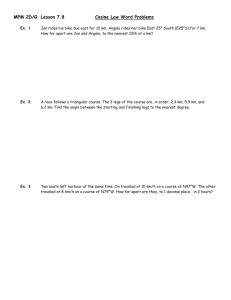

Gummel-Poon Static

npn Circuit Model

C

RC

B

RBB

B’

ILC

IBR

ILE

IBF

Intrinsic

Transistor

ICC - IEC = {IS/QB}*

{exp(vBE/NFVt)exp(vBC/NRVt)}

RE

L30 01May03

E

2

Gummel Poon npn

Model Equations

IBF = IS expf(vBE/NFVt)/BF

ILE = ISE expf(vBE/NEVt)

IBR = IS expf(vBC/NRVt)/BR

ILC = ISC expf(vBC/NCVt)

ICC - IEC = IS(exp(vBE/NFVt - exp(vBC/NRVt)/QB

QB = { + [ + (BF IBF/IKF + BR

IBR/IKR)]1/2 } (1 - vBC/VAF - vBE/VAR )-1

L30 01May03

3

VBIC Model Overview

[5]

Self-heating effects included

Improved Early effect

modeling

Quasi-saturation modeling

Parasitic substrate transistor

modeling

Parasitic fixed (oxide)

capacitance modeling

An avalanche multiplication

model included

Base current is decoupled

from collector current

L30 01May03

4

CAD Tools Support for VBIC

• Hspice

[4]

Does not support PNP device

Does not scale with “Area” and “M” terms

• Spectre

[5]

Support both NPN and PNP devices

scale with “Area” and “M” term

• HPADS

No temperature nodes (“dt” and “tl”), so

unable to simulate thermal coupling effects

L30 01May03

5

Temperature Designations for VBIC

Parameters

Description

Spectre

[4]

Hspice

[5]

Name

Default

Name

Default

Temperature rise of

the device from

ambient

trise

0

dtemp

0

Ambient temp.

temp

27

temp

25

Parameters

measurement

temperature

tnom

27

tnom

25

tref

27

L30 01May03

6

Using VBIC in Spectre

[5]

Name c b e [s] [dt] [tl] ModelName

parameter=value ...

• Selft=1 and Rth>0 to enable Self-heating

• 1 volt at the temperature nodes = 1 degree in

temperature

• “tl” node represents the initial local temperature

of device which always corresponds to

trise+temp

• “dt” node represents the rise above trise+temp

caused by thermal dissipation, whose value equals

V(dt)-V(tl)

• Device temperature=V(dt)-V(tl)+trise+temp

L30 01May03

7

Using VBIC in Cadence

• Need explicit external temperature nodes in the

symbol to model inter-device thermal coupling by

Connecting thermal network between “dt” nodes, or

Adding VCVS between “tl” and “tlr” node

• Customized VBIC 6-terminal (5-pin) symbol

L30 01May03

8

Model Conversion

•

•

•

•

Most BJTs are defined with SGP model

A conversion from SGP to VBIC is needed

Only approximate conversion is possible

Some parameters are left unmapped such as Rth and

Cth

• Two approaches are provided

Manual conversion — done empirically and need Local

Ratio Evaluation [2]

Program conversion — “official” program sgp_2_vbic

[3]

L30 01May03

9

Parameters Mapping by sgp_2_vbic

VBIC

Rcx

Rci

Rbx

Rbi

Re

Is

Nf

Nr

Fc

Cje

Pe

Me

Cjc

Cjep

Pc

mapping

Rc

0

Rbm

Rb-Rbm

Re

Is

Nf

Nr

Fc

Cje

Vje

Mje

Cjc·Xcjc

Cjc(1-Xcjc)

Vjc

L30 01May03

VBIC

Mc

Cjcp

Ps

Ms

Nei

Iben

Nen

Ibei

Ibci

Nci

Ibcn

Ncn

Ikf

Ikr

Tf

mapping

Mjc

Cjs

Vjs

Mjs

Nf

Ise

Ne

Is/Bf

Is/Br

Nr

Isc

Nc

Ikf

Ikr

Tf

VBIC

Xtf

Vtf

Itf

Tr

Td

Ea

Eaie

Eaic

Eane

Eanc

Xis

Xii

Xin

Kfn

Afn

Early Effect model is

mapping

different

Xtf

Need Vbe, Vbc to solve

Vtf

the 3 equations below

Itf

Tr

g OF

1 / VAF

Tf·Ptf/180

I C 1 VbeF / VAR VbcF / VAF

Eg

Eg

Eg

g oR

1 / VAR

Eg

I e 1 VbeR / VAR VbcR / VAF

Eg

Xti

F CbcF

1

F

q

q

Xti-Xtb

be

bc F

g

/

I

c

o

VEF 1

Xti-Xtb

CbeR 1 1

R

R

Kf

qbe R

qbc

g o / I e VER

Af

10

L30 01May03

11

Heterojunction

Electrostatics

qfp

EC,p

qfn

DEC

EC,n

EF,p

EF,n

EV,p

EV,n

L30 01May03

Eo

DEV

-xn

0

xp

12

Poisson’s Equation

dEx n qND

dx

n

n

Ex

dEx p qNA

dx

p

p

Exdx Vbi,n

-xn

Exdx Vbi,n

L30 01May03

x

xp

Continuity eqn at x 0

nEx x 0 pEx x 0

13

Heterojunction

electronics

Charge neutrality, qNdxn qNa xp

Vbi fp fn

qfn Eo Ef,n qn Ec Ef,n

Ec Ef,n kT lnNc / Nd

qfn qn Eg,n Ef,n Ev,n

Ef,n Ev,n kT lnNv / pno , pno ni2 / Nd

L30 01May03

14

Heterojunction

electronics (cont)

qfp Eo Ef,p q p Ec Ef,p ,

Ec Ef,p kT lnNc / npo , npo ni2 / Na .

qfp q p Eg,p Ef,p Ev,p ,

Ef,p Ev,p kT lnNv / Na ,

c.f. 8.39 & 8.40 in text.

L30 01May03

15

Heterojunction

electronics (cont)

e.g. 8.39

ppo Nv,n

,

qVbi DEv kT ln

p

N

no v,n

ppo Na , and pno ni2/Nd .

Since hole injection is important,

and the appropriate barrier is DEv

then this is the appropriate form.

L30 01May03

16

Heterojunction

depletion widths

2n pV N Na,p 2

bi d,n

W xn xp

qN Na,p nN pNa,p

d,n

d,n

2n pVbiNa,p

xn

qN nN pNa,p

d,n

d,n

2n pVbiNd,n

xp

qNa,p nN pNa,p

d,n

L30 01May03

17

Final Exam

• Review a paper on “Device Parameter

Extraction”.

• Paper to be reviewed will be posted

Monday, May 5, 2003

• Comment on Device Physics used.

• Critique the extraction procedures

– Assumptions

– Consistency of method w.r.t. assumptions

• One page solution due 11 AM, Thur., May 8

L30 01May03

18

References

•

•

•

•

•

Fujiang Lin, et al, “Extraction Of VBIC Model for SiGe

HBTs Made Easy by Going Through Gummel-Poon Model”,

from

http://eesof.tm.agilent.com/pdf/VBIC_Model_Extractio

n.pdf

http://www.fht-esslingen.de/institute/iafgp/neu/VBIC/

Avanti Star-spice User Manual, 04, 2001.

Affirma Spectre Circuit Simulator Device Model

Equations

Zweidinger, D.T.; Fox, R.M., et al, “Equivalent circuit

modeling of static substrate thermal coupling using

VCVS representation”, Solid-State Circuits, IEEE

Journal of , Volume: 2 Issue: 9 , Sept. 2002, Page(s):

1198 -1206

L30 01May03

19

![[Company Name] Certificate of Completion](http://s2.studylib.net/store/data/005402466_1-8a11f4ced01fd5876feee99f8d8e6494-300x300.png)