EE 5342 Lecture

advertisement

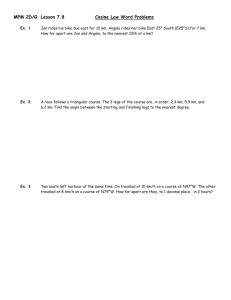

EE5342 – Semiconductor Device Modeling and Characterization Lecture 30 May 05, 2010 Professor Ronald L. Carter ronc@uta.edu http://www.uta.edu/ronc/ dt for VBIC-R1.5 model • Model: VBIC-R1.5. • “selft” flag set to 1. • No optimization done. • No external circuit connected. • Rth=5.8E+0 • Cth=96E-12 L30 05/05/10 2 VBIC-R1.5 Y11 plot (standard data) L30 05/05/10 3 VBIC-R1.5 Y11 plot (standard data) L30 05/05/10 4 VBIC-R1.2 Y11 plot (optimized data) • For optimized data refer slide “Model Parameters”. • Circuit used is shown in “Circuit for Y parameters (optimized data)” slide. fc Τ fc1= 2E3 7.962E-05 fc2= 9.25E4 1.721E-06 fc3= 3.2E6 4.976E-08 Fc4=2E3 7.962E-05 Fc5=1E5 1.592E-06 Fc6=4E6 3.981E-08 fc7= 2E3 7.962E-05 fc8= 1E5 1.592E-06 fc9=4E6 3.981E-08 L30 05/05/10 5 Spreadsheet for Calculating the Rth and Cth • Calculations mentioned in the previous slides have been implemented in an Excel spreadsheet. • The Cauer to Foster network transformation is done. Fig. 7. Electrical equivalent Cauer network of the HBT Fig. 8. Electrical equivalent Foster network of the HBT • The spreadsheet takes the dimensions of different layers of the devices and gives corresponding Cauer and Foster network values. This enables the calculation of time constants which can be converted into a single pole. The characteristic times for the Foster network appear on a impulse response plot. L30 05/05/10 6 IC-CAP Simulations L30 05/05/10 7 Effect of Rth on current feedback op-amp settling time 500 500 W W - vOUT + 100 W vIN = 1 V P-P, t = 200 m-sec Offset L30 05/05/10 vOUT ,max vOUT t AvIN,max 8 Current Feedback Op Amp Data (LMH6704) Switching Offset Thermal switching offset as % of Vp 1.00% cfoa model 0.39% e t / 13.4 0.16% e t / 3.3 y = 0.0039e-0.0749x Offset = .39% Tau = 13.4 u-sec 0.10% y = 0.0055e-0.1416x Offset = 0.16% Tau = 7.1 u-sec Tau 0.01% 0 L30 05/05/10 5 0.16% 3.3 0.55% / 7.7 0.39% / 13.4 10 15 20 25 Time after switching (u-sec) 9 30 LMH6550 impulse thermal characteristics • LeCroy sampling oscilloscope (1MW input mode) • Maximum averaging (10000) • Input nominally +/- 1V with 50 micro-sec period and 50% duty cycle. • Fractional Gain Error = FGE vOUT (t) FGE L30 05/05/10 vOUT ,max vIN (t) vIN,max 1 10 vIN Rising Response 1.2 10.00% vIN 1.0 0.8 0.6 0.4 0.2 FGE vOUT 1.00% y = 0.0362e-111568x R2 = 0.9707, Tau = 9 micro-sec 0.0 0.0E+00 L30 05/05/10 5.0E-06 1.0E-05 1.5E-05 0.10% 2.0E-05 11 vIN Falling Response 0 10.00% -0.2 vOUT -0.4 y = 0.0373e-148345x R2 = 0.9257 Tau = 6.7 micro-sec -0.6 1.00% -0.8 -1 -1.2 0.0E+00 L30 05/05/10 FGE vIN 5.0E-06 1.0E-05 1.5E-05 0.10% 2.0E-05 12 Current Feedback Op-Amp (CFOA) with Simple Current Mirror (CM) Bias VCC Q3 Q4(stk2pnp-cm) Q9 Q10 Q17 Q7(stk3-npn-bf) 200 μA +1 V Q6 Q14 VEE VP VCC VEE Z VN Q5 -1 V Q 15 RF Q13 Q8(stk3-pnp-bf) Q1 Q2 Q11 VO VCC Q12 Q 16 Q18 sup VEE L30 05/05/10 STICK1 STICK2 STICK3 STICK4 STICK5 STICK6 13 Large-signal Output Voltage Transient Analysis for CFOA with Simple CM Biasing Voltage (mV) -968 High-to-Low area x1 High-to-Low area x8 -970 TT=-5311 mV -972 -974 TT=-789 mV -976 -978 0 5 10 15 20 25 30 35 40 45 Time (ms) Voltage (mV) 1028 1026 Low-to-High area x1 Low-to-High area x8 TT=5313 mV 1024 1022 TT=789 mV 1020 0 L30 05/05/10 5 10 15 20 25 Time (ms) 30 35 40 45 14 Hypothesis: The Thermal Tail is a Linear Superposition of the Contribution from each Individual Circuit Stick • The contribution of individual transistor to the total thermal tail. • Used six stick classifications according to transistor type and functionality. i.e. Q10stk3-pnp-bf and Q11stk4-npn-cm • Enabled the self-heating effect in the stick of interest and disabled the self-heating effect of the remaining transistors. • Simulated the contribution of each individual stick. • The total thermal tail simulated is essentially the sum of the individual thermal tail contributions of each circuit stick. L30 05/05/10 15 The Hypothesis Supported Area x1 Thermal Tail (uV/V) Area x8 High-to-Low Low-to-High High-to-Low Low-to-High stk2-npn-bf (Q5) -822 842 -124 128 stk2-pnp-bf (Q6) -727 712 -101 98 stk2-npn-cm (Q2) -89 91 -11 12 stk2-pnp-cm (Q4) -91 89 -10 9 stk3-npn-bf (Q7) -877 850 -111 106 stk3-pnp-bf (Q8) -783 808 -111 115 stk4-npn-cm (Q12) -1213 1217 -172 173 stk4-pnp-cm (Q10) -1075 1073 -159 158 stk5-npn-bf(Q13) 13 -13 2 -2 stk5-pnp-bf(Q14) -4 4 -1 1 stk5-npn-cm(Q18) 16 -15 2 -2 stk5-pnp-cm(Q17) -5 2 0 0 stk6-npn-bf(Q15) 0 1 0 0 stk6-pnp-bf(Q16) -1 0 0 0 added total -5658 5661 -796 796 simulated total -5311 5313 -789 L30 05/05/10 16 789 L30 05/05/10 17 Heterojunction Electrostatics qfp EC,p qfn DEC EC,n EF,p EF,n EV,p EV,n L30 05/05/10 Eo DEV -xn 0 xp 18 Poisson’s Equation dEx n qND dx n n Ex dEx p qNA dx p p Exdx Vbi,n -xn Exdx Vbi,n L30 05/05/10 x xp Continuity eqn at x 0 nEx x 0 pEx x 0 19 Heterojunction electronics Charge neutrality, qNdxn qNa xp Vbi fp fn qfn Eo Ef,n qn Ec Ef,n Ec Ef,n kT lnNc / Nd qfn qn Eg,n Ef,n Ev,n Ef,n Ev,n kT lnNv / pno , pno ni2 / Nd L30 05/05/10 20 Heterojunction electronics (cont) qfp Eo Ef,p q p Ec Ef,p , Ec Ef,p kT lnNc / npo , npo ni2 / Na . qfp q p Eg,p Ef,p Ev,p , Ef,p Ev,p kT lnNv / Na , c.f. 8.39 & 8.40 in text. L30 05/05/10 21 Heterojunction electronics (cont) e.g. 8.39 ppo Nv,n , qVbi DEv kT ln p N no v,n ppo Na , and pno ni2/Nd . Since hole injection is important, and the appropriate barrier is DEv then this is the appropriate form. L30 05/05/10 22 Heterojunction depletion widths 2n pV N Na,p 2 bi d,n W xn xp qN Na,p nN pNa,p d,n d,n 2n pVbiNa,p xn qN nN pNa,p d,n d,n 2n pVbiNd,n xp qNa,p nN pNa,p d,n L30 05/05/10 23 References • • • • • Fujiang Lin, et al, “Extraction Of VBIC Model for SiGe HBTs Made Easy by Going Through Gummel-Poon Model”, from http://eesof.tm.agilent.com/pdf/VBIC_Model_Extractio n.pdf http://www.fht-esslingen.de/institute/iafgp/neu/VBIC/ Avanti Star-spice User Manual, 04, 2001. Affirma Spectre Circuit Simulator Device Model Equations Zweidinger, D.T.; Fox, R.M., et al, “Equivalent circuit modeling of static substrate thermal coupling using VCVS representation”, Solid-State Circuits, IEEE Journal of , Volume: 2 Issue: 9 , Sept. 2002, Page(s): 1198 -1206 L30 05/05/10 24 Thermal Analogy References [1] I.Z. Mitrovic , O. Buiu, S. Hall, D.M. Bagnall and P. Ashburn “Review of SiGe HBTs on SOI”, Solid State Electronics, Sept. 2005, Vol. 49, pp. 1556-1567. [2] Masana, F. N., “A New Approach to the Dynamic Thermal Modeling of Semiconductor Packages”, Microelectron. Reliab., 41, 2001, pp. 901–912. [3] Richard C. Joy and E. S. Schlig, “Thermal Properties of Very Fast Transistors”, IEEE Trans. ED, ED-1 7. No. 8, August 1970, pp. 586599. [4] Kevin Bastin, “Analysis and Modeling of self heating in SiGe HBTs” , Aug. 2009, Masters Thesis, UTA. [5] Rinaldi, N., “On the Modeling of the Transient Thermal Behavior of Semiconductor Devices”, IEEE Trans-ED, Volume: 48 , Issue: 12 , Dec. 2001; Pages:2796 – 2802. L30 05/05/10 25 Simulation … References • • [1] E. Castro, S. Coco, A. Laudani, L. LO Nigro and G. Pollicino, “A New Tool For Bipolar Transistor Characterization Based on HICUM”, Communications to SIMAI Congress, ISSN 1827-9015, Vol. 2, 2007. [2] K. Bastin, “Analysis And Modeling of Self Heating in Silicon Germanium Heterojunction Bipolar Transistors”, Thesis report, The University of Texas at Arlington, August 2009. L30 05/05/10 26 AICR Team at University of Texas Arlington - Electrical Engineering Earlier Contributors Current • Ronald L. Carter, Professor • W. Alan Davis, Associate Professor • Howard T. Russell, Senior Lecturer • Ardasheir Rahman1 • Ratan Pulugurta1 • Xuesong Xie1 • Arun Thomas-Karingada2 • Sharath Patil2 • Valay Shah2 L30 05/05/10 • • • • • • Kevin Bastin, MS Abhijit Chaugule, MS Daewoo Kim, PhD Anurag Lakhlani, MS Zheng Li, PhD Kamal Sinha, PhD 1PhD Student 2MS Student 27

![[Company Name] Certificate of Completion](http://s2.studylib.net/store/data/005402466_1-8a11f4ced01fd5876feee99f8d8e6494-300x300.png)