Q=0

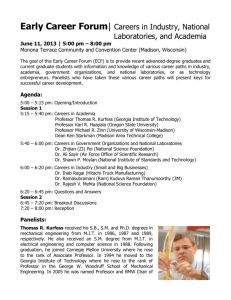

advertisement