DC Bias 2

advertisement

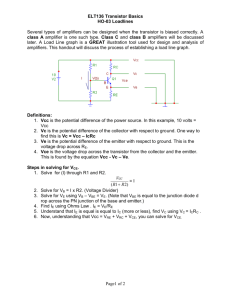

Voltage Divider Bias ELEC 121 BJT Biasing 3 For the Voltage Divider Bias Configurations • Draw Equivalent Input circuit • Draw Equivalent Output circuit • Write necessary KVL and KCL Equations • Determine the Quiescent Operating Point – Graphical Solution using Loadlines – Computational Analysis • Design and test design using a computer simulation January 2004 ELEC 121 2 Voltage-divider bias configuration January 2004 ELEC 121 3 Voltage Divider Input Circuit Approximate Analysis The Approximate method may be used only when R2 .1 RE Under these conditions RE does not significantly load R2 and it is effect may be ignored: IB << I1 and I2 and I1 I2 Therefore: R2 VB = VCC R1 + R2 We may apply KVL to the input, which gives us: -VB + VBE + IE RE = 0 Solving for IE we obtain: IE = VB - VBE RE January 2004 ELEC 121 4 Input Circuit Exact Analysis The Exact Analysis method is always valid must be used when R2 > .1 RE Perform Thevenin’s Theorem using the transistor as the load Open the base lead of the transistor, and the Voltage Divider bias circuit is: R2 VTH = VCC R1 + R2 Calculate RTH We may apply KVL to the input, which gives us: -VTH + IB RTH + VBE + IE RE = 0 Since IE = ( + 1) IB RTH + VBE + IE RE = 0 β +1 Solving for IE we obtain: -VTH + IE IE = VTH - VBE RTH + RE β +1 January 2004 ELEC 121 5 Redrawing the input circuit for the network January 2004 ELEC 121 6 Determining VTH R2 VTH = VCC R1 + R2 January 2004 ELEC 121 7 Determining RTH RTH = January 2004 R1 R2 R1 + R2 ELEC 121 8 The Thévenin Equivalent Circuit Note that VE = VB – VBE and IE = ( + 1)IB January 2004 ELEC 121 9 Input Circuit Exact Analysis We may apply KVL to the input, which gives us: -VTH + IB RTH + VBE + IE RE = 0 Since IE = ( + 1) IB RTH -VTH + IE + VBE + IE RE = 0 β +1 Solving for IE we obtain: VTH - VBE IE = RTH + RE β +1 January 2004 ELEC 121 10 Collector-Emitter Loop January 2004 ELEC 121 11 Collector-Emitter (Output) Loop Applying Kirchoff’s voltage law: - VCC + IC RC + VCE + IE RE = 0 Assuming that IE IC and solving for VCE: IC = VCC – VCE – (RE + RC) Solve for VE: V E = IE R E Solve for VC: VC = VCC - IC RC or VC = VCE + IE RE Solve for VB: January 2004 VB = VCC - IB RB or VB = VBE + IE RE ELEC 121 12 Voltage Divider Bias Example 1 January 2004 ELEC 121 13 Voltage Divider Bias Example 2 January 2004 ELEC 121 14 Design of CE Amplifier with Voltage Divider Bias 1. 2. 3. 4. 5. 6. 7. 8. Select a value for VCC Determine the value of from spec sheet or family of curves Select a value for ICQ Let VCE = ½ VCC (typical operation, 0.4 VCC ≤ VC ≤ 0.6 VCC ) Let VE = 0.1 VCC (for good operation, 0.1 VCC ≤ VE ≤ 0.2 VCC ) Calculate RE and RC Let R2 ≤ 0.1 RE (for this calculation, use low value for ) Calculate R1 VCC - VB R1 = R2 VB January 2004 ELEC 121 15 CE Amplifier Design • Design a Common Emitter Amplifier with Voltage Divider Bias for the following parameters: VCC = 24V IC = 5mA VE = .1VCC VC = .55VCC = 135 January 2004 ELEC 121 16 January 2004 ELEC 121 17 CE Amplifier Design January 2004 ELEC 121 18 CE Amplifier Design Voltage Divider Bias January 2004 ELEC 121 19 Voltage Divider Bias with Dual Power Supply January 2004 ELEC 121 20 Voltage Divider Bias with Dual Power Supply Input Circuit Find VTH and RTH R2 VTH1 = VCC R1 + R2 (Note VEE is negative) R1 VTH2 = VEE R1 + R2 VTH = VTH1 - VTH2 R2 VTH = VCC R1 + R2 R1 R2 RTH = R1 + R2 January 2004 ELEC 121 R1 V EE R1 + R 2 21 Voltage Divider Bias with Dual Power Supply Output Circuit -VCC + ICRC + VCE + IERE - VEE = 0 If we assume IE @ IC (β > 100) VCC + VEE - VCE RC + RE If we use IC = αIE IC = IC = January 2004 ELEC 121 VCC + VEE - VCE RC + αRE 22 Voltage Divider Bias with Dual Power Supply January 2004 ELEC 121 23 PSpice Simulation PSpice Bias Point Simulation January 2004 ELEC 121 25 PSpice Simulation for DC Bias January 2004 ELEC 121 26 PSpice Simulation for DC Sweep January 2004 ELEC 121 27 PSpice Simulation for DC Sweep The response of VC demonstrates rises rapidly towards the Q Point and then increases gradually towards a maximum value The response of VCE demonstrates that it reaches a peak value near the Q point and then decreases January 2004 ELEC 121 28 Simulation Settings for AC Sweep January 2004 ELEC 121 29 Probe Output for AC Sweep January 2004 ELEC 121 30