Lab4

advertisement

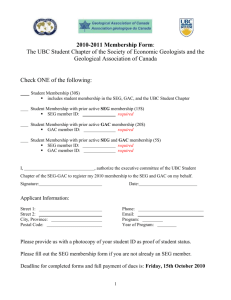

CMPEN270 – Digital Design Practice Lab4 – Implementation of a Hex to Seven Segment Converter Penn State Erie, The Behrend College 1 Purpose The purpose of this lab is to design and implement a hexadecimal to seven segment converter. The purpose of this device is to convert a 4-bit input representing a hexadecimal value into a pattern of illuminated LEDs on a 7-segment display representing the hexadecimal value. The circuit will be implemented in VHDL using a Select Signal Assignment statement. In addition, a new signal type, std_logic_vector will be introduced as a means to gather together signals into an array-like format. 2 Pre-Lab The hexadecimal-to-seven-segment or decimal-to-seven-segment decoder is a combinational circuit that converts a hexadecimal or decimal number to an appropriate code to select which segments to turn on to display the number on a seven-segment display. Each of the seven outputs of the decoder (a, b, c, d, e, f, and g) corresponds to exactly one segment in the display, as shown in Figure 1. Figure 1: Inputs and outputs from the Hex2Sevent converter. The pattern of segments to be illuminated for each digit is shown in Figure 2. For example, the hexadecimal number ‘0’ is provided as input the output would be seg(6)=1, seg(5)=1, seg(4)=1, seg(3)=1, seg(2)=1, seg(1)=1, seg(0)=0. Write the truth table for a hex2seven converter. The truth table has 4 inputs, hex(3), hex(2), hex(1), hex(0) (where hex(3) is the MSB and hex(0) is the LSB) and seven outputs seg(6), seg(5), seg(4), seg(3), seg(2), seg(1), seg(0), seg(6) is the MSB and seg(0) the LSB. Read pages 16 and 17 of the Low-Carb VHDL Tutorial posted on the class web page and write the entity description of the hex2seven converter using std_logic_vectors and the “downto” notation. Consult Section 5.4 of the Low-Carb VHDL Tutorial, Conditional Signal Assignment, and write the architecture description of the hex2seven converter. Combine the entity and architecture into one complete VHDL file and save it as hex2seven.vhd. Word process in notepad, save a copy and turn-in a hardcopy. 1 0 1 2 3 4 5 6 7 8 9 A B C D E F Figure 2: Numerical designations for 7-segment display. When the hex2seven converter is synthesized and downloaded onto the PLDT-3 board it will control the two 7-segment displays. Consult page 10 of the PLDT-3 manual posted on the class web page to complete Table 1. Turn-in a hardcopy. 7- SEGMENT DISPLAY Segment Left 7-segment CPLD pin Right 7-segment CPLD pin seg<6> seg <5> seg <4> seg <3> seg <2> seg <1> seg <0> Table 1: Pin assignments for switches and seven-segment displays on the PLTD board. 3 In-lab 1) Create a VHDL call the project lab4. 2) Add the hex2seven.vhd to the the project. 3) Add the testbench posted on ANGEL to the design. Check that the port names in the testbench match the hex2seven entity description. Read Appendix B to see how this is done. 4) Simulate your design and verify proper operation. 2 5) Create the implementation constraint file using the instructions in lab3. To test the hex2seven component a set of 4-DIP switches will be used to set the input of the hex2seven converter and the output will be sent to either of the 7-segment displays on the PLDT-3 boards. The pin locations for the two seven segment displays are given in Table 1. The inputs, hex(3 downto 0) are connected to the toggle switches S6-1, S6-2, S6-3 and S6-4, whose pin locations are p11, p7, p6 and p5, respectively. Use Appendix A to get the syntax correct for std_logic_vectors. Create an ICF file and make the pin assignments above. 6) Follow the procedure in lab3 to download the generated programming data to the PLDT-3 board. Verify the hex2seven circuit’s functionality. 4 Turn-In This is an information lab report and consequently only requires you to show that you have fully functional hex-to-seven converter. Make sure your instructor signs-off that your circuit is working. Turn in a “report” containing a title page and the following 1) Timing diagram from your testbench with the radix of hex shown in hexadecimal. 2) VHDL code for the hex2seven component Appendix A: UCF file for std_logic_vectors 1. In order to implement the hex2seven converter, the variables in the port description must be bound to the pins of the chip. This is accomplished in the implementation constraint file. In the Design panel, make sure Implementation radio button is selected. Right mouse click on the “hex2seven.vhd” icon in the Heiarchy menu and select “New Source…”. Select Implmentation constraint file and name it hex2seven. Click next and then Finish. 2. Expand the hex2seven.vhd icon in the Heiarchy. Single click click hex2seven.ucf, expand User Constraints in the Process area and double click “Edit Constraints (Text)”. 3. Add the following to the hex2seven.ucf file. Obviously, the pin locations need to be corrected according to Table 1. NET NET NET NET NET NET NET NET NET NET NET "seg<6>” "seg<5>" "seg<4>" "seg<3>" "seg<2>" "seg<1>" "seg<0>" "hex<3>" "hex<2>" "hex<1>" "hex<0>" LOC LOC LOC LOC LOC LOC LOC LOC LOC LOC LOC = = = = = = = = = = = "P11"; "P11"; "P11"; "P11"; "P11"; "P11"; "P11"; "P11"; "P11"; "P11"; "P11"; Listing 2: The ICF file for a component which uses std_logic_vectors. 3 Appendix B: Working with Testbenches In several of the labs you will need to edit the testbench in order to correct the interface between your component and the testbench or to edit the signals that the testbench is applying to your design. Figure B.1 is a graphical depection of what is going on with a testbench. The code inside the testbench creates an instance of your Hex2Seven component, in a manner this is like a subroutine call of your component. In VHDL each instance of a component must be given a unique name, its customary to call a component instantaited inside a testbench “UUT”, which stands for Unit Under Test. Figure B.1: A graphical depectition of a hex2seven component instantiated inside a testbench. Since the testbench needs to know the entity interface to your component in order to instantatite it, the Hex2Seven entity description is given in lines 9-12 of the testbench file. In addition to instantating the component, the testbench also applies inputs to the UUT. To do this inputs are drawn from a test_vector declared inside the testbench (lines 20-22) using a for-loop (lines 32-35) in the main body of the testbench. After the for loop terminates, the testbench halts itself by throwing a terminal error in lines 3840. Cosequently, you will always see “**Failure:<some message>” in the console area of the ISIM simulator when your simulation completed, even if its has done sone correctly. The expression “<some message>” is specified in line 39 of the testbench. In the coming labs you will be asked to make modifications to this testbench. If our circuit had multiple inputs, a test vector will need to be given for each. Starting in Lab 5, we will use self-checking testbenches, testbenches that have a vector which specifies the correct output for each of the inputs given in the test vectors. A self-checking testbench checks each output from the UUT to see if it matches its expected value in the testbench and halts if there are any discrepencies. 4