quiz 2 (LO3) - WordPress.com

advertisement

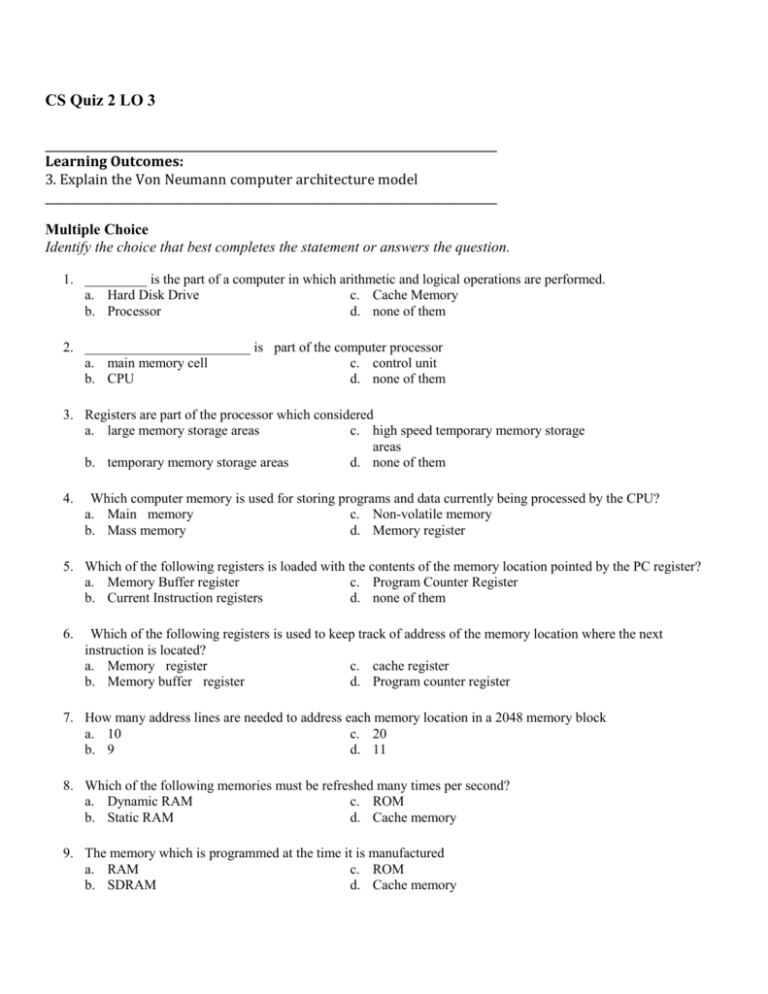

CS Quiz 2 LO 3 ____________________________________________________________ Learning Outcomes: 3. Explain the Von Neumann computer architecture model ____________________________________________________________ Multiple Choice Identify the choice that best completes the statement or answers the question. 1. _________ is the part of a computer in which arithmetic and logical operations are performed. a. Hard Disk Drive c. Cache Memory b. Processor d. none of them 2. ________________________ is part of the computer processor a. main memory cell c. control unit b. CPU d. none of them 3. Registers are part of the processor which considered a. large memory storage areas c. high speed temporary memory storage areas b. temporary memory storage areas d. none of them 4. Which computer memory is used for storing programs and data currently being processed by the CPU? a. Main memory c. Non-volatile memory b. Mass memory d. Memory register 5. Which of the following registers is loaded with the contents of the memory location pointed by the PC register? a. Memory Buffer register c. Program Counter Register b. Current Instruction registers d. none of them 6. Which of the following registers is used to keep track of address of the memory location where the next instruction is located? a. Memory register c. cache register b. Memory buffer register d. Program counter register 7. How many address lines are needed to address each memory location in a 2048 memory block a. 10 c. 20 b. 9 d. 11 8. Which of the following memories must be refreshed many times per second? a. Dynamic RAM c. ROM b. Static RAM d. Cache memory 9. The memory which is programmed at the time it is manufactured a. RAM c. ROM b. SDRAM d. Cache memory 10. One example of the Transfer of control instructions is a. JMP c. Del b. MOV d. Add 11. Branch instructions are used to a. execute an instruction b. change the program sequence. c. execute the first instruction d. execute the last instruction 12. Different components in the motherboard of a PC unit are linked together by sets of parallel electrical conducting lines. What are these lines called? a. links c. Connectors b. Conductors d. Buses 13. ___________________ is used to transfer data between peripherals and memory, or between peripherals and accumulator, Such as mov a. I/O instructions c. memory instructions b. peripherals instructions d. CPU instructions 14. ____________________ is used to perform addition, subtraction, multiplication, Increment, decrement, and logical operations. a. computational instruction c. Arithmetic instruction b. Logic instruction d. Arithmetic and Logic instruction 15. Which statement is valid? a. 65536 bytes of RAM = 64 Kbytes b. 1 MB of RAM = 2048 bytes c. 2 KB of RAM = 2000 bytes d. 1 MB of RAM = 1000 Kbytes 16. which statement is valid about RAM ? a. is called Redundant Access Memory b. volatile memory c. it starts the POST program d. non-volatile memory 17. which statement is valid about ROM ? a. is called Read Only Memory b. volatile memory c. variable memory d. fixed memory 18. which statement is valid about Cache Memory ? a. it is Read Only Memory c. It has much shorter access time than the RAM. b. located close to the main memory d. It has much longer access time than the RAM. 19. ________________ is a collection of parallel electrical lines which connect the computer components a. information Bus c. I/O Interface b. Bus System d. Serial Cable 20. L1 ( Level 1) internal cache memory is a. part of the main memory c. part of the motherboard b. longer than level2 cache memory d. built-in the CPU. CS Quiz 2 LO 3 Answer Section MULTIPLE CHOICE 1. 2. 3. 4. 5. 6. 7. 8. 9. 10. 11. 12. 13. 14. 15. 16. 17. 18. 19. 20. ANS: ANS: ANS: ANS: ANS: ANS: ANS: ANS: ANS: ANS: ANS: ANS: ANS: ANS: ANS: ANS: ANS: ANS: ANS: ANS: B C C A B D D A C A B D A D A B A C B D PTS: PTS: PTS: PTS: PTS: PTS: PTS: PTS: PTS: PTS: PTS: PTS: PTS: PTS: PTS: PTS: PTS: PTS: PTS: PTS: 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 OBJ: OBJ: OBJ: OBJ: OBJ: OBJ: OBJ: OBJ: OBJ: OBJ: OBJ: OBJ: OBJ: OBJ: OBJ: OBJ: OBJ: OBJ: OBJ: OBJ: LO 3 LO 2 LO 3 LO 3 LO 3 LO 3 LO 3 LO 3 LO 3 LO 2 LO 2 LO 2 LO 3 LO 3 LO 3 LO 3 LO 3 LO 3 LO 3 LO 3