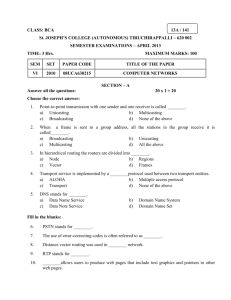

sample of a completed template

advertisement

Special Session Proposal In 5 words or less, describe the scope of the proposal (e.g., statistical timing, analog circuit simulation, physical design, low-power analysis, etc.): Session Chair Shankar Krishnamoorthy Affiliation Email Mentor Graphics Corp. Speaker Name, Job Title, and Talk Title City kathy@dac.com Affiliation State San Jose Email Country US CA City State Country Algorithms and Data Structures for Fast Routing to Handle Increasing Design Complexity Dirk Mueller, Verification Specialist Univ. Of Bonn kathy@dac.co m Boulder CO US Organizer Name(s) Affiliation Email City State Country With each subsequent technology node, routing complexity increases exponentially to handle the explosion of design rules and routing constraints. Metal layer stacks are becoming increasingly complex, with varying degrees of wire widths and interconnect parasitics becoming the norm. This session discusses design closure from a routing-centric perspective from three angles: core routing technology, guiding physical design to create a friendlier hand-off to routing, and reducing routing complexity by changing the underlying methodology. • Gyuszi Suto graduated from the Technical University of Cluj-Napoca Romania in 1987 with a Master’s Degree In Computer Engineering. He joined Intel in 1993 and has worked on 3 generations of VLSI routers as architect, main developer and mentor to new team members. For the past 6 years, he has mainly focused on physical design rule modeling of the Intel process technology. • Zhuo Li received the Ph.D. degree in computer engineering from Texas A&M University, College Station, in 2005. Dr. Li is currently a Research Staff Member in IBM Austin Research Laboratory. He received several IBM technical/invention awards including three IBM Outstanding Technical Achievement Awards, and filed 31 patents with 8 issued. He has published over 50 conference and journal papers, and is a recipient of the ASPDAC Best Paper Award in and the IEEE CAS Outstanding Young Author Award. Zhuo has spent the last seven years developing algorithms for buffering, routing, sizing, and vt optimization within IBM's design closure environment. • Dirk Mueller received his Ph.D. in 2009 from the University of Bonn for his work on global and detailed routing. Since then he has been a post-doctoral researcher at the University of Bonn working on a full blown router that has been used in the production of several VLSI chips. His expertise lies in using an non-traditional resource sharing algorithm for the global routing engine. 1. Algorithms and Data Structures for Fast Routing to Handle Increasing Design Complexity We present advanced data structures and algorithms for fast and high-quality global and detailed routing in modern technologies based on a combinatorial approximation scheme for min-max resource sharing. Detailed routing uses exact shortest path algorithms, based on a shape-based data structure for pin access and a two-level track-based data structure for long-distance connections. 2. Guiding a Physical Design Closure System to Produce Easier-to-Route Designs Physical synthesis has emerged as one of the most important tools in design closure, which starts with the logic synthesis step and generates a new optimized netlist and its layout for the final signoff process. A traditional physical synthesis tool optimizes timing/area/power with the assumption that each net can be routed with an optimal Steiner tree. However, advanced design rules, more IP and hierarchical design styles for billion-gate designs, serious buffering problems from interconnect scaling and metal layer stacks make routing a much more challenging problem. This paper discusses techniques that may relieve this problem, and guide the physical design closure system to produce not only easier to route designs, but also better timing quality. 3. Rule Agnostic Routing by Using Design Fabrics Moore's law poses a tremendous challenge on how to print and manufacture these ever-shrinking physical components, generation after process generation. One aspect of this challenge is that the process rules are exploding in complexity, directly translating into EDA tool complexity. Traditional design rules governed the spacing, overlap or alignment of any two layout objects from this set: diffusion, poly, via cut, wire, etc. Our solution relies on grids (aka. Fabrics), models the design rules on those grids and presents them to the EDA tools in such a way that it minimizes the complexity cost on the tools' side. In an ideal situation, the proposed solution can completely decouple the tools from the process rules, i.e. even if the tools don't change at all, they'll still be able to support new process nodes.