cathode strips - Physics - The Ohio State University

advertisement

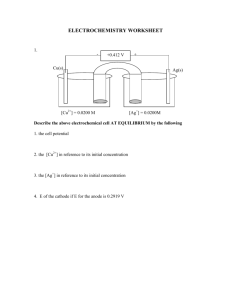

A Study of Proton-Proton Collisions at the LHC The Ohio State University - Task A.2 B.G. Bylsma, L.S. Durkin, D. Fisher, J Gilmore, J.H. Gu, D. Larson, D. Herman, T.Y.Ling, C.L. Kim, P. Nylander, V.J. Sehgal, M. Studer,C. Rush LHC Physics 1 LHC Year = 105 pb-1 Collecting and Analyzing the Physics will be difficult ... Muon Chambers will clearly play a major role in LHC experiments H -> ZZ -> CMS Detector U.S. Endcap Muon System Alabama, UC Davis, UCLA, UC Riverside, Carnegie Mellon, Fermilab, Florida, Stoney Brook, Northwestern, Ohio State, Purdue, UT Dallas, Wisconsin Endcap Cathode Strip Chambers Electronics Overview -Cathode Strip Chambers •6 layer modules •anode wire hits in azimuth direction •induced cathode strips in radial direction Environment is Demanding •Singles Rate ~100 KHz/strip •Track Rate 300 KHz/chamber - Main Functions of Electronics • generate trigger primatives for Level-1 - identify local charged track segments using both cathode and anode info • acquire precise muon information for offline analysis - cathode strips: precision azimuthal position from interpolation of induced strip charges - anode wires: precision timing; course radial position from ganged wires. Momentum Resolution BMU/EMU Only Momentum Resolution FULL CMS CSC Electronics Organization • Cathode Preamp/Shaper Asic - Ohio State • SCA ASIC - U.C. Davis • Cathode Readout Control - Ohio State • Comparitor ASIC - UCLA/CERN • Cathode PC Board - Ohio State • Anode Preamp Shaper Disc ASIC - CMU/PNPI • Anode LCT ASIC - UCLA • Anode PC Board - UCLA/CMU/PNPI • Motherboard DAQ - Ohio State • Motherboard Trigger - UCLA • DDU Board - Ohio State • Low Voltage Distribution - Wisconsin Front-End Electronics Organization 2268 cathode boards 1980 anode boards 480 motherboards Cathode Preamp/Shaper ASIC •5 pole semi-gaussian shaper •100 nsec peaking time •1 pole/1 zero tail cancellation •return to baseline in 400 nsec 4 channel prototype - AMI 1.8 u Noise • 1 % at Landau Peak -> 150m Resolution • kT limited FET amplifier, 7000 e’s at 250 pF 12 Bit Dynamic Range • 8 bits for Landau peak • 2 bits for Landau tail • 2 bits for gas gain variation Good Linearity • < 1% from 0 to 15 MIPs BUCKEYE RADIATION TEST EMU Radiation and Charged Track Backrounds Buckeye SCA ADC Comparator Control FPGA MUX Channel Li nks Front back ure 4. Latest prototype of 96-ch Cathode Front-End Board designed and prod at Ohio State in June 1999. Cathode FE Board (July 1999) • Buckeye Preamp/Shaper • Analog Storage + Controller • 12 bit ADC’s • Digital Trigger Primitives • 40 Mhz Word Transfer to Motherboard Cathode FE Board Status BUCKEYE Preamp/Shaper Finalized • Improvements for 1999: rate sensitivity 15X better latchup fixed • Final Prototype due from AMI late August • Preproduction run September/October UC Davis SCA ASIC • Improvements for 1999: Much faster 400 nsec digitization 150 nsec digitization • New design with LVDS signals due AMI late Aug. • Preproduction run September/October Trigger 1/2 Strip Generator • 2nd Iteration Completed • Presently testing • Hopefully Complete OSU SCA Controller • Uses XLINX FPGA • Design Completed Board Layout • Third Iteration works well • One more board before production Analog Storage Switch Capacitor Array (SCA) •Free Running 50 nsec Samples •Charge stored in capacitor array •sample baseline (2 samples) •2-track resolution (3 samples) Chambers are self triggered • trigger logic determines good track in 500 nsec CFEB connectors Control FPGAs JTAG CC CC B TM TM B CLCT CLCT B ALCT ALCT B Optical transceiver GLINKs FIFOs (16K,75 MHz) DAQ Motherboard 1999 • Buffer/Event Builder/optical readout for all boards: cathode, anode, trigger • 8 16K Fifos, FPGA controllers • 75 MHz Optical Link Counting House Electronics DDU Board • Prototype, Final System with onboard pentium • HP GLINK (1.5 Gbit/s, 75 Mword/s) • 33 MHz PCI into Personal Computer Cathode Integration Test Results from Integration Test Same noise at 40 MHZ as at 2.5 MHZ ! • Chamber and Electronics shipped to CERN this morning • Test Beam should start Mid August CERN Test Beam 1998 First Test of FE Electronics System: 3 96 channel anode FE Boards 3 96 channel cathode FE Boards 3 48 channel LCT trigger boards 1 trigger motherboard 1 DAQ motherboard Slow Control/JTAG Test at CERN H2 and X5 Beamlines 10-225 GeV Beam 740 GBq Cs 137 Source CERN H2 - 100 GeV , No Source CERN H2 - 100 GeV , No Source Cathode Offline Resolution Spacial Resolution: -Single Layer Strip Position (cm) - 6 layer chamber ~ 100 m Time Resolution: - single layer ~ 7 nsec CERN X5 - 100 GeV , Expected LHC Rate Conclusion Schedule is Tight US CMS Master L-1 Schedule -Start EMU installation 1/16/03 - Finish 8/29/04 EMU Electronics Schedule - Finish R&D by 12/1999 - Full pilot system 2/2000 - Construction 6/2000 Cathode Board on Schedule ! Realistic DAQ Motherboard built/tested ! Control Room DAQ boards in second design stage ! FE Board and ASIC Production Should Start on Time !