C2000 Digital Power Supply

Workshop

Texas Instruments

Technical Training

D SP

TEXAS INSTRUMENTS

TECHNOLOGY

Copyright © 2008 Texas Instruments. All rights reserved.

Workshop Outline

1.

Introduction to Digital Power

Supply Design

2.

Driving the Power Stage with PWM

Waveforms

3.

Lab: Closed-Loop Control

Tuning the Loop for Good Transient

Response

5.

Lab: PWM Generation / Open-Loop Control

Controlling the Power Stage with

Feedback

4.

Lab: Exploring the Development Environment

Lab: Tuning the Loop

Summary and Conclusion

Workshop Outline

1.

Introduction to Digital Power

Supply Design

2.

Driving the Power Stage with PWM

Waveforms

3.

Lab: Closed-Loop Control

Tuning the Loop for Good Transient

Response

5.

Lab: PWM Generation / Open-Loop Control

Controlling the Power Stage with

Feedback

4.

Lab: Exploring the Development Environment

Lab: Tuning the Loop

Summary and Conclusion

Introduction to Digital Power Supply Design

What is a Digital Power Supply?

Why use Digital Control

Techniques?

Peripherals used for Digital Power

Supply Design

Development Tools and Software

What is Digital Power?

Generic Power System Block Diagram

Vin

Controller

(Compensator)

PWM

Switches

(FETs)

LC

Network

Vout

The controller block is what differentiates between a digital

power system and a conventional analog power system

Why Digital Control Techniques?

Controller

Analog

or

Digital ??

PWM

Sensor(s)

Analog Controller

+

Digital Controller

Insensitive to environment (temp, drift,…)

S/w programmable / flexible solution

Precise / predictable behavior

Advanced control possible (non-linear, multi-variable)

Can perform multiple loops and “other” functions

High bandwidth

High resolution

Easy to understand / use

Historically lower cost

Component drift and aging / unstable

Component tolerances

Hardwired / not flexible

Limited to classical control theory only

Large parts count for complex systems

Power Elec.

Bandwidth limitations (sampling loop)

PWM frequency and resolution limits

Numerical problems (quantization, rounding,…)

AD / DA boundary (resolution, speed, cost)

CPU performance limitations

Bias supplies, interface requirements

Benefits of Digital Control

Filter

Bridge

VI

Inrush/

Hot-plug

Control

V

PFC

DC/DC

VI

8

4

5

1

V

V

I

Multi-mode

Multi-mode

Power control

control

Power

Interface

Circuit

Monitor

MCU

MCU

(MCU)

(MCU?)

Output

Traditional Analog

Power Supply

DC/DC

Current/Load

DC/DC

Current/Load

Converter

Sharing

Converter

Sharing

Control

Control

Control

Control

PFC Control

I

Supervisory

Supervisory

Housekeeping

Housekeeping

Circuits

Circuits

Multiple chips for

control

Micro-controller for

supervisory

Dedicated design

To Host

Aux P/S

Eliminate Components

Filter

Bridge

V

PFC

DC/DC

V

Output

Reduce Manufacturing Cost

Better Performance Across Corners

One Design, Multiple Supplies

Failure Prediction

Aux P/S

Digital controller enables multi-threaded applications

One Device, Multiple DC Outputs

Variable DC Output

Analog Control System

R

+

“Analog Computation”

Differential equations

e

-

C

P

(controller)

(plant)

Y

C

C2

C1

R

R

R2

R

R1

C ( s)

R2 1 R1C1s

R1 1 R2C2 s

Need to find:

R1, R2, C1, C2

Energy

Storage

Elements

L

d 3 y (t )

d 2 y (t )

dy (t )

k

k

k 0y (t ) f (t )

2

1

3

2

dt

dt

dt

Differential equations

1st, 2nd, 3rd,…order

Laplace Transform

Digital Control System

R

+

E

-

Cd

U

(controller)

D-A

P

ZOH

(plant)

Y

A-D

S&H

Difference equation

C

U (n) a2 U (n 2) a1 U (n 1)

R

b2 E (n 2) b1 E (n 1) b0 E (n)

L

where E (n) R (n) Y (n)

Need to find:

a1, a2, b0, b1, b2

Energy

Storage

Elements

d 3 y (t )

d 2 y (t )

dy (t )

k

k

k 0y (t ) f (t )

2

1

3

2

dt

dt

dt

Differential equations

1st, 2nd, 3rd,…order

OR

Laplace Transform

Z Transform

Time Sampled Systems

Digital Processor

+

A-D

Control

Law

D-A

Ref

y(t)

y(n)

t

Continuous

time signal

sample

period

T

t

Discrete

time signal

u(n)

u(t)

t

t

Processor Bandwidth

y(n)

TSAMPLE

t

Processor

Control Code

Sample Freq (=PWM)

(kHz)

100

300

500

700

1000

1500

2000

Control Code

Sample Period

(ns)

10000

3333

2000

1429

1000

667

500

Control

Time Division Multiplexing (TDM)

y(n)

TSAMPLE

t

Processor 1

Control Code (C1)

Processor 2 Control Code (C2)

Processor 3

Single CPU

Control Code (C3)

C1

C2

C3

Control Code

Control Code

Control

Control Code

C1

C2

Control

Control

C3

C1

C2

C3

Digitally Controlled Power Supply

DAC

DSC

(PWM)

ADC

0110101100

1011011101

0010100111

“High fidelity”

Translation boundary

“Plant”

System Mapping

PFC – 3ph Interleaved

F280xx

DSP

32 bit core

60~100

MHz

Vin

ADC

12 bit

(80nS)

VOUT

Ch1

Ch2

Ch16

1A

ePWM1

1B

Phase-Shifted Full Bridge

2A

ePWM2

2B

3A

ePWM3

3B

8A

ePWM8

8B

VIN

VOUT

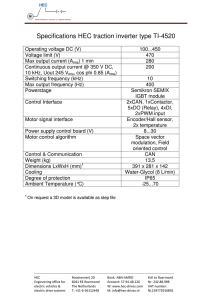

TMS320F280x

High Performance DSP (C28x

Code security

64Kw Flash

+ 1Kw OTP

18Kw

RAM

4Kw

Boot

ROM

ePWM

eCAP

Memory Bus

100 MIPs C28xTM 32-bit DSP

32x32-bit

Multiplier

RMW

Atomic

ALU

32-bit

Timers (3)

Real-Time

JTAG

Peripheral Bus

Interrupt Management

eQEP

12-bit ADC

Watchdog

Core)

100MIPS performance

Single cycle 32 x32-bit MAC (or dual 16 x16 MAC)

Very Fast Interrupt Response

Single cycle read-modified-write

Memory Sub-System

Fast program execution out of both RAM and

Flash memory

85 MIPS with Flash Acceleration Technology

100 MIPS out of RAM for time-critical code

Control Peripherals

CAN 2.0 B

I2C

SCI

32-bit

Register

File

TM

SPI

Up to 6 ePWM, 4 eCAP, and 2 eQEP

Ultra-Fast 12-bit ADC

6.25 MSPS throughput

Dual sample&holds enable simultaneous sampling

Auto Sequencer, up to 16 conversions w/o CPU

Communications Ports

GPIO

Multiple standard communication ports provide

simple interfaces to other components

Datasheet available at: http://www-s.ti.com/sc/ds/tms320f2808.pdf

Efficient 32-bit Processor Capability

Interrupt Management

TM

C28x

32x32 bit

Multiplier

32-bit DSP

RMW

Atomic

ALU

32-bit

Timers (3)

Real-Time

JTAG

32-bit

Register

File

# Instructions vs PWM

PWM freq. PWM per. Processor MIPS

(kHz)

(s)

100

150

50

20.0

2000

3000

100

10.0

1000

1500

200

5.0

500

750

250

4.0

400

600

300

3.3

333

500

500

2.0

200

300

750

1.3

133

200

1000

1.0

100

150

MIPS = Million Instruction Per Second

C28xTM DSP Core

Single-cycle 32-bit multiplier makes

computationally intensive control

algorithms more efficient

Three 32-bit timers support multiple

control loops / time bases

Single cycle read-modified-write in any

memory location and 32-bit registers

improve control algorithm efficiency

Real-time JTAG debug shortens

development cycle

Fast & flexible interrupt management

significantly reduce interrupt latency

TPWM

PWM

CPU

Control Code spare Control Code spare

Control

ePWM “DAC” Capability

ePWM

Counter

Compare

Action

Qualifier

Time-Base

Control Peripherals

Event

Trig.

& Int.

Trip

Zone

Dead

Band

PWM

Chop

EPWMxA

EPWMxB

PWM effective resolution (CPU=100MHz)

PWM

(kHz)

50

100

150

250

500

750

1000

Standard PWM

bits

%

11.0

0.05

10.0

0.10

9.4

0.15

8.6

0.25

7.6

0.50

7.1

0.75

6.6

1.00

HR-PWM

bits

%

17.0

0.0007

16.0

0.0015

15.4

0.0022

14.7

0.0037

13.7

0.0075

13.1

0.0112

12.7

0.0150

ePWM

Number of channels scalable

and resources allocated per

channel

Two independent PWM outputs

per module

Dedicated time-base timer

Two independent compare

registers

Multi-event driven waveform

Trip zones and event interrupts

F2808 offers 6 modules

Provides ePWM DAC capability

for DPS

Switching can be programmed

as Asymmetric or Symmetric

PWM

High-Resolution PWM mode

12-bit ADC Capability

ADC

Prescaler

8 ADC

Inputs

8 ADC

Inputs

Analog

MUX

Analog

MUX

S/H

A

S/H

B

Start of

Conversion

12-bit

ADC

Module

SYSCLK

Result

Registers

16 words

Auto Sequencer

Control Peripherals

Fast & Flexible

12-bit 16-Channel ADC

12.5 MSPS throughput

Dual sample/hold enable

simultaneous sampling or

sequencing sampling modes

Analog input: 0V to 3V

16 channel, multiplexed inputs

ADC Utilization:

# Channels (“Loops”) vs. PWM frequency

MSPS = 3

PWM

# Channels

(kHz)

125

24

250

12

500

6

750

4

1000

3

MSPS = 6.25

PWM

# Channels

(kHz)

125

50

250

25

500

13

750

8

1000

6

Auto Sequencer supports up to 16

conversions without CPU

intervention

Sequencer can be operated as two

independent 8-state sequencers or

as one large 16-state sequencer

Sixteen result registers (individually

addressable) to store conversion

values

Code Composer Studio

Menus or Icons

Help

CPU

Window

Project Manager:

Source & object files

File dependencies

Compiler, Assembler &

Linker build options

Full C/C++ & Assembly

Debugging:

C & ASM Source

Mixed mode

Disassembly (patch)

Set Break Points

Set Probe Points

Editor:

Structure Expansion

Status

Window

Watch Window

Graph

Window

Memory Window

Software Library Approach

CNTL

2P2Z

CNTL

3P3Z

Ref

Ref

Uout

FB

Control 2-pole / 2-zero

FB

Buck

Single

DRV

E

P

W

M

Duty

H

W

HR

Buck

Single

DRV

Uout

Control 3-pole / 3-zero

EPWMnA

Buck Single Output

IIR-FILT

2P2Z

IIR-FILT

3P3Z

f

In

Out

2nd order IIR filter

MPIL

DRV

f

In

E

P

W

M

Out

3rd order IIR filter

EPWM1A

EPWM1B

EPWM2A

Freq

Out

Offset

Sine Wave generator

HHB

DRV

Gain

Out

Offset

Duty

High precision Sine Gen

INV

SQR

Out

Inverse Square function

Duty

E

P

W

M

H

W

EPWMnA

EPWMnB

Power Factor 2-phase

Interleaved

IBM

FB

DRV

E

P

W

M

H

W

EPWMnA

In

EPWMnB

DelLL

DelRL

Half H-Bridge

PSFB

DRV

Delay

Slope

E

P

W

M

Phase

Out

Target

Soft Start and Sequencing

E

P

W

M

H

W

EPWMnA

EPWMnB

EPWM(n+1)A

EPWM(n+1)B

IBM method Full Bridge

SSartSEQ

In

EPWMnA

SGenHP1

Freq

Gain

PFC

2PHIL

DRV

Adj

H

W

Multi-Phase Interleaved

SinGen1

H

W

High Resolution Buck

EPWM2B

Duty

Duty

E

P

W

M

Llegdb

Rlegdb

H

W

EPWMnA

EPWMnB

ADC

DRV

EPWM(n+1)A

EPWM(n+1)B

Phase Shifted Full Bridge

Rslt

A

D

C

Ch0

Ch1

Ch3

Ch4

H

W

Analog-Digital Converter driver

Modular Software Architecture

“Signal Net” based module connectivity

Net1

Net2

In1A

f1

Out1

In1B

Net6

f2

Net3

In2A

In3A

Net7

In4A

In4B

f4

Out4

Net8

In4C

f5

Out2

f3

Net4

Net5

In5A

Out5

Net9

Out3

Initialization time

// pointer & Net declarations

Int *In1A, *In1B, *Out1, *In2A,...

Int Net1, Net2, Net3, Net4,...

// “connect” the modules

In1A=&Net1; In1B=&Net2; In2A=&Net3; In3A=&Net4; // inputs

Out4=&Net8; Out5=&Net9;

// outputs

Out1=&Net5; In4A=&Net5;

// Net5

Out2=&Net6; In4B=&Net6;

// Net6

Out3=&Net7; In4C=&Net7; In5A=&Net7;

// Net7

Run time - ISR

; Execute the code

f1

f2

f3

f4

f5

Peripheral Drivers

CPU dependency only:

• Math / algorithms

• Per-Unit math (0-100%)

• Independent of Hardware

Vref

(Q15)

BUCK

DRV

CNTL

2P2Z

Ref

Fdbk

Out

Duty

(Q15)

Vout

(Q15)

// pointer & Net declarations

int *CNTL_Ref1, *CNTL_Fdbk1, *CNTL_Out1;

int *BUCK_In1, *ADC_Rslt1;

int Vref, Duty, Vout;

// “connect” the modules

CNTL_Ref1 = &Vref;

CNTL_Out1 = &Duty; BUCK_In1 = &Duty;

CNTL_Fdbk1 = &Vout; ADC_Rslt1 = &Vout;

In

ADC

SEQ1

DRV

Rslt0

Depends on:

• PWM frequency

• System clock frequency

E

P

W

M

H

W

A

D

C

H

W

EPWM1A

ADC_A0

ADC_A1

ADC_A2

ADC_A3

Depends on:

• # ADC bits (10 / 12 ?)

• Unipolar, Bipolar ?

• Offset ?

Dual Buck Example

BG

ISR

Start / Stop trigger

Voltage

Controller

S-start / SEQ

Vref1

BUCK

DRV

CNTL

2P2Z

Ref

Uout

DutyCmd1

FB

Duty

Single Power Stage

E

P

W

M

H

W

Vin

EPWM1A

Vout1

DRV

Buck

400 kHz

400 kHz

ADC

DRV

Vout1

rslt0

A

D

C

H

W

Ch0

400 kHz

Voltage

Controller

S-start / SEQ

Vref2

BUCK

DRV

CNTL

2P2Z

Ref

Uout

DutyCmd2

FB

Duty

Single Power Stage

E

P

W

M

H

W

Vin

EPWM2A

400 kHz

400 kHz

ADC

DRV

Vout2

rslt0

400 kHz

A

D

C

H

W

Ch1

Vout2

DRV

Buck

Software Block Execution

BG

ISR

(400 kHz)

SStartSeq

Context Save

Comms

ADC_DRV(1)

CNTL_2P2Z(1)

Loop-1

BUCK_DRV(1)

ISR body

ADC_DRV(2)

Other....

CNTL_2P2Z(2)

Loop-2

BUCK_DRV(2)

Context

Restore

Lab1: Exploring the Development Environment

Navigate CCS features

Understand DPS library structure

Generate and visualize PWM waveforms

TI PowerTrain

PTD08A010W

10A module

Current meas.

Temp meas

Over Current Prot.

Over Current Flag

No Heat-sink needed

controlCard 2808

SW1

Phase Links

Active

Load LEDs

Volt

Meter

Workshop Outline

1.

Introduction to Digital Power

Supply Design

2.

Driving the Power Stage with PWM

Waveforms

3.

Lab: Closed-Loop Control

Tuning the Loop for Good Transient

Response

5.

Lab: PWM Generation / Open-Loop Control

Controlling the Power Stage with

Feedback

4.

Lab: Exploring the Development Environment

Lab: Tuning the Loop

Summary and Conclusion

Driving the Power Stage with PWM Waveforms

Open-Loop System Block Diagram

Generating PWM using the ePWM

Module

Power Stage Topologies and Software

Library Support

Simple Open-Loop Diagram

Watch Window

Duty1

Duty1

HR

BUCK

DRV

E

P

W

M

In

H

W

ADC

1CH

DRV

A

D

C

Single Power Stage

Vin1

EPWMnA

Duty2

Duty3

Duty1

slider

Vfdbk

Vout1

Rslt

H

W

Ch0

DRV

Vout1

Buck

Scaleable PWM Peripherals

Each peripheral module has the same structure

xSYNCI

SYNCI

EPWM1INTn

EPWM1SOC

EPWM1

Module

EPWM1AO

Resources allocated on a per channel basis

EPWM1BO

Each channel (module) supports 2

independent PWM outputs (A&B)

SYNCO

xSYNCO

# Channels easily scaleable – software reuse

SYNCI

EPWM2INTn

PIE

EPWM2SOC

EPWM2

Module

Time-base synch feature for all channels

EPWM2AO

EPWM2BO

GPIO

Mux

6 modules (12 PWM outputs) on F2808

Key features:

SYNCO

Phase & edge control

New counting modes

SYNCI

EPWM6INTn

EPWM6SOC

EPWM6

Module

EPWM6AO

Independent deadband

EPWM6BO

Flexible trip-zones

TZ1n to TZ6n

SOC

SYNCO

xSOC

ADC

VBus32

to ECAP1 module (sync in)

High frequency chopper mode

ePWM Module Block Diagram

Time-Base (TB)

TBPRD Shadow (16)

CTR=ZERO

TBPRD Active (16)

CTR=CMPB

Sync

In/Out

Select

Mux

Disabled

S0

EPWMxSYNCO

S1

CTR=PRD

TBCTL[SYNCOSEL]

16

EPWMxSYNCI

Counter

UP / DWN

(16 bit)

TBCNT

Active (16)

TBCTL[SWFSYNC]

(software forced sync)

TBCTL[CNTLDE]

CTR=ZERO

CTR_Dir

16

TBPHS Active (16)

Phase

Control

CTR=PRD

EPWMxINTn

CTR=ZERO

CTR=CMPA

Counter Compare (CC)

CTR=CMPB

Event

Trigger &

Interrupt

(ET)

EPWMxSOCA

EPWMxSOCB

CTR_Dir

16

CTR=CMPA

Action

Qualifier

(AQ)

16

CMPA Shadow (16)

16

EPWMxAO

EPWMA

CMPA Active (16)

Dead

Band

(DB)

PWM

Chopper

(PC)

Trip

Zone

(TZ)

CTR=CMPB

EPWMxBO

EPWMB

16

CMPB Active (16)

CMPB Shadow (16)

EPWMxTZINTn

TZ1n to TZ6n

CTR=ZERO

Module Sync and Phase Control

TBCTR

FFFFh

Master Module

Ext Sync In

(optional)

Master

Phase Reg

En

SyncIn

600

600

TBPRD

EPWM1A

CNT=Zero

CNT=CMPB

EPWM1B

X

1

0000

CTR=Zero

(SycnOut)

SyncOut

time

TBCTR

2

FFFFh

Phase = 120o

Slave Module

Slave

Phase Reg

En

12

SyncIn

EPWM2A

EPWM2B

CNT=CMPB

2

200

TBPHS

CNT=Zero

X

600

600

TBPRD

200

0000

SyncOut

SyncIn

time

Action Qualifier Module (AQ)

Key Features

TBCTR = Period

Multi event driven waveform generator

Events drive outputs A and B independently.

Full control on waveform polarity

Full transparency on waveform construction

S/W forcing events supported

All events can generate interrupts & ADC SOC

EPWMA

Action

Qualifier

Module

(AQ)

TBCTR = Zero

TBCTR = Compare A

TBCTR = Compare B

EPWMB

SW force

TBCTR Direction

Events

Zero

Actions

Nothing

Clear Lo

Set Hi

Toggle

Z

Z

Z

Z

T

(ZRO)

TBCTR

(Up)

equals:

CMPA

CA

CA

CA

CMPB

CB

CB

CB

P

P

P

CMPA

CA

CA

CA

P

CB

CB

CB

CB

T

(CBd)

S/W force

CA

T

(CAd)

CMPB

CBu

CMPB

SW

SW

SW

SW

T

CAu

CMPA

T

(PRD)

TBCTR

(Down)

equals:

CB

PRD

Period

T

(CBu)

Period

CA

T

(CAu)

TBCTR

ZRO

Zero

CBd

CAd

Simple Waveform Construction

TBCTR

TBPRD

value

Z

P

CB

CA

Z

P

CB

CA

Z

P

Z

P

CB

CA

Z

P

CB

CA

Z

P

EPWMA

EPWMB

TBCTR

TBPRD

value

CA

CB

CA

CB

EPWMA

EPWMB

Z

Z

Z

T

T

T

Fault Management Support

Vin

‘2808

EPWM1A

Iin

EPWM2A

TZ1

CL2

TZ3

CL1

EPWM1B

EPWM2B

ECAP1

Iin

EPWM1A

Buck #1

I1

HiZ

I2

ShutDown

TZ2

Vout1

I1

IsetCL1

Vout2

Action on

Fault

EPWM2A

Buck #2

I2

HiZ

IsetCL2

IsetSD

IsetSD

Iin

Trip Zones:

I1

IsetCL1

6 independent zones (TZ1~TZ6)

I2

IsetCL2

Force High, Low or HiZ on trip

One-time trip catastrophic failure

EPWM1A

Cycle-by-cycle current limit mode

TZ1~TZ6 can trigger interrupt

EPWM2A

Multi-Phase Interleaved (MPI)

Ext Sync In

(optional)

Master

Phase Reg

En

SyncIn

EPWM1A

CNT=Zero

CNT=CMPB

EPWM1B

X

1

Vin

SyncOut

EPWM1A

EPWM2A

EPWM3A

Slave

Phase Reg

En

SyncIn

12

EPWM2A

CNT=Zero

EPWM2B

CNT=CMPB

X

2

Vout

SyncOut

EPWM1B

Slave

Phase Reg

En

SyncIn

2

EPWM3A

CNT=Zero

CNT=CMPB

3

X

EPWM3B

SyncOut

EPWM2B

EPWM3B

Switching Requirements – MPI

P

P

P

I

I

I

P

CA

P

CB

CA

P

A

• Asymmetrical PWM case

• Complementary output

generated by dead-band unit

• CMPB triggers ADC SOC

Pulse Center

INIT-time

EPWM1A

212

P

CA

P

CB

CA

A

EPWM2A

2

• Period (1,2,3)

• CAu Action (1,2,3)

• PRD Action (1,2,3)

• Phase (2,3)

• PRD Interrupt (1)

• CBu ADC SOC (1,2,3)

• Dead-band

RUN-time

CB

A

CA

EPWM3A

P

CA

P

• CMPA (1,2,3)

• CMPB (1,2,3)

Half H-Bridge (HHB)

VDC_bus

Ext Sync In

(optional)

Master

Phase Reg

En

EPWM1A

SyncIn

EPWM1A

CNT=Zero

CNT=CMPB

1

X

EPWM1B

SyncOut

EPWM1B

VOUT

Switching Requirements – HHB

CMPA

modulation

range

CA

CB

CMPA

modulation

range

Z

CA

• Up/Down Count

• Asymmetrical PWM

• dead-band on A only

• 50 % max Modulation

(controlled by CMPA)

Z

A

EPWM1B

Z

CB

CA

Z

A

EPWM1A

DBRED

DBRED

CA

INIT-time

• ZRO Action (A,B)

• CAd Action

• CAu Action

• CBd ADC trigger

• CBd ADC trigger

• DBRED

Compare A modulation range:

0 < CMPA < ( PRD – ½ x DBRED )

RUN-time

• CMPA

• CMPB (optional)

Phase Shifted Full Bridge (PSFB)

Ext Sync In

(optional)

Master

Phase Reg

En

VOUT

SyncIn

EPWM1A

CNT=Zero

CNT=CMPB

EPWM1B

X

1

VDC_bus

EPWM1A

EPWM2A

EPWM1B

EPWM2B

SyncOut

Slave

Phase Reg

En

SyncIn

Var

EPWM2A

CNT=Zero

EPWM2B

CNT=CMPB

2

X

SyncOut

Switching Requirements – PSFB

Z

Z

Z

I

I

I

Z

CB

CA

Z

A

CB

CA

• Asymmetrical PWM

• Using dead-band module

• Phase (Φ) is the control variable

• Duty fixed at ~ 50%

• RED / FED control ZVS trans.

i.e. via resonance

• CMPB can trigger ADC SOC

Z

A

EPWM1A

RED

ZVS

transition

Power

Phase

EPWM1B

FED

ZVS

transition

2variable

Z

CB CA

Z

CB CA

A

EPWM2A

EPWM2B

Z

A

RED

Power

Phase

FED

INIT-time

• Period (1,2)

• CMPA (1,2) ~ 50%

• CAu action (1,2)

• ZRO action (1,2)

• CBu trigger for ADC SOC

RUN-time

• Phase (2) – every cycle

• FED / RED (1,2) – slow loop

Software Driver Module – PSFB

50% duty

PSFB

DRV

Net1

phase

Net2

llegdb

Net3

rlegdb

E

P

W

M

H

W

EPWM1A

EPWM1B

EPWM1A

EPWM2A

llegdb

Left leg

dead-band

EPWM2B

EPWM1B

Power

Phase

llegdb

2phase

VOUT

VDC_bus

EPWM1A

EPWM2A

EPWM2A

rlegdb

right leg

dead-band

EPWM1B

“Left leg”

EPWM2B

“Right leg”

EPWM2B

Power

Phase

rlegdb

Software Driver Module – PFC2PHIL

PFC

2PHIL

DRV

Net1

Duty

Net2

Adj

E

P

W

M

EPWM1A

H

W

EPWM1B

+/Adj

EPWM1A

VDC_bus

+/Adj

EPWM1B

EPWM1A

EPWM1B

1

Lab2: PWM Generation / Open-Loop Control

Control Buck output voltage using simple PWM

duty cycle adjustment without feedback

Use CCS watch window and slider button features

to conveniently adjust PWM duty cycle

Watch Window

Duty1

Duty1

Buck

Single

DRV

E

P

W

M

In

H

W

Buck

Single

DRV

E

P

W

M

In

H

W

Vin

EPWM-1A

Buck-1

Vout1

Buck-2

Vout2

DRV

Duty2

Duty1

Watch Window

EPWM-2A

DRV

Vout1

Duty1

slider

Duty2

slider

Vout2

Temp1

Temp2

Iout1

Iout2

Vin

ADC

Casc

Seq

CNF

A

D

C

H

W

Vout1

Vout2

Temp1

Temp2

Iout1

Iout2

Vin

Workshop Outline

1.

Introduction to Digital Power

Supply Design

2.

Driving the Power Stage with PWM

Waveforms

3.

Lab: Closed-Loop Control

Tuning the Loop for Good Transient

Response

5.

Lab: PWM Generation / Open-Loop Control

Controlling the Power Stage with

Feedback

4.

Lab: Exploring the Development Environment

Lab: Tuning the Loop

Summary and Conclusion

Controlling the Power Stage with Feedback

Closed-Loop System Block Diagram

Analog-to-Digital Converter Module

Digital Control of Power Converter

High Resolution PWM Benefits

Soft Start – Starting the Loop

The “Closed-Loop”

Control

“2P2Z”

Vset

Ref

FB

Uout

“PWM”

DRV

E

P

W

M

In

H

W

Duty

Vin

Power

Stage

“Loop”

Feedback

“ADC”

DRV

A

D

C

Rslt

H

W

Vout

ADC Module Block Diagram

Analog MUX

...

MUX

A

ADCINA7

ADCINB0

ADCINB1

Result MUX

S/H

A

S/H

MUX

...

MUX

B

ADCINB7

S/H

B

12-bit A/D

Converter

SOC

EOC

Autosequencer

MAX_CONV1

(GPIO/XINT2_ADCSOC)

Ch Sel (CONV00)

Ch Sel (CONV01)

Ch Sel (CONV02)

Ch Sel (CONV03)

...

Software

ePWM_SOC_A

ePWM_SOC_B

External Pin

RESULT0

RESULT1

Ch Sel (CONV15)

Start Sequence

Trigger

RESULT2

Result

Select

...

ADCINA0

ADCINA1

RESULT15

Digital Control of Power Converter

Vc

Vo

Power Converter

Vin

C

RL

Vref _ adc

Vo max Kd

D

Kd

Vs

PWM

Digital

Controller

U(n)

ADC

Gc(z)

E(n)

+

Vr

+

U ( z ) B0 B1 z 1 B2 z 2

Gc ( z )

E ( z ) 1 A1 z 1 A2 z 2

U (n) B0 E (n) B1E (n 1) B2 E (n 2) A1U (n 1) A2U (n 2)

Digital Control of Power Converter

Steady State Limit Cycle

Vo levels (DPWM duty

ADC levels

ratio steps)

Volt

Vc

Vref

Vs

Vs

Vc

steady state output,

limit cycle

Volt

Vref

Vo levels (DPWM duty ADC levels

ratio steps)

Vc

Vs

Vs

error bins

+0010

+0001

0000

-0001

time

error bins

+0010

+0001

0000

-0001

steady state output,

no limit cycle

time

High Frequency PWM

V

TPWM

PWM

TSysclk

VSTEP

t

t

PWM resolution = Log2 ( TPWM / TSysClk )

F2808 – SysClk = 100 MHz

PWM Freq

(kHz)

100

150

250

500

750

1000

1500

2000

Regular resolution

(bits)

(%)

10.0

0.1

9.4

0.2

8.6

0.3

7.6

0.5

7.1

0.8

6.6

1.0

6.1

1.5

5.6

2.0

High resolution

(bits)

(%)

16.0

0.002

15.4

0.002

14.7

0.004

13.7

0.008

13.1

0.011

12.7

0.015

12.1

0.023

11.7

0.030

High Resolution PWM (HRPWM)

PWM Period

Regular

PWM Step

(i.e. 10ns)

Device Clock

(i.e. 100MHz)

HRPWM divides a clock

cycle into smaller steps

called Micro Steps

(Step Size ~= 150ps)

ms

ms

ms

ms

Calibration Logic

ms

ms

Calibration Logic tracks the

number of Micro Steps per

clock to account for

variations caused by

Temp/Volt/Process

HRPWM

Micro Step (~150ps)

Significantly increases the resolution of conventionally derived digital PWM

Uses 8-bit extensions to Compare registers (CMPxHR) and Phase register

(TBPHSHR) for edge positioning control

Typically used when PWM resolution falls below ~9-10 bits which occurs at

frequencies greater than ~200 kHz (with system clock of 100 MHz)

Not all ePWM outputs support HRPWM feature (see device data manual)

Resolution Loss – Low Duty Utilization

TPWM

Max Duty

PWM

Not Utilized

t

TSYSCL (10 ns)

0.8

1

1.2

1.8

2.5

3.3

5

94%

93%

92%

91%

90%

89%

87%

93%

92%

90%

89%

88%

86%

83%

91%

90%

88%

87%

85%

83%

80%

87%

85%

82%

80%

78%

74%

70%

82%

79%

75%

72%

69%

64%

58%

76%

73%

67%

63%

59%

53%

45%

64%

58%

50%

44%

38%

29%

17%

Vin

14

12

10

9

8

7

6

Benefit of High Resolution PWM

Watch Window

Vref

HR

BUCK

DRV

Voltage

Controller

Vref

CNTL

2P2Z

Ref

FB

Uout

DutyCmd

Duty

Single Power Stage

E

P

W

M

H

W

Vin1

EPWMnA

DRV

Vout1

Buck

1 MHz

DutyCmd

1 MHz

ADC

1CH

DRV

Vout

rslt0

A

D

C

H

W

Ch0

1 MHz

HiRes PWM (150ps)

Regular PWM (10ns)

Limit cycle problem

No Limit cycle

Edge control is precise

Edge jumps around

Managing the “Closed-Loop”

Fault

Trip

Dead

Band

SSartSEQ

Delay

Slope

Out

Target

Coeff set 3

Coeff set 2

Coeff

- B2 set 1

Coeff

Coeff - B2

CoeffCoeff

- B1 - B2

Coeff - B1

CoeffCoeff

- B0 - B1

Coeff - B0

CoeffCoeff

- A2 - B0

Coeff - A2

CoeffCoeff

- A1 - A2

Coeff - A1

Coeff - A1

Vset

Control

“2P2Z”

Ref

FB

Duty

Clamp

“PWM”

DRV

E

P

W

M

In

H

W

“ADC”

DRV

A

D

C

Rslt

H

W

Duty

Uout

Open/Closed

Loop

Feedback

Simple User Interface Control

Supervisory - BG

Control Engine(s)

Fault Trip

Dead Band

Open/Closed Loop

Trip

Zone

Duty Clamp

Vset

SSartSEQ

Control

“2P2Z”

Delay

Slope

Out

Target

Coeficient

Tuning

Coeff set 3

Coeff set 2

CoeffCoeff

- B2 set 1

Coeff - B2

CoeffCoeff

- B1 - B2

Coeff - B1

CoeffCoeff

- B0 - B1

Coeff - B0

CoeffCoeff

- A2 - B0

Coeff - A2

CoeffCoeff

- A1 - A2

Coeff - A1

Coeff - A1

Vout Monitor

Duty Monitor

Ref

FB

“PWM”

DRV

E

P

W

M

In

H

W

“ADC”

DRV

A

D

C

Rslt

H

W

Duty

Uout

Voltage

Feedback

Soft-Start and Sequencing Multi Vout

Lab3: Closed-Loop Control

Regulate the Buck output by using Voltage Mode Control (VMC) with

closed-loop feedback

Soft-start and sequencing function used to ensure an “orderly”

voltage ramp-up/down

Soft-start profile and target voltage is conveniently adjusted by using

the CCS watch window and slider buttons feature

SStartSEQ

HR

BUCK

DRV

Voltage

Controller

CNTL

2P2Z

Delay

Slope

Out

Vref

Target

Ref

Uout

Duty1

Duty

Single Power Stage

E

P

W

M

H

W

Vin1

EPWMnA

FB

ADC

1CH

DRV

Watch Window

Vout1

rslt0

A

D

C

H

W

Ch0

Vsoft

Graph Window

SlewRate

DataLog

OnDelay

Mem

Buffer

Vsoft

slider

In

DRV

Vout1

Buck

Workshop Outline

1.

Introduction to Digital Power

Supply Design

2.

Driving the Power Stage with PWM

Waveforms

3.

Lab: Closed-Loop Control

Tuning the Loop for Good Transient

Response

5.

Lab: PWM Generation / Open-Loop Control

Controlling the Power Stage with

Feedback

4.

Lab: Exploring the Development Environment

Lab: Tuning the Loop

Summary and Conclusion

Tuning the Loop for Good Transient Response

Digital Power Supply Control Theory

Intuitive Loop Tuning – “Visually

without Math”

Active Load Feature of the Power EVM

Multi-Loop Control

The Digital Control System

Digital Processor

G(s)

r(t)

+

e(kT)

Controller

u(kT)

DAC

Actuator

Process

D(z)

ADC

Sensor

Advantages

Considerations

• Immunity from environmental effects

• Advanced control strategies possible

• Immunity from component errors

• Improved noise immunity

• Ability to modify and store control parameters

• Ability to implement digital communications

• System fault monitoring and diagnosis

• Data logging capability

• Ability to perform automated calibration

• Sample rate

• Quantization

• Ease of programming

• Controller design

• Cost

• Processor selection

• Requires data converters

• Numeric issues

c(t)

PID Control Review

u(t ) K e(t ) K e(t ).dt K de(t )

P

I

D dt

Gc(s)

KP = Proportional gain

KI = Integral gain

KD = Derivative gain

KP

K

G ( s) K I K s

P s

D

C

K

I

e(t)

e.dt

+

K

D

de

dt

u(t)

Usually written in “parallel” form:

G (s) K 1 1 T s

C

C T s d

i

KP = K C

KI = KC/Ti

KD = KCTd

Proportional term controls loop gain

Integral action increases low frequency gain and

reduces/eliminates steady state errors

Derivative action adds phase lead which improves

stability and increases system bandwidth

Tuning the Step Response

Performance of the control loop can be determined from the

output response to a change in load

Acceptable response might be specified in terms of...

Peak overshoot

Time to settle to within specified error band

We will adjust PID coefficients to optimise our digital controller

Loop Tuning – Good First Step

U (n) B0 E (n) B1E (n 1) B2 E (n 2) A1U (n 1) A2U (n 2)

E(n-1)

Z-1

E(n)

B0

X

E(n-2)

Z-1

B1

X

B2

U(n)

Σ

A2

X

A1

U(n-2)

X

X

Z-1

Z-1

U(n-1)

PRD-SF

X

Duty

PID – Intuitive / Interactive

We can also write the controller in transfer function form:

U(z)

B0 + B1*z-1 + B2*z-2

B0z2 + B1*z + B2

------ = ------------------------- = ---------------------E(z)

1 - z-1

z2 – z

Compare with the General 2P2Z transfer function:

U(z)

B0 + B1*z-1 + B2*z-2

B0z2 + B1*z + B2

------ = --------------------------- = ---------------------E(z)

1 + A1*z-1 + A2*z-2

z2 + A1*z + A2

We can see that PID is nothing but a special case of 2P2Z control where:

A1 = -1

and

A2 = 0

Change PID coeff. “on fly” in back-ground loop

// Coefficient init

Coef2P2Z_1[0] = Dgain * 67108;

Coef2P2Z_1[1] = (Igain - Pgain - Dgain - Dgain)*67108;

Coef2P2Z_1[2] = (Pgain + Igain + Dgain)*67108;

Coef2P2Z_1[3] = 0;

Coef2P2Z_1[4] = 67108864;

Coef2P2Z_1[5] = Dmax[1] * 67108;

Coef2P2Z_1[6] = 0x00000000;

//

//

//

//

//

//

//

B2

B1

B0

A2

A1

Clamp Hi limit (Q26)

Clamp Lo

Control Law Computation

U (n) B0 E (n) B1E (n 1) B2 E (n 2) A1U (n 1) A2U (n 2)

U(n)

DBUFF

U(n-1)

XAR7

A1

U(n-2)

A2

E(n)

B0

E(n-1)

B1

E(n-2)

B2

min

max

duty

; e(n)=Vref-Vout

MOVU

ACC,@Vref

SUBU

ACC,*XAR2++

LSL

ACC,#8

; ACC=e(n)

(Q24)

MOVL

@VCNTL_DBUFF+4,ACC

ZAPA

; Voltage control law

MOVL

XT,@VCNTL_DBUFF+8 ; XT=e(n-2)

QMPYAL

P,XT,*XAR7++

; b2*e(n-2)

MOVDL

XT,@VCNTL_DBUFF+6 ; XT=e(n-1), e(n-2)=e(n-1)

QMPYAL

P,XT,*XAR7++

; ACC=b2*e(n-2), P=b1*e(n-1)

MOVDL

XT,@VCNTL_DBUFF+4 ; XT=e(n), e(n-1)=e(n)

QMPYAL

P,XT,*XAR7++

; ACC+=b1*e(n-1), P=b0*e(n)

MOVL

XT,@VCNTL_DBUFF+2 ; XT=u(n-2)

QMPYAL

P,XT,*XAR7++

; P=a2*u(n-2)

MOVDL

XT,@VCNTL_DBUFF

; XT=u(n-1), u(n-2)=u(n-1)

QMPYAL

P,XT,*XAR7++

; ACC=a2*u(n-2)

ADDL

ACC,P

; ACC=a2*u(n-2)+a1*u(n-1)

LSL

ACC,#(23-VCNTL_QF+8)

; (Q23)

ADDL

ACC,ACC

; (Q24)

MOVL

@VCNTL_DBUFF,ACC ; ACC=u(n)

; Saturate the result [min,max]

MINL

ACC,*XAR7++

MAXL

ACC,*XAR7++

; Duty Cycle Modulation

MOVL

XT,ACC

QMPYL

P,XT,*XAR7++

;(Q0)

MOV

*XAR3++,P

Type II Controller

Lo

Vin

Vout

COMPARATOR

+

-

1

1

R2C2

Gc ( s)

R1C1 C1 C2

s s

R2C1C2

s

Co

Do

DRIVER

CONTROLLER

C1

C2

R2

R1

+

-

REF

Bode Diagram

80

70

60

R1 4.12k

Magnitude (dB)

50

R2 124k

40

30

20

10

0

C1 8.2 pF

-10

-20

0

Phase (deg)

C2 2.2nF

-45

-90

2

10

3

10

4

10

5

10

Frequency (rad/sec)

6

10

7

10

8

10

Digital Type II Controller

Lo

Vin

Vout

Do

B2 B1 z 1 B0 z 2

Gc ( z )

1 A1 z 1 A0 z 2

Co

DRIVER

DIGITAL

PROCESSOR

CONTROLLER

Bode Diagram

100

B2 9.927

B1 0.03632

Magnitude (dB)

80

60

40

20

0

-20

90

A1 1.339

45

A0 0.3391

Phase (deg)

B0 9.891

0

-45

(Tustin’s transform, Ts = 1 us)

-90

2

10

3

10

4

10

5

10

Frequency (rad/sec)

6

10

7

10

8

10

Type III Controller

Lo

Vin

Vout

COMPARATOR

+

Do

-

1

1

s

s

R

C

R

R

C

R R3

2 2

1

3

3

Gc ( s) 1

R1 R3C1 C1 C2

1

s

s s

R

C

C

R

C

2 1 2

3 3

Co

DRIVER

CONTROLLER

C1

C2

C3

R2

R3

R1

+

-

REF

Bode Diagram

40

R2 20.5k

R3 150

Magnitude (dB)

R1 4.12k

C1 0.22nF

20

10

0

45

Phase (deg)

C2 2.7nF

C3 6.8nF

30

0

-45

-90

3

10

4

10

5

10

Frequency (rad/sec)

6

10

7

10

Digital Type III Controller

Lo

Vin

Gc ( z )

1

2

Vout

Do

3

B3 B2 z B1 z B0 z

1 A2 z 1 A1 z 2 A0 z 3

Co

DRIVER

DIGITAL

PROCESSOR

CONTROLLER

B3 9.658

Bode Diagram

100

B2 9.158

B0 9.164

A2 2.128

Magnitude (dB)

B1 9.652

80

40

20

0

A1 1.397

90

45

Phase (deg)

A0 0.2689

60

0

-45

(Tustin’s transform, Ts = 1 us)

-90

3

10

4

10

5

10

Frequency (rad/sec)

6

10

7

10

2-Channel Buck EVM

TI PowerTrain

PTD08A010W

10A module

Current meas.

Temp meas

Over Current Prot.

Over Current Flag

No Heat-sink needed

Phase Links

Active

Load LEDs

Volt

Meter

2-Channel Buck EVM Schematic

Lab4: Tuning the Loop

Tune closed-loop Buck power stage for improved transient performance

using visual “trial and error” (rather than mathematical approach)

The 2-channel Buck EVM has an active load circuit when enabled by software

provides a repetitive step change in load

CCS graph window feature used to view the transient in real-time

Transient response can be modified directly until the desired improvement is

achieved by adjusting P, I, D sliders

Fault

Trip

Coefficient “tuning”

P

I

SSartSEQ

D

Vset

Delay

PID

Mapping

( 3 to 5 )

CCS or GUI

sliders

OR

Im

Pole / Zero

to Coef Map

(5 to 5)

Re

Pole / Zero

adjust GUI

Slope

Dead

Band

Out

Target

Coeff set 3

Coeff set 2

Coeff

- B2 set 1

Coeff

Coeff - B2

CoeffCoeff

- B1 - B2

Coeff - B1

CoeffCoeff

- B0 - B1

Coeff - B0

CoeffCoeff

- A2 - B0

Coeff - A2

CoeffCoeff

- A1 - A2

Coeff - A1

Coeff - A1

Control

“2P2Z”

Ref

FB

Duty

Clamp

“PWM”

DRV

E

P

W

M

In

H

W

“ADC”

DRV

A

D

C

Rslt

H

W

Duty

Uout

Open/Closed

Loop

Feedback

Graph Window

DataLog

Mem

Buffer

In

Multi-Loop Control

Supervisory BG

Loop-1 mgmt

Control Engine(s)

Coef[1]

Vref[1]

2 pole /

2 Zero

Ref

Uout

Uout[1]

ePWM

module

Duty PWM

FB

ADC

module

Controller 1

Out

Loop-2 mgmt

Coef[2]

Vref[2]

2 pole /

2 Zero

Ref

Uout

Uout[2]

ePWM

module

Duty PWM

ADC

module

Out

Loop-N mgmt

Coef[N]

Vref[N]

2 pole /

2 Zero

Ref

Uout

Uout[N]

ADC-2

ePWM

module

Duty PWM

ADC

module

Out

Diag, slow

adjustment.

PWM-2

In

FB

Controller N

ADC-1

In

FB

Controller 2

PWM-1

ADC-N

In

ADC

module

Out

PWM-N

In

ADC GenPurp

PFC (2PHIL) Software Control Flow

VpfcSetSlewed

1 kHz

SLEW

LIMIT

385 V

VpfcSet

VpfcSlewRate

In

Out

Incr

VpfcCntl

VpfcOvp

1 kHz

100 kHz

100 kHz

CNTL

2P2Z

PFC

OVP

PFC

ICMD

Ref

Out

In

CNTL

2P2Z

Out

Ref

PfcIcmd

V2

Voltage

Controller

PFC

2PHIL

DRV

100 kHz

V1

Out

Fdbk

Vmon

2

100 kHz

Out

PfcDuty

Duty

Fdbk

Adj

Vac

E

P

W

M

EPWM1A

H

W

EPWM1B

Current

Controller

Vboost

Vboost

PfcShareAdj

VpfcSet

InvVavgSqr

Ipfc

385 V

160 V

50 kHz

50 kHz

200 kHz

200 kHz

INV

SQR

FILT

BIQUAD

AC

LINE

RECT

FILT

2P2Z

50mS

Out

In

Out

In

Out

In

Out

200 kHz

Ipfc

Vboost

In

VacLine

rslt0

rslt1

rslt2

rslt3

Vavg

VacLineAvg

VacLineRect

IN0

ADC

SEQ1

DRV

VacLineFilt

rslt4

BOX

CAR

AVG

IphA

100 Hz

IpfcAvgA

PFC

ISHARE

PfcShareAdj

IphB

Out

In

BOX

CAR

AVG

Ia

Ib

Out

IpfcAvgB

Out

50 kHz

In

rslt5

IpfcPhaseA

HalfVref

50 kHz

IpfcPhaseB

A

D

C

H

W

IN1

IN2

IN3

IN4

IN5

DC-DC (ZVSFB) Software Control Flow

200 kHz

200 kHz

SLEW

LIMIT

48 V

2

VoutSet

In

VoutSlewRate

Incr

200 kHz

VoutSetSlewed

CNTL

2P2Z

Ref

Out

Out

Voltage

Controller

VdcCntl

Fdbk

Vout

I_FOLD

BACK

V

Out

phase

PhaseCntl

I

50 kHz

Rv

VoutSet

Fv

48 V

Ri

PSFB

DB

DRV

Fi

CNTL

2P2Z

0V

100ms

12 A

IoutSet

Ipri

Ref

Fdbk

Out

EPWM1A

PSFB

DRV

200 kHz

200 ns

DbAdjL

llegdb

180 ns

DbAdjR

rlegdb

EPWM1B

E

P

W

M

EPWM2A

EPWM2B

H

W

IdcCntl

200 kHz

200 kHz

Current Controller

Ipri

Ipri

rslt0

Vout

Vout

rslt1

ADC

SEQ2

DRV

A

D

C

IN0

H

W

IN1

CPU Bandwidth Utilization

MIPS = 100

# TS = 4

S. rate = 200

ISR

All

TS1

TS2

TS3

TS4

Rate

# inst / us = 100

# inst / time slice = 500

Sampling period = 5.0

Function / Activity

# Cyc

PWM (kHz) = 200

PWM (bits) = 9.0

Tot. Cyc.

292

200 kHz Context Save / Restore

32

200 kHz

200 kHz

200 kHz

200 kHz

200 kHz

200 kHz

200 kHz

200 kHz

200 kHz

200 kHz

ISR Call / Return / Ack

Time slice Mgmt

ADCSEQ2_DRV

CNTL_2P2Z 1 (V loop)

CNTL_2P2Z 2 ( I loop)

I_FOLD_BACK

ZVSFB_DRV

ADCSEQ1_DRV

FILT_2P2Z

AC_LINE_RECT

24

12

14

36

36

25

14

57

35

7

100 kHz

100 kHz

100 kHz

100 kHz

PFC_OVP

PFC_ICMD

CNTL_2P2Z 4 (I loop)

PFC2PHIL_DRV

25

30

36

26

117

50 kHz

50 kHz

100 Hz

50 kHz

1 kHz

BOXCAR_AVG 1

BOXCAR_AVG 2

PFC_ISHARE

Execution Pre-scaler(1:50)

CNTL_2P2Z 3 (V loop)

42

42

15

10

36

145

100 kHz

100 kHz

100 kHz

100 kHz

PFC_OVP

PFC_ICMD

CNTL_2P2Z 4 (I loop)

PFC2PHIL_DRV

25

30

36

26

117

FILT_BIQUAD

INV_SQR

46

78

124

50 kHz

50 kHz

FW_Isr

Stats

% Util

58%

Every ISR call

Context Save

ADCSEQ2_DRV

CNTL_2P2Z(1)

CNTL_2P2Z(2)

ZVSFB_DRV

ADCSEQ1_DRV

FILT_2P2Z

AC_LINE_RECT

% Util

Time Slice mgr

82%

#Cyc. Rem.

91

% Util

87%

#Cyc. Rem.

63

% Util

82%

#Cyc. Rem.

91

50 kHz

50 kHz

50 kHz

Function / Activity

Comms + Supervisory

+ Soft-Start + Other ?

SLEW_LIMIT 1

SLEW_LIMIT 2

TS2

TS3

TS4

PFC_OVP

PFC_ICMD

CNTL_2P2Z(4)

PFC2PHIL_DRV

BOXCAR_AVG(1)

BOXCAR_AVG(2)

PFC_ISHARE

ExecPS(1:50)

CNTL_2P2Z(3)

PFC_OVP

PFC_ICMD

CNTL_2P2Z(4)

PFC2PHIL_DRV

FILT_BIQUAD

INV_SQR

% Util

83%

# inst. Tot.Cyc.

400

434

Stats

Int Ack

Context restore

17

17

% ISR utilization =

Spare ISR MIPS =

BG loop rate (kHz) / (us) =

Return

87%

12.6

29.0

34.4

50 kHz

TS1

#Cyc. Rem.

84

BG

200 kHz

Workshop Outline

1.

Introduction to Digital Power

Supply Design

2.

Driving the Power Stage with PWM

Waveforms

3.

Lab: Closed-Loop Control

Tuning the Loop for Good Transient

Response

5.

Lab: PWM Generation / Open-Loop Control

Controlling the Power Stage with

Feedback

4.

Lab: Exploring the Development Environment

Lab: Tuning the Loop

Summary and Conclusion

Summary and Conclusion

Review of Workshop Topics and

Exercises

TI Digital Power Products

C2000 Digital Signal Controller

Family

UCD9xxx Digital Power Controller

Family

Where to Find More Information

Workshop Topics and Exercises Review

C28x DSC family provides ideal controller

for Digital Power Supply design

Scalable ePWM peripherals, ADC and fault

management support

Code Composer Studio, DPS Library and TI

Buck EVM

Controlled Buck output voltage using

PWM waveform and duty cycle without

feedback

Controlled Buck output using Voltage

Mode Control with feedback

Tuned closed-loop Buck power stage

visually using CCS features

TI Is The Right Digital Power Partner

TI solutions cover the spectrum of power applications

Flexibility

TMS320F282x

TMS320F281x

TMS320F283x

TMS320F280x

Fully Programmable,

Control Focused

UCD9111

UCD9112

UCD9220

UCD9240

Power-Optimized

Controllers

System Complexity

TI’s Digital Power Solutions Span the

Industry

Non-Isolated DC/DC POL

Isolated DC/DC &

Offline AC/DC

• UCD91xx Single-Output Digital Controller • TMS320C2000 Digital Signal Controllers

• UCD92xx Multi-Output Digital Controller

• TMS320C2000 Digital Signal Controllers

DC/AC Inverters

• TMS320C2000 32-bit controller

solutions for green energy (solar, wind,

fuel cells) and UPS battery backup

System Management

Only

• UCD9080 Power Supply Sequencer

and Monitor

C2000 Family Roadmap

F283xx

F282xx

F282xx

F281x

F281x

150

150 MHz

MHz

88 Devices

Devices

F280xx

F280xx

60 MHz

MHz

60

150ps PWM

PWM

150ps

Future

Future

C28xxx

C28xxx

300 MFLOPS

FPU, DMA

150

150 MHz

MHz

DMA

DMA

Future

C28xxx

F280x

F280xx

100

MHz

100MHz

150ps PWM

PWM

150ps

TMS320F280xx Digital Signal Controllers

High Performance Signal Processing

Code security

32-256

KB

Flash

12-36

KB

RAM

8KB

Boot

ROM

PWM

Event Capture

Memory Bus

C28xTM 32-bit DSC

32x32-bit

Multiplier

RMW

Atomic

ALU

32-bit

Timers (3)

Real-Time

JTAG

Peripheral Bus

Interrupt Management

QEP

12-bit ADC

Watchdog

Memory Sub-System

Fast program execution out of both RAM and

Flash memory

80 MIPS with Flash Acceleration Technology

100 MIPS out of RAM for time-critical code

Control Peripherals

CAN 2.0 B

I2C

SCI

32-bit

Register

File

Up to 100 MHz performance

Single cycle 32 x32-bit MAC (or dual 16 x16 MAC)

Very Fast Interrupt Response

Single cycle read-modify-write

SPI

GPIO

Up to 16 PWM channels and 4 event captures

150 ps High-Resolution PWM

Ultra-Fast 12-bit ADC

6.25 MSPS throughput

Dual sample&holds enable simultaneous sampling

Auto Sequencer, up to 16 conversions w/o CPU

Communications Ports

Multiple standard communication ports provide

simple interfaces to other components

Datasheet available at: http://www-s.ti.com/sc/ds/tms320f2808.pdf

F280xx Controller Portfolio

All Devices are 100% Hardware, Software & Pin Compatible

MHz

Flash

KB

RAM

KB

12-bit

16-ch

ADC

PWM/

Hi-Res.

CAP/

QEP

Communication

Ports

F28015

60

32

12

267ns

10/4

2/0

SPI, SCI, I2C

F28016

60

32

12

267ns

10/4

2/0

SPI, SCI, CAN, I2C

F2801-60

60

32

12

267ns

8/3

2/1

2x SPI, SCI, CAN, I2C

F2802-60

60

64

12

267ns

8/3

2/1

2x SPI, SCI, CAN, I2C

F2801

100

32

12

160ns

8/3

2/1

2x SPI, SCI, CAN, I2C

F2802

100

64

12

160ns

8/3

2/1

2x SPI, SCI, CAN, I2C

F2806

100

64

20

160ns

16/4

4/2

4x SPI, 2x SCI, CAN, I2C

F2808

100

128

36

160ns

16/4

4/2

4x SPI, 2x SCI, 2x CAN, I2C

F2809

100

256

36

80ns

16/6

4/2

4x SPI, 2x SCI, 2x CAN, I2C

F28044

100

128

20

80ns

16/16

0

SPI, SCI, I2C

TMS320

100-pin LQFP and u*BGA; Also available in -40 to 125 C and Automotive Q100

TMS320F283xx Digital Signal Controllers

High Performance Signal Processing

Code security

128-512

KB

Flash

52-68

KB

RAM

8KB

Boot

ROM

PWM

Event Capture

Memory Bus

Interrupt Management

C28xTM 32-bit DSC

32x32-bit

Multiplier

RMW

Atomic

ALU

32-bit

Timers (3)

Real-Time

JTAG

Peripheral Bus

DMA

QEP

12-bit ADC

Watchdog

Memory Sub-System

Fast program execution out of both RAM and

Flash memory

120 MIPS with Flash Acceleration Technology

150 MIPS out of RAM for time-critical code

Control Peripherals

CAN 2.0 B

I2C

SCI

32-bit

FloatingPoint Unit

Up to 150 MHz performance with 32-bit floatingpoint unit

Six-channel DMA speeds data throughput

Very Fast Interrupt Response

SPI

McBSP

Up to 16 PWM channels and 4 event captures

150 ps High-Resolution PWM

Ultra-Fast 12-bit ADC

12.5 MSPS throughput

Dual sample&holds enable simultaneous sampling

Auto Sequencer, up to 16 conversions w/o CPU

Communications Ports

Multiple standard communication ports provide

simple interfaces to other components

Datasheet available at: http://www-s.ti.com/sc/ds/tms320f28335.pdf

F283xx & F282xx Controller Portfolio

TMS320

MHz

FPU

Flash

KB

RAM

KB

12-bit

16-ch ADC

DMA

PWM/

HRPWM

CAP/

QEP

F28335

150

Yes

512

68

80 ns

Yes

18/6

6/2

F28334

150

Yes

256

68

80 ns

Yes

18/6

4/2

F28332

100

Yes

128

52

80 ns

Yes

16/4

4/2

F28235

150

No

512

68

80 ns

Yes

18/6

6/2

F28234

150

No

256

68

80 ns

Yes

18/6

4/2

F28232

100

No

128

52

80 ns

Yes

16/4

4/2

Communication

Ports

SPI, 3x SCI, I2C,

2x McBSP, 2x

CAN

SPI, 3x SCI, I2C,

2x McBSP, 2x

CAN

SPI, 2x SCI, I2C,

McBSP, 2x CAN

SPI, 3x SCI, I2C,

2x McBSP, 2x

CAN

SPI, 3x SCI, I2C,

2x McBSP, 2x

CAN

SPI, 2x SCI, I2C,

McBSP, 2x CAN

• 176-pin/ball LQFP/PBGA; 179-ball u*BGA; -40 to 125 C and Q100 in PBGA

• IQMath library provides software compatibility between floating-point and

fixed-point!

C2000 controlCARDs

F2808

F28335

only $59!

only $69!

New low cost single-board controllers perfect for initial software

development and small volume system builds.

Small form factor (9cm x 2.5cm) with standard 100-pin DIMM

interface

F28x analog I/O, digital I/O, and JTAG signals available at

DIMM interface

Isolated RS-232 interface

Single 5V power supply required

controlCARDs available for 100MHz fixed-point TMS320F2808

and 150 MHz TMS320F28335 floating-point controller

controlCARDs are available individually through TI distributors

and on the web:

Part Number: C2000-CC2808

Part Number: C2000-CC28335

Digital Power Experimenter Kit

DPEK

only $229!

DPEK includes

2-rail DC/DC EVM using TI

PowerTrain™ modules (10A)

On-board digital multi-meter and

active load for transient

response tuning

F2808 controlCARD

C2000 Applications Software CD

with example code and full

hardware details

Digital Power Supply Workshop

teaching material and lab

software

Code Composer Studio v3.3 with

code size limit of 32KB

9VDC power supply

DPEK available through TI

authorized distributors and on

the web

Part Number:C2000-DCDC2KIT

C2000 DC/DC Developer’s Kit

Only

$325!

DC/DC Kit includes

8-rail DC/DC EVM using TI

PowerTrain™ modules (10A)

F28044 controlCARD

C2000 Applications Software CD

with example code and full

hardware details

Code Composer Studio v3.3 with

code size limit of 32KB

9VDC power supply

Available through TI

authorized distributors and on

the web

Part Number:C2000-DCDC8KIT

C2000 AC/DC Developer’s Kit

Only

AC/DC Kit includes

$695!

AC/DC EVM features

AC/DC EVM with interleaved PFC

and phase-shifted full-bridge

F2808 controlCARD

C2000 Applications Software CD

with example code and full

hardware details

Code Composer Studio v3.3 with

code size limit of 32KB

12VAC in, 80W/10A output

Primary side control

Synchronous rectification

Peak current mode control

Two-phase PFC with current

balancing

AC/DC Kit available through TI

authorized distributors and on the

web

Part Number:C2000-ACDCKIT

Emulation Solutions for C2000 Controllers

BlackHawk USB2000

Controller only $299

Full CCS compatibility

Bi-Color Status LED

(red/green)

3.3/5.0 volt device I/O

Optional Isolation Adaptor for

$299

http://www.blackhawkdsp.com/Resellers.aspx

Spectrum Digital XDS510-LC

only $249

Full CCS compatibility

Supports SDFlash

programming utility

Supports XMLGUI for

interfacing to ‘C’ – provides

scripting capability

http://www.spectrumdigital.com

VisSim Graphical Programming

for C2000

www.vissim.com

Model based design for

simulation, code generation,

and interactive debugging

Efficient code generation

near hand code quality

Automatic code generation

for F28xx peripherals: ADC,

SCI, SPI, I2C, CAN, ePWM,

GPIO

High speed target

acquisition for wave form

display on PC

Watch ‘how to’ tutorials on

Visual Solutions web site

Performance

UCD9xxx Digital Power Controller Family

UCD92xx

UCD9240

4 ind outputs

64 & 80 pin

UCD9230

3 ind outputs

48 pin

UCD9220

2 ind outputs

32 pin

UCD9112

1 output, 2 phase

32 pin

UCD9111

1 output, 1 phase

32 pin

UCD91xx

Integration

Recommended Next Step:

One-day Training Course

TMS320C28x 1-Day Workshop Outline

- Workshop Introduction

- Architecture Overview

- Programming Development Environment

- Peripheral Register Header Files

- Reset, Interrupts and System Initialization

- Control Peripherals

- IQ Math Library and DSP/BIOS

Introduction to

TMS320F2808

Design and

Peripheral Training

- Flash Programming

- The Next Step…

Recommended Next Step:

Multi-day Training Course

TMS320C28x Multi-day Workshop Outline

- Architectural Overview

- Programming Development Environment

- Peripheral Register Header Files

- Reset and Interrupts

- System Initialization

- Analog-to-Digital Converter

- Control Peripherals

In-depth

TMS320F2808

Design and

Peripheral Training

- Numerical Concepts and IQmath

- Using DSP/BIOS

- System Design

- Communications

- Support Resources

For More Information . . .

Internet

Website: http://www.ti.com

FAQ: http://www-k.ext.ti.com/sc/technical_support/knowledgebase.htm

Device information

my.ti.com

Application notes

News and events

Technical documentation

Training

Enroll in Technical Training: http://www.ti.com/sc/training

USA - Product Information Center ( PIC )

Phone: 800-477-8924 or 972-644-5580

Email: support@ti.com

Information and support for all TI Semiconductor products/tools

Submit suggestions and errata for tools, silicon and documents

European Product Information Center (EPIC)

Web: http://www-k.ext.ti.com/sc/technical_support/pic/euro.htm

Phone: Language

Belgium (English)

France

Germany

Israel (English)

Italy

Netherlands (English)

Spain

Sweden (English)

United Kingdom

Finland (English)

Fax: All Languages

Number

+32 (0) 27 45 55 32

+33 (0) 1 30 70 11 64

+49 (0) 8161 80 33 11

1800 949 0107 (free phone)

800 79 11 37 (free phone)

+31 (0) 546 87 95 45

+34 902 35 40 28

+46 (0) 8587 555 22

+44 (0) 1604 66 33 99

+358(0) 9 25 17 39 48

+49 (0) 8161 80 2045

Email: epic@ti.com

Literature, Sample Requests and Analog EVM Ordering

Information, Technical and Design support for all Catalog TI

Semiconductor products/tools

Submit suggestions and errata for tools, silicon and documents

Technical Training

Organization

ti