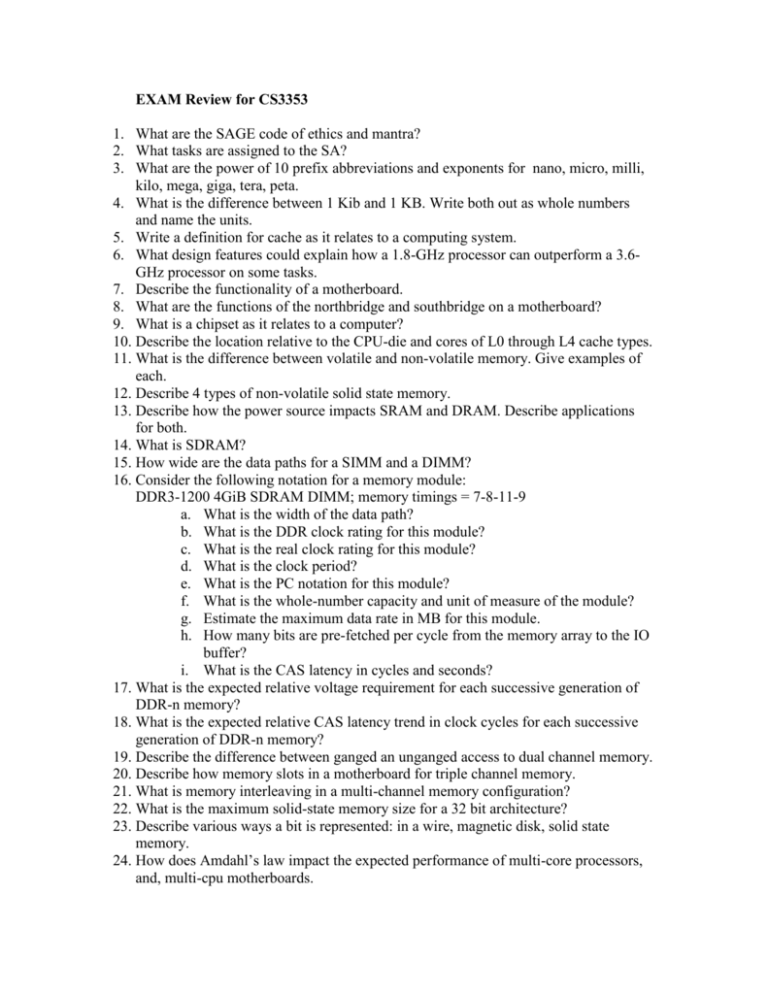

EXAM Review for CS3353

advertisement

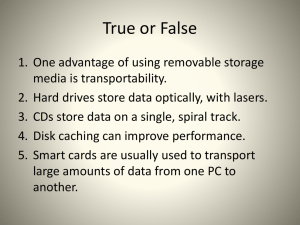

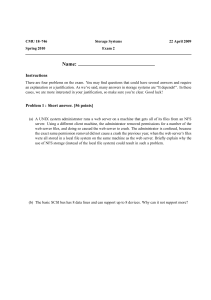

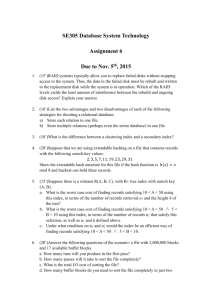

EXAM Review for CS3353 1. What are the SAGE code of ethics and mantra? 2. What tasks are assigned to the SA? 3. What are the power of 10 prefix abbreviations and exponents for nano, micro, milli, kilo, mega, giga, tera, peta. 4. What is the difference between 1 Kib and 1 KB. Write both out as whole numbers and name the units. 5. Write a definition for cache as it relates to a computing system. 6. What design features could explain how a 1.8-GHz processor can outperform a 3.6GHz processor on some tasks. 7. Describe the functionality of a motherboard. 8. What are the functions of the northbridge and southbridge on a motherboard? 9. What is a chipset as it relates to a computer? 10. Describe the location relative to the CPU-die and cores of L0 through L4 cache types. 11. What is the difference between volatile and non-volatile memory. Give examples of each. 12. Describe 4 types of non-volatile solid state memory. 13. Describe how the power source impacts SRAM and DRAM. Describe applications for both. 14. What is SDRAM? 15. How wide are the data paths for a SIMM and a DIMM? 16. Consider the following notation for a memory module: DDR3-1200 4GiB SDRAM DIMM; memory timings = 7-8-11-9 a. What is the width of the data path? b. What is the DDR clock rating for this module? c. What is the real clock rating for this module? d. What is the clock period? e. What is the PC notation for this module? f. What is the whole-number capacity and unit of measure of the module? g. Estimate the maximum data rate in MB for this module. h. How many bits are pre-fetched per cycle from the memory array to the IO buffer? i. What is the CAS latency in cycles and seconds? 17. What is the expected relative voltage requirement for each successive generation of DDR-n memory? 18. What is the expected relative CAS latency trend in clock cycles for each successive generation of DDR-n memory? 19. Describe the difference between ganged an unganged access to dual channel memory. 20. Describe how memory slots in a motherboard for triple channel memory. 21. What is memory interleaving in a multi-channel memory configuration? 22. What is the maximum solid-state memory size for a 32 bit architecture? 23. Describe various ways a bit is represented: in a wire, magnetic disk, solid state memory. 24. How does Amdahl’s law impact the expected performance of multi-core processors, and, multi-cpu motherboards. 25. A task is such that 25% of the task must be completed by one worker serially, and the remaining 75% can be divided evenly among n-workers. If it takes 10 hours for 3 workers to complete the task, how long would it take 25 workers to complete the same task? What is the maximum theoretical speedup? 26. What makes super linear speedup possible? 27. What is the impact of load-balancing on the predicted speedup calculated by Amdahl’s law. 28. If a 4-core processor has a clock rating of 2.4-GHz and it takes an average of 6 cycles per instruction, estimate the maximum MIPS rating for this processor. 29. If an operation takes 20 instructions, and the processor is rated at 3.6GHz (Dual core), what is the maximum operation rating for this processor? Assume an average of 6 cycles per instruction. 30. What principle prevents a multi-core, super-scalar CPU-die from achieving linear speed-up? 31. A CPU-die performed three benchmark tests with the following results: BM1=850MIPS, BM2=600MIPS, BM3=650MIPS. Estimate the clock speed for this cpu if there are an average of 5 cycles per instruction. 32. Discuss in detail the benefits and the drawbacks (if any) of disk partitioning. 33. What is the purpose of disk defragmentation? 34. Define the following in the context of RAID: hot swap, cold swap, warm swap, hotspare. 35. According to the article “Failure Trends in a Large Disk Population”, how are HDD SMART parameters helpful? 36. Discuss the impact of temperature on disk failure. 37. Discuss the impact of activity-level on a disk reliability. 38. Draw a diagram to illustrate disk storage topology: platter, sector, track, cylinder. 39. What is located in the first sector, first track, first cylinder of an active-bootable partition on a HDD? 40. What is the meaning of RAID? 41. Study the RAID table posted on the course web page. Describe an application for each RAID level. 42. What is RAID stripe width? 43. What is RAID stripe size? 44. How do you determine the stripe width for RAID 3? 45. How do you determine the stripe width for RAID 0 and 5? 46. What is the disk storage efficiency for RAID 0, 1, 3, 5, 6, and 1+0 in terms of n, the number of total disk drives in the array? a. Which of these RAID types use parity? b. What is the efficiency of each RAID type? c. How many disk failures can each tolerate? d. What is the minimum number of disks required to implement each? 47. Describe how parity is used to recover data from a lost drive in a RAID 3 and RAID 5 array. 48. Describe what happens during the IO operations of a RAID-5 configuration that would prevent the array from achieving its maximum theoretical IO transfer rate. 49. Describe the difference between RAID 1+0 and RAID 0+1 50. What is full-duplexing in the context of RAID-1? 51. What is the limit of IO speedup for a 3 disk RAID-3 array compared to a single disk. What is the speedup for a 3 disk RAID-5 array compared to a single disk? Is it possible to achieve the limit? If not, why not. 52. Describe how two drives can be configured as a mirrored RAID-0. 53. List the three general metrics for measuring disk performance. 54. List the major factors impacting the overall HDD IO throughput. 55. What is the order of magnitude for HDD seek times and rotational delays? 56. A SATA-2 bus has bandwidth rated @ 3 Gb/sec. An HDD is attached and is shown to perform @ 60MB/s for sequential IO. The HDD is divided into two 500GB partitions. What is the minimum time to mirror (copy all bits) from one one partition to the other? 57. Four identical HDDs each rated at 100 MB/sec are attached to the same SATA-2 bus. What is the expected total bandwidth for all four drives running simultaneously? 58. Two 80MB/sec HDDs are attached to a SATA-2 bus. Estimate the minimum amount of time it takes to copy 320GB from one drive to the other. 59. What is the difference between sequential and direct access IO? 60. How can direct access IO reach the performance level of sequential IO? 61. What is read-ahead and write-behind? 62. Draw a diagram for each network topology: bus, ring, star, mesh, compound. 63. What is TCP/IP. 64. What are the four (or five) layers of the TCP/IP protocol? 65. What are the data units used in each of the TCP/IP layers? 66. What are the address types in the four layers of the TCP/IP protocol? 67. What is an n-port bridge? 68. What is a 3-level switch? 69. What is a NIC and what is a MAC address? 70. Outline a design for a compound network that includes these physical topologies: star, bus, ring, and mesh. Explain how each part of your design includes LANs, CANs, and WANs. 71. Give a brief explanation of CSMA/CD using a network repeater. What would change if a level-2 network switch replaced the repeater? 72. Explain how a modern Ethernet LAN is implemented to avoid collisions. 73. Give a brief explanation of CSMA/CA using ACK, CTS, RTS. 74. Define AP, BSS, and ESS 75. Review all the posted in-class assignments.