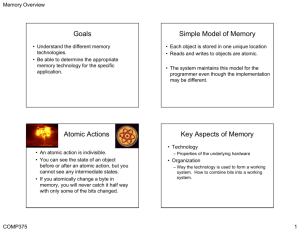

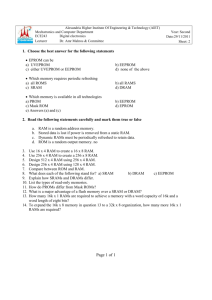

Memory Terms

advertisement

Hardware Chapter 5 – Managing Memory 1. ROM – read only memory. Stores its data on chips attached to the system board like BIOS and System BIOS 2. RAM – random access memory. Main system memory, housed on SIMM, DIMM or RIMM cards. 3. SRAM – static RAM. Does not need to be refreshed. Most SRAM is now inside the processor housing and/or on the system board. Also found on COAST modules. Faster than DRAM, but more expensive. Memory chips are made of transistors that can stay in place as long as there is voltage available. 4. DRAM – dynamic RAM. Needs to be refreshed every few milliseconds. Slower than SRAM, but cheaper. DRAM transistors are charged by capacitors, which must be recharged. 5. Refresh – to rewrite the data to the memory chip. Accomplished by the memory controller, which is part of the chip set. 6. COAST – Cache On A STick. A memory module that contains SRAM used as cache, outside of the processor housing. 7. EDO – extended data output RAM is a type of chip that improves the time to read from memory on microprocessors such as the Intel Pentium. EDO RAM was initially optimized for the 66 MHz Pentium Classic. 8. SDRAM – runs in sync with the system clock. Completes one read or write for each clock cycle. 9. DDR/DDR2 – double-data rate. Faster version of SDRAM. Completes 2 reads or writes for each clock cycle. DDR2 is faster than DDR and uses less power. 10. Rambus – data can travel on a 16- or 32-bit path. Works like a packeted network and can run at internal speeds of 800 to 1600 MHz. Housed on a RIMM; each socket on the system board must be filled. If the socket does not hold a RIMM, then it must hold a placeholder module called a C-RIMM. Rambus licenses the technology, making DDR and DDR2 more popular than RIMMs. 11. Parity – an error-checking procedure in which either every byte has an even number of ones or every byte has an odd number of ones. Every byte occupies nine rather than eight bits. A method of testing the integrity of the bits stored in RAM. 12. ECC – error-correcting code. Detects and corrects errors in one bit of the byte. Slower than non-error checking RAM (because of the extra time it takes to verify the data), and it costs more, but is more reliable. Generally used on servers. 13. caching – a method of storing data/instructions in SRAM for quick retrieval. Requires a cache controller. Under normal conditions, memory caching guesses correctly more than 90% of the time. 14. SIMM – rated by speed measured in nanoseconds. Common speeds are 60, 70, and 80 nanoseconds. Speed is a measure of access time (the time the CPU takes to receive a value in response to a request). Access time includes the time it takes to refresh the chips. The smaller the rating, the faster the chip. 15. DIMM – rated by speed and capacity. Hold from 8MB to 2GB of data. 16. Latency – number of clock cycles it takes to read or write a column or row of data. See handout on Latency. 17. Dual channel – a pair of DIMMs that are equally matched in size, speed, and features can each use a channel to simultaneously feed data to the memory controller. Each channel uses the normal 64-bit data path of the system bus, making an effective data path of 128 bits. (DDR and DDR2) 18. PC Ratings – a measure of the total bandwidth of data moving between the memory module and the CPU. PC1600 – 200 MHz PC2100 – 266 MHz PC2700 – 333 MHz PC3200 – 400 MHz PC4000 – 500 MHz PC4200 – 533 MHz PC5300 – 667 MHz 19. BEDO DRAM (Burst Extended Data Output DRAM) – a type of dynamic random access memory (DRAM) that can send data back to the computer from one read operation at the same time it is reading in the address of the next data to be sent. In addition, after reading the address, it is able to send the data back in three successive clock cycles without clock coordination (that is, the three successive outputs seem to be sent from the RAM in a sudden burst. It is faster than EDO, but never gained a market share because Intel chose not to support it. 20. SDRAM – a DIMM that is synchronized with the system clock (64 bit data path, 168 pins, 2 notches). Improved versions of SDRAM include DDR and DDR2. Use what the board supports.