http//:www.see.ed.ac.uk/ICMTS/

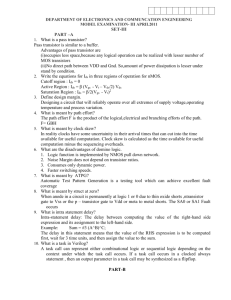

advertisement