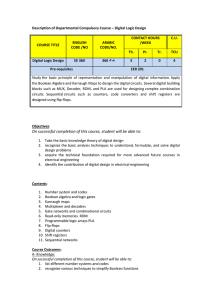

605105 Logic-Design

advertisement

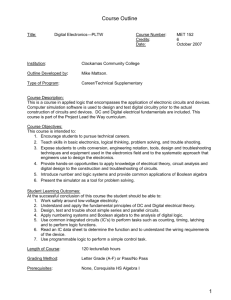

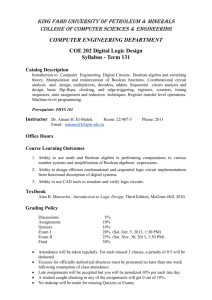

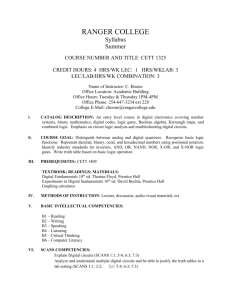

Al-Isra Private University Faculty of Science and Information Technology Department of CS Course Plan ___________________________________________________________________________________ Course No.: 605105 Course Name: Logic Design Course Website: http://elearn.iu.edu.jo 1 Course Classification: Department Compulsory (All) Time Division: 3 Lecture Hours + 1 Practical Hour Semester &Year: Second, 2014/2015 Course Description (3 credit hours, Prerequisite: 606108/ General Physics for computer science) Numbering system, computer codes, Boolean algebra and logic gates, simplification of Boolean functions, combinational logic, MSI and PLD components, synchronous clocked sequential circuits, asynchronous sequential circuits, and shift registers, memories. Course Intended Outcomes At the end of the course, students are expected to learn: Numbering systems. Boolean algebra and logic gates. Design of sequential circuits (flip-flops, counters, shift registers). Simplification of Boolean functions. Design of combinational circuits (adders, comparators, multiplexers, coder, decoders,..., etc). Memories. Course Outline Week Mon Class (Text Sec.) Oct 26 Course outline and course preview. Introductory digital concepts, Digital and analog quantities, Binary digits, logic levels, and digital waveforms, (1.1-1.3). Nov 2 Octal and Hexadecimal numbers, Binary coded Decimal (BCD), BCD addition, Signed numbers, Logic gates, The invertors, The AND, OR, and NOR gates, (2.3-2.5, 3.1, 3.2) Nov 9 Simplification using Boolean algebra, Standard forms of Boolean expressions, SOP & POS, (4.5-4.6) QUIZ More examples, K-Map with don’t care terms, BCD example, (4.9) Five variables K-Map, examples, Combinational logic, Special combinational logic circuits, Implementing combinational circuits, The universal property of NAND and NOR gates, ((4.10,5.1-5.3) Review Nov 16 Nov 23 Nov 30 Dec 7 Dec14 Return and Discussion of the First Exam Results, Functions of combinational logic, Basic Adder (half & full adders), (6.1) Active high or low enable, encoders, Decoder expansion, Wed Class (Text Sec.) Basic logic operations, Basic logic functions, Digital integrated circuits, Numbers systems, operations and codes, Decimal, Binary, binary fractions, binary arithmetic, (1.3-1.5, 2.1-2.2) The XOR and XNOR gates, Integrated circuit logic families, Boolean algebra and logic simplification, Boolean operations and expressions, Laws and rules of Boolean algebra. (3.3-3.4, 4.14.3) Boolean expressions and truth tables, The Karnaugh map, The Karnaugh map SOP minimization, (4.6- 4.9) The Karnaugh map POS minimization, (4.10) QUIZ Combinational logic circuits using universal gates, Operation with pulse waveforms, (5.4, 5.5) First Exam Parallel binary adders, look-ahead carry adders, adder/subtractor Comparators, Decoders, (6.2- 6.5) Multiplexers, multiplexer expansion, Design using multiplexers, and De- Al-Isra Private University 2 Faculty of Science and Information Technology Department of CS Course Plan ___________________________________________________________________________________ encoders, and code converters(optional), multiplexers, Parity (6.5-6.6) generators/checkers, Tutorial examples, (6.6) flip-flops operating Characteristics, Dec21 Flip-flops and related devices, Latches, SR latch, Edge-triggered flip-flop, (7.1-7.2) Flip flops with preset and clear , QUIZ Timing diagram of JK with preset & clear, (7.2-7.4) Asynchronous counter operation, Dec 28 Applications of flip flops, division by 2, Counters, Counter with decoder, (8.1-8.2) Synchronous counter operation, Up/down Design of synchronous counters, Jan 4 synchronous counters, Design of more examples, (8.3, 8.4) synchronous counters, (8.2-8.4) Second Exam Review, Jan 11 Jan 18 Jan 25 Feb 1 Feb 8 Basic semiconductor memories, ROMs, PROMs and RAMs (10.1-10.2) Memory Expansion, special types of memories, (10.1- 10.4) programmable devices, Programmable Magnetic and optical memories, logic devices (PLDs) Review Final Exam Return and Discussion of the Second Exam Results, Basic shift register functions, (9.1), Types of shift registers, (9.2) Textbook 1. Digital Fundamentals, Floyd, Prentice-Hall, 8th edition, 2003. Suggested references 1. Digital logic and Computer Design, Mano, Prentice -Hall, 4th edition,2007 2. Digital systems, principles and applications, Tocci, Ronald R.,Prentice-Hall, 10th edition 2006 Marking First Exam Second Exam Lab Activity Final Exam 15 marks (theoretical) 15 marks (theoretical) 20 marks 10 marks 40 marks Regulations 1. 2. 3. 4. 5. There will be three term exams given during this semester. The best two out of three will be considered for the First and Second Exam. This means: there will be NO makeup exams! Missing one of the two left exams means a ZERO grade will be given for that exam. There are no makeup for quizzes Attendance is mandatory and University regulations will be enforced. All Cheating incidents will be reported to the chair. The following activities are considered cheating: a. Turning in assignment that includes parts of someone else's work. b. Turning in someone else’s assignment as your own. c. Giving assignment to someone else to turn in as their own. d. Copying answers in a test or quiz. e. Taking a test or quiz for someone else. f. Having someone else take a test or quiz for you. See Student handbook for other regulations. Al-Isra Private University Faculty of Science and Information Technology Department of CS Course Plan ___________________________________________________________________________________ 3 Assignments and/or Projects Assignments / Projects Quizzes Homework Description Due Date Marking During the course. (three or more) Problem sets 60% of Mark 40% of The nature of the assignments, deadlines and Mark method of delivery will be specified by instructors throughout the course. Instructors' information Section: 1 Lecture Room: 4116 Time: 11-12:30 (Mon, Wed) Lab: 4336 Time: 12:30-2:00 (Mon, Wed) Instructor's Name: Dr. Adnan Al-Helali Office No.: 4125 Email : adnan_hadi@iu.edu.jo Office Hours: 10-11 Mon, Wed 3-4 Sun, Tue Or by appointment if necessary Important: The content of this syllabus may not be changed during the current semester Instructor Council Chair Activity Activity