Storage Elements

advertisement

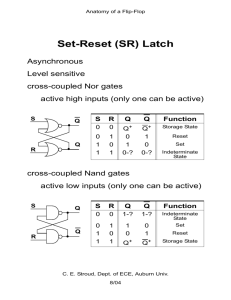

Storage Elements u The use of combinational logic permits a computer to make arbitrarily difficult decisions (realize an arbitrary truth table). u However, to have the computational capability of a (Universal) Turing machine, it must also be able to ÒmemorizeÓ (store) and recall information. u What do storage structures look like? Preliminaries u What does this circuit do? Q Q+ = Q' WhatÕs this? ItÕs an oscillator. Q Q' u How about this? Q+ Q nn Q+ Q Q+ = Q'' = Q This circuit has 2 stable states: Q = 0, Q = 1 R-S (Reset-Set) Latch u Logically, an R-S latch stores one of two values, i.e. it has two (stable) memory states: ¥ Q = 0 : The reset state ¥ Q = 1: The set state u There are two inputs R and S, which are able to reset and set the memory state, respectively. u There are two outputs Q and Q', which convey the latchÕs state and its complement, respectively. R-S Latch Implementation (with NOR gates) u Using only NOR gates, an R-S latch can be implemented as follows: S u Q' l R l Q Note: Although only combinational gates are used here, this is not a combinational logic structure -- itÕs behavior depends on itÕs STATE, i.e. on past inputs R-S Latch Behavior (NOR Implementation) S Q Q' R l Q+ l u Q u Q+ = (R OR (S OR Q)') ' u If R=S=0, then Q+ =(Q')', i.e. Q remains ÒquiescentÓ i.e. unchanged from whatever it was before: LATCH REMEMBERS. u If R=1 and S=0, then Q+=0 and Q' =1: LATCH RESETS. If S=1 and R=0, then Q' =0 and Q+= 1: LATCH SETS. If S=1 and R=1, then Q+= Q' =0!!! BUT should NOT try to Set and Reset the Latch at the same time. R-S Latch Implementation (with NAND gates) u An R-S latch can also be implemented using only NAND gates: S' Q' Q R' l l u Note that when S' = 0 it forces Q =1. Although the textbook calls this input S, it is better to name an input for what it does when it is 1 (e.g. S' is ÒdonÕt setÓ, or Òactive low setÓ). R-S Latch Behavior (in general) u u u u The input (R,S) = (0,0) [or (R', S' = (1,1)] is called the quiescent input: it leaves the Q in its current (stable) state. A momentary reset input (R,S) = (1,0) [(R', S' = (0,1)] results in a transition to the reset state Q=0 (Q will remain 0 during further quiescent and reset inputs, i.e. until the next set input). A momentary set input (R,S) = (0,1) [ (R',S') = (1,0)] results in a transition to the set state Q=1 (Q will remain 1 until the next reset input). The input (R,S) = (1,1) [ (R',S') = (0,0)] is not allowed. A Gated D Latch, Constructed from an R-S Latch ' Q Q' ' u Note: S = WE AND D, R=WE AND D' uWhat happens when WE = 0? uWhen WE = 1? Gated D Latch (summary of behavior) u Latch that have a means of controlling when the input(s) can effect a possible state change are called gated latches. u In particular, a gated D latch is a storage element with data input D and control input WE (write enable); it stores the value of D whenever WE is momentarily asserted. u Namely, Q = D while WE = 1 and Q remains quiescent otherwise. Finite State Machines u u u u FSMs (or Sequential Machines) can be built from gates and latches (or Flip-Flops: like latches but with special timing and triggering, using clocks). These have a finite number of STATEs. OUTPUT is some combinational function of CURRENT INPUT and CURRENT STATE. NEXT STATE is some combinational function of CURRENT INPUT and CURRENT STATE. Registers u An n-bit register is a logic structure that stores n bits . u It has n data inputs, a control input WE, and n outputs. u At the ÒsmallÓ extreme, a gated D latch serves as a 1-bit register. u An n-bit register can be realized by n gated D latches. A 4-Bit Register Notation for a Sequence of Bits u u u Q[3:0] can be used to denote the sequence of bits Q3, Q2, Q1, Q0 stored in this 4-bit register, where Q is the name of the source register and each bit assigned its own bit number. Generally, the output (state) bits of an n-bit register, A, are called A[n-1:0], where An-1 is the leftmost bit (MSB), and A0 is the rightmost (LSBð). Subsequence (field) notation: e.g. A[5:3] denotes A5 ,A4 ,A3 Memory u u u u A Register typically stores the value of an operand (e.g. a 32-bit word) for various arithmetic and logical operations. A memory (RAM, ROM,É) has a much larger storage capacity, today often consisting of millions of memory locations, each having a unique identifier called an address. The set of all such identifiable locations is referred to as the memoryÕs address space. The number of bits stored in each location is the memoryÕs addressability (or Òaddressible unitÓ) - e.g. 8 bits per location is Òbyte addressability.Ó Address Space & Addressability u If an address has n-bits, then the address space has size 2n locations. e.g. n=10 gives 210 =1024 locations (Ò1KÓ) n=20 gives 220 =1,048,576 locations (Ò1MÓ) u If the addressability is 8 bits, then the memory is byte-addressable, a byte being 8 bits. u A 16 MB memory thus refers to a byteaddressable memory with (approximately) 16 million locations. How many locations? How many address bits? A 22 by 3-Bit Memory (4 locations with 3-Bit addressability)