Midterm Data Sheets 2013

advertisement

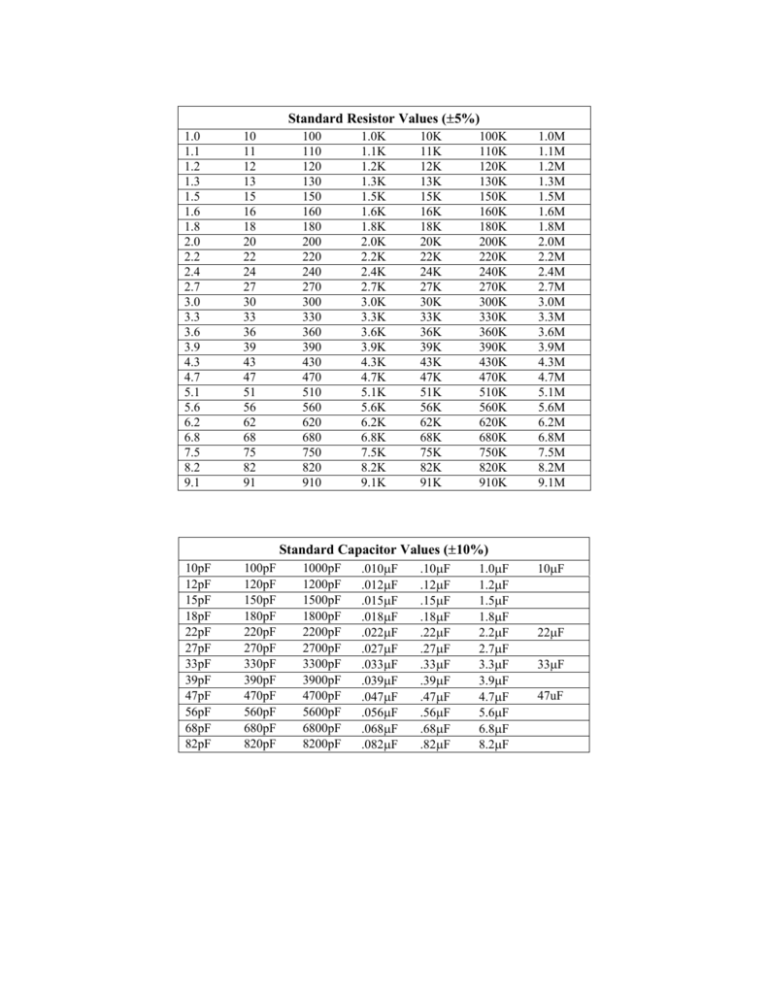

Standard Resistor Values (±

± 5%)

1.0

1.1

1.2

1.3

1.5

1.6

1.8

2.0

2.2

2.4

2.7

3.0

3.3

3.6

3.9

4.3

4.7

5.1

5.6

6.2

6.8

7.5

8.2

9.1

10

11

12

13

15

16

18

20

22

24

27

30

33

36

39

43

47

51

56

62

68

75

82

91

100

110

120

130

150

160

180

200

220

240

270

300

330

360

390

430

470

510

560

620

680

750

820

910

1.0K

1.1K

1.2K

1.3K

1.5K

1.6K

1.8K

2.0K

2.2K

2.4K

2.7K

3.0K

3.3K

3.6K

3.9K

4.3K

4.7K

5.1K

5.6K

6.2K

6.8K

7.5K

8.2K

9.1K

10K

11K

12K

13K

15K

16K

18K

20K

22K

24K

27K

30K

33K

36K

39K

43K

47K

51K

56K

62K

68K

75K

82K

91K

100K

110K

120K

130K

150K

160K

180K

200K

220K

240K

270K

300K

330K

360K

390K

430K

470K

510K

560K

620K

680K

750K

820K

910K

1.0M

1.1M

1.2M

1.3M

1.5M

1.6M

1.8M

2.0M

2.2M

2.4M

2.7M

3.0M

3.3M

3.6M

3.9M

4.3M

4.7M

5.1M

5.6M

6.2M

6.8M

7.5M

8.2M

9.1M

Standard Capacitor Values (±

± 10%)

10pF

12pF

15pF

18pF

22pF

27pF

33pF

39pF

47pF

56pF

68pF

82pF

100pF

120pF

150pF

180pF

220pF

270pF

330pF

390pF

470pF

560pF

680pF

820pF

1000pF

1200pF

1500pF

1800pF

2200pF

2700pF

3300pF

3900pF

4700pF

5600pF

6800pF

8200pF

.010µF

.012µF

.015µF

.018µF

.022µF

.027µF

.033µF

.039µF

.047µF

.056µF

.068µF

.082µF

.10µF

.12µF

.15µF

.18µF

.22µF

.27µF

.33µF

.39µF

.47µF

.56µF

.68µF

.82µF

1.0µF

1.2µF

1.5µF

1.8µF

2.2µF

2.7µF

3.3µF

3.9µF

4.7µF

5.6µF

6.8µF

8.2µF

10µF

22µF

33µF

47uF

LM139/LM239/LM339/LM2901/LM3302

Low Power Low Offset Voltage Quad Comparators

General Description

Features

The LM139 series consists of four independent precision

voltage comparators with an offset voltage specification as

low as 2 mV max for all four comparators. These were

designed specifically to operate from a single power supply

over a wide range of voltages. Operation from split power

supplies is also possible and the low power supply current

drain is independent of the magnitude of the power supply

voltage. These comparators also have a unique characteristic in that the input common-mode voltage range includes

ground, even though operated from a single power supply

voltage.

n

n

n

n

n

Application areas include limit comparators, simple analog to

digital converters; pulse, squarewave and time delay generators; wide range VCO; MOS clock timers; multivibrators

and high voltage digital logic gates. The LM139 series was

designed to directly interface with TTL and CMOS. When

operated from both plus and minus power supplies, they will

directly interface with MOS logic — where the low power

drain of the LM339 is a distinct advantage over standard

comparators.

n

n

n

n

n

n

n

Wide supply voltage range

LM139/139A Series

2 to 36 VDC or ± 1 to ± 18 VDC

LM2901:

2 to 36 VDC or ± 1 to ± 18 VDC

LM3302:

2 to 28 VDC or ± 1 to ± 14 VDC

Very low supply current drain (0.8 mA) — independent

of supply voltage

Low input biasing current:

25 nA

± 5 nA

Low input offset current:

± 3 mV

Offset voltage:

Input common-mode voltage range includes GND

Differential input voltage range equal to the power

supply voltage

Low output saturation voltage:

250 mV at 4 mA

Output voltage compatible with TTL, DTL, ECL, MOS

and CMOS logic systems

Advantages

n

n

n

n

n

n

High precision comparators

Reduced VOS drift over temperature

Eliminates need for dual supplies

Allows sensing near GND

Compatible with all forms of logic

Power drain suitable for battery operation

One-Shot Multivibrator with Input

Lock Out

00570612

© 2004 National Semiconductor Corporation

DS005706

www.national.com

LM139/LM239/LM339/LM2901/LM3302 Low Power Low Offset Voltage Quad Comparators

March 2004

LM139/LM239/LM339/LM2901/LM3302

Distributors for availability and specifications.

Absolute Maximum Ratings (Note 10)

If Military/Aerospace specified devices are required,

please contact the National Semiconductor Sales Office/

LM139/LM239/LM339

LM139A/LM239A/LM339A

LM3302

LM2901

Supply Voltage, V+

36 VDC or ± 18 VDC

28 VDC or ± 14 VDC

36 VDC

28 VDC

−0.3 VDC to +36 VDC

−0.3 VDC to +28 VDC

50 mA

50 mA

Molded DIP

1050 mW

1050 mW

Cavity DIP

1190 mW

Small Outline Package

760 mW

Differential Input Voltage (Note 8)

Input Voltage

Input Current (VIN < −0.3 VDC),

(Note 3)

Power Dissipation (Note 1)

Output Short-Circuit to GND,

(Note 2)

Storage Temperature Range

Continuous

Continuous

−65˚C to +150˚C

−65˚C to +150˚C

Lead Temperature

(Soldering, 10 seconds)

260˚C

260˚C

Operating Temperature Range

−40˚C to +85˚C

LM339/LM339A

0˚C to +70˚C

LM239/LM239A

−25˚C to +85˚C

LM2901

−40˚C to +85˚C

LM139/LM139A

−55˚C to +125˚C

Soldering Information

Dual-In-Line Package

Soldering (10 seconds)

260˚C

260˚C

Vapor Phase (60 seconds)

215˚C

215˚C

Infrared (15 seconds)

220˚C

220˚C

Small Outline Package

See AN-450 “Surface Mounting Methods and Their Effect on Product Reliability” for other methods of

soldering surface mount devices.

ESD rating (1.5 kΩ in series with 100 pF)

600V

600V

Electrical Characteristics

(V+=5 VDC, TA = 25˚C, unless otherwise stated)

Parameter

Conditions

LM139A

Min Typ

LM239A, LM339A

Max

Min

Typ

LM139

Max

Min Typ

Units

Max

Input Offset Voltage

(Note 9)

1.0

2.0

1.0

2.0

2.0

5.0

mVDC

Input Bias Current

IIN(+) or IIN(−) with Output in

25

100

25

250

25

100

nADC

25

5.0

50

3.0

25

nADC

Linear Range, (Note 5), VCM=0V

Input Offset Current

Input Common-Mode

Voltage Range

Supply Current

IIN(+)−IIN(−), VCM=0V

+

V =30 VDC (LM3302,

3.0

+

0

V −1.5

+

0

V −1.5

+

0

V −1.5

VDC

V+ = 28 VDC) (Note 6)

RL = ∞ on all Comparators,

0.8

2.0

RL = ∞, V+ = 36V,

0.8

2.0

0.8

2.0

mADC

1.0

2.5

1.0

2.5

mADC

(LM3302, V+ = 28 VDC)

Voltage Gain

RL≥15 kΩ, V+ = 15 VDC

50

200

50

200

50

200

V/mV

300

ns

VO = 1 VDC to 11 VDC

Large Signal

Response Time

www.national.com

VIN = TTL Logic Swing, VREF =

300

1.4 VDC, VRL = 5 VDC,

2

300

(Continued)

(V+=5 VDC, TA = 25˚C, unless otherwise stated)

Parameter

Conditions

LM139A

Min Typ

LM239A, LM339A

Max

Min

Typ

Max

LM139

Min Typ

Units

Max

RL = 5.1 kΩ

Response Time

VRL = 5 VDC, RL = 5.1 kΩ,

Output Sink Current

VIN(−) = 1 VDC, VIN(+) = 0,

1.3

1.3

1.3

µs

16

mADC

(Note 7)

6.0

16

6.0

16

6.0

VO ≤ 1.5 VDC

Saturation Voltage

VIN(−) = 1 VDC, VIN(+) = 0,

250

400

250

400

250

400

mVDC

ISINK ≤ 4 mA

Output Leakage

Current

VIN(+) = 1 VDC,VIN(−) = 0,

0.1

0.1

0.1

nADC

VO = 5 VDC

Electrical Characteristics

(V+ = 5 VDC, TA = 25˚C, unless otherwise stated)

Parameter

Conditions

LM239, LM339

Min

Typ

LM2901

Max

Min Typ

LM3302

Max

Min Typ

Units

Max

Input Offset Voltage

(Note 9)

2.0

5.0

2.0

7.0

3

20

mVDC

Input Bias Current

IIN(+) or IIN(−) with Output in

25

250

25

250

25

500

nADC

Input Offset Current

IIN(+)−IIN(−), VCM = 0V

Input Common-Mode

V+ = 30 VDC (LM3302,

Linear Range, (Note 5), VCM=0V

Voltage Range

Supply Current

5.0

50

V+−1.5

0

5

50

V+−1.5

0

3

0

100

nADC

V+−1.5

VDC

+

V = 28 VDC) (Note 6)

RL = ∞ on all Comparators,

0.8

2.0

0.8

2.0

0.8

2.0

mADC

RL = ∞, V+ = 36V,

1.0

2.5

1.0

2.5

1.0

2.5

mADC

(LM3302, V+ = 28 VDC)

Voltage Gain

RL ≥ 15 kΩ, V+ = 15 VDC

50

200

25

100

2

30

V/mV

VO = 1 VDC to 11 VDC

Large Signal

Response Time

VIN = TTL Logic Swing, VREF =

300

300

300

ns

1.3

1.3

1.3

µs

16

mADC

1.4 VDC, VRL = 5 VDC,

RL = 5.1 kΩ,

Response Time

VRL = 5 VDC, RL = 5.1 kΩ,

Output Sink Current

VIN(−)= 1 VDC, VIN(+) = 0,

(Note 7)

6.0

16

6.0

16

6.0

VO ≤ 1.5 VDC

Saturation Voltage

VIN(−) = 1 VDC, VIN(+) = 0,

Output Leakage

VIN(+) = 1 VDC,VIN(−) = 0,

250

400

250

400

250

500

mVDC

ISINK ≤ 4 mA

Current

0.1

0.1

0.1

nADC

LM139

Units

VO = 5 VDC

Electrical Characteristics

(V+ = 5.0 VDC, (Note 4))

Parameter

Conditions

LM139A

Min Typ

Max

LM239A, LM339A

Min Typ

Max

Min Typ

Max

Input Offset Voltage

(Note 9)

4.0

4.0

9.0

Input Offset Current

IIN(+)−IIN(−), VCM = 0V

100

150

100

mVDC

nADC

Input Bias Current

IIN(+) or IIN(−) with Output in

300

400

300

nADC

Input Common-Mode

V+=30 VDC (LM3302,

V+−2.0

VDC

Voltage Range

V+ = 28 VDC) (Note 6)

Linear Range, VCM = 0V (Note 5)

0

3

V+−2.0

0

V+−2.0

0

www.national.com

LM139/LM239/LM339/LM2901/LM3302

Electrical Characteristics

LM139/LM239/LM339/LM2901/LM3302

Electrical Characteristics

(Continued)

(V+ = 5.0 VDC, (Note 4))

Parameter

Conditions

LM139A

Min Typ

Saturation Voltage

VIN(−)=1 VDC, VIN(+) = 0,

LM239A, LM339A

Max

Min Typ

Max

LM139

Min Typ

Units

Max

700

700

700

mVDC

1.0

1.0

1.0

µADC

36

36

36

VDC

ISINK ≤ 4 mA

Output Leakage Current

VIN(+)

=

1 VDC, VIN(−) = 0,

VO = 30 VDC, (LM3302,

VO = 28 VDC)

Keep all VIN’s ≥ 0 VDC (or V−,

Differential Input Voltage

if used), (Note 8)

Electrical Characteristics

(V+ = 5.0 VDC, (Note 4))

Parameter

Conditions

LM239, LM339

Min Typ

Max

LM2901

Min Typ

LM3302

Max

Min Typ

Units

Max

Input Offset Voltage

(Note 9)

9.0

9

15

40

Input Offset Current

IIN(+)−IIN(−), VCM = 0V

150

50

200

300

mVDC

nADC

Input Bias Current

IIN(+) or IIN(−) with Output in

400

200

500

1000

nADC

V+−2.0

VDC

700

700

mVDC

1.0

1.0

1.0

µADC

36

36

28

VDC

Linear Range, VCM = 0V (Note 5)

Input Common-Mode

V+ = 30 VDC (LM3302, V+ = 28 VDC)

Voltage Range

(Note 6)

Saturation Voltage

VIN(−) = 1 VDC, VIN(+) = 0,

V+−2.0

700

V+−2.0

0

400

0

ISINK ≤ 4 mA

Output Leakage Current VIN(+)

=

1 VDC, VIN(−) = 0,

VO = 30 VDC, (LM3302, V

O

= 28 VDC)

Differential Input Voltage Keep all VIN’s ≥ 0 VDC (or V−,

if used), (Note 8)

Note 1: For operating at high temperatures, the LM339/LM339A, LM2901, LM3302 must be derated based on a 125˚C maximum junction temperature and a

thermal resistance of 95˚C/W which applies for the device soldered in a printed circuit board, operating in a still air ambient. The LM239 and LM139 must be derated

based on a 150˚C maximum junction temperature. The low bias dissipation and the “ON-OFF” characteristic of the outputs keeps the chip dissipation very small

(PD≤100 mW), provided the output transistors are allowed to saturate.

Note 2: Short circuits from the output to V+ can cause excessive heating and eventual destruction. When considering short circuits to ground, the maximum output

current is approximately 20 mA independent of the magnitude of V+.

Note 3: This input current will only exist when the voltage at any of the input leads is driven negative. It is due to the collector-base junction of the input PNP

transistors becoming forward biased and thereby acting as input diode clamps. In addition to this diode action, there is also lateral NPN parasitic transistor action

on the IC chip. This transistor action can cause the output voltages of the comparators to go to the V+ voltage level (or to ground for a large overdrive) for the time

duration that an input is driven negative. This is not destructive and normal output states will re-establish when the input voltage, which was negative, again returns

to a value greater than −0.3 VDC (at 25˚)C.

Note 4: These specifications are limited to −55˚C ≤ TA ≤ +125˚C, for the LM139/LM139A. With the LM239/LM239A, all temperature specifications are limited to

−25˚C ≤ TA ≤ +85˚C, the LM339/LM339A temperature specifications are limited to 0˚C ≤ TA ≤ +70˚C, and the LM2901, LM3302 temperature range is −40˚C ≤ TA

≤ +85˚C.

Note 5: The direction of the input current is out of the IC due to the PNP input stage. This current is essentially constant, independent of the state of the output so

no loading change exists on the reference or input lines.

Note 6: The input common-mode voltage or either input signal voltage should not be allowed to go negative by more than 0.3V. The upper end of the common-mode

voltage range is V+ −1.5V at 25˚C, but either or both inputs can go to +30 VDC without damage (25V for LM3302), independent of the magnitude of V+.

Note 7: The response time specified is a 100 mV input step with 5 mV overdrive. For larger overdrive signals 300 ns can be obtained, see typical performance

characteristics section.

Note 8: Positive excursions of input voltage may exceed the power supply level. As long as the other voltage remains within the common-mode range, the

comparator will provide a proper output state. The low input voltage state must not be less than −0.3 VDC (or 0.3 VDCbelow the magnitude of the negative power

supply, if used) (at 25˚C).

Note 9: At output switch point, VO.1.4 VDC, RS = 0Ω with V+ from 5 VDC to 30 VDC; and over the full input common-mode range (0 VDC to V+ −1.5 VDC), at 25˚C.

For LM3302, V+ from 5 VDC to 28 VDC.

Note 10: Refer to RETS139AX for LM139A military specifications and to RETS139X for LM139 military specifications.

www.national.com

4

MM54HC05/MM74HC05

Hex Inverter (Open Drain)

General Description

Features

The MM54HC05/MM74HC05 are logic functions fabricated

by using advanced silicon-gate CMOS technology, which

provides the inherent benefits of CMOSÐlow quiescent

power and wide power supply range. These devices are

also functionally and pin-out compatible with standard

DM54LS/DM74LS logic families. The MM54HC05/

MM74HC05 open drain Hex Inverter requires the addition of

an external resistor to perform a wire-NOR function.

All inputs are protected from static discharge damage by

internal diodes to VCC and ground.

Y

Y

Y

Y

Open drain for wire-NOR function

Fanout of 10 LS-TTL loads

Typical propagation delays:

tPZL (with 1 kX resistor) 8 ns

tPLZ (with 1 kX resistor) 13 ns

Low input current: 1 mA maximum

Connection Diagram

Dual-In-Line Package

TL/F/9388 – 1

Top View

Order Number MM54HC05 or MM74HC05

Logic Diagram

Typical Application

TL/F/9388 – 2

TL/F/9388 – 3

Note: Can be extended to more than 2 inputs.

C1995 National Semiconductor Corporation

TL/F/9388

RRD-B30M105/Printed in U. S. A.

MM54HC05/MM74HC05 Hex Inverter (Open Drain)

January 1988

Absolute Maximum Ratings (Notes 1 & 2)

Operating Conditions

If Military/Aerospace specified devices are required,

please contact the National Semiconductor Sales

Office/Distributors for availability and specifications.

Supply Voltage (VCC)

DC Input or Output Voltage

(VIN, VOUT)

Operating Temp. Range (TA)

MM74HC

MM54HC

Input Rise or Fall Times

(tr, tf) VCC e 2.0V

VCC e 4.5V

VCC e 6.0V

b 0.5V to a 7.0V

Supply Voltage (VCC)

b 1.5V to VCC a 1.5V

DC Input Voltage (VIN)

b 0.5V to VCC a 0.5V

DC Output Voltage (VOUT)

g 20 mA

Clamp Diode Current (IIK, IOK)

g 25 mA

DC Output Current, per pin (IOUT)

g 50 mA

DC VCC or GND Current, per pin (ICC)

b 65§ C to a 150§ C

Storage Temperature Range (TSTG)

Power Dissipation (PD)

(Note 3)

600 mW

S.O. Package only

500 mW

Lead Temperature (TL)

(Soldering 10 seconds)

260§ C

DC Electrical Characteristics

Symbol

Parameter

Conditions

Min

2

0

Max

6

VCC

Units

V

V

b 40

b 55

a 85

a 125

§C

§C

1000

500

400

ns

ns

ns

(Note 4)

VCC

TA e 25§ C

74HC

54HC

TA eb40§ C to a 85§ C TA eb55§ C to a 125§ C Units

Typ

Guaranteed Limits

VIH

Minimum High Level

Input Voltage

2.0V

4.5V

6.0V

1.5

3.15

4.2

1.5

3.15

4.2

1.5

3.15

4.2

V

V

V

VIL

Maximum Low Level

Input Voltage**

2.0V

4.5V

6.0V

0.5

1.35

1.8

0.5

1.35

1.8

0.5

1.35

1.8

V

V

V

VOL

Maximum Low Level

Output Voltage

VIN e VIH

lIOUTl s20 mA

RL e %

VIN e VIH

lIOUTl s4.0 mA

lIOUTl s5.2 mA

2.0V

4.5V

6.0V

0

0

0

0.1

0.1

0.1

0.1

0.1

0.1

0.1

0.1

0.1

V

V

V

4.5V

6.0V

0.2

0.2

0.26

0.26

0.33

0.33

0.4

0.4

V

V

0.5

5

10

mA

g 0.1

g 1.0

g 1.0

mA

2.0

20

40

mA

ILKG

Maximum High Level

VIN e VIH or VIL

Output Leakage Current VOUT e VCC

6.0V

IIN

Maximum Input

Current

VIN e VCC or GND 6.0V

ICC

Maximum Quiescent

Supply Current

VIN e VCC or GND 6.0V

IOUT e 0 mA

Note 1: Absolute Maximum Ratings are those values beyond which damage to the device may occur.

Note 2: Unless otherwise specified all voltages are referenced to ground.

Note 3: Power Dissipation temperature derating Ð plastic ‘‘N’’ package: b 12 mW/§ C from 65§ C to 85§ C; ceramic ‘‘J’’ package: b 12 mW/§ C from 100§ C to 125§ C.

Note 4: For a power supply of 5V g 10% the worst case output voltages (VOH and VOL) occur for HC at 4.5V. Thus the 4.5V values should be used when

designing with this supply. Worst case VIH and VIL occur at VCC e 5.5V and 4.5V respectively. (The VIH value at 5.5V is 3.85V.) The worst case leakage current

(IIN, ICC, and IOZ) occur for CMOS at the higher voltage and so the 6.0V values should be used.

**VIL limits are currently tested at 20% of VCC. The above VIL specification (30% of VCC) will be implemented no later than Q1, CY’89.

2

AC Electrical Characteristics

VCC e 5V, TA e 25§ C, CL e 15 pF, tr e tf e 6 ns

Symbol

Parameter

Conditions

Typ

tPZL, tPLZ

Maximum Propagation Delay

RL e 1 kX

8

AC Electrical Characteristics

Symbol

Parameter

Conditions

Guaranteed

Limit

Units

ns

VCC e 2.0V to 6.0V, CL e 50 pF, tr e tf e 6 ns unless otherwise specified

VCC

TA e 25§ C

Typ

74HC

TA eb40§ C to a 85§ C

54HC

TA eb55§ C to a 125§ C

Units

Guaranteed Limits

tPZL

Maximum Propagation

Delay

RL e 1 kX

2.0V

4.5V

6.0V

30

8

7

75

15

13

95

19

16

110

22

19

ns

ns

ns

tPLZ

Maximum Propagation

Delay

RL e 1 kX

2.0V

4.5V

6.0V

30

13

12

90

18

15

115

23

20

135

27

23

ns

ns

ns

tTHL

Maximum Output

Fall Time

2.0V

4.5V

6.0V

30

8

7

75

15

13

95

19

16

110

22

19

ns

ns

ns

CPD

Power Dissipation

Capacitance (Note 5)

CIN

Maximum Input

Capacitance

(per gate)

8

5

pF

10

10

10

pF

Note 5: CPD determines the no load dynamic power consumption, PD e CPD VCC2 f a ICC VCC, and the no load dynamic current consumption, IS e CPD VCC f a ICC.

The power dissipated by RL is not included.

Physical Dimensions inches (millimeters)

Order Number MM54HC05J or MM74HC05J

NS Package Number J14A

3

SLRS007B − NOVEMBER 1986 − REVISED NOVEMBER 1995

•

•

•

•

•

•

•

•

•

•

•

•

•

•

NE PACKAGE

(TOP VIEW)

1-A Output-Current Capability Per Driver

Applications Include Half-H and Full-H

Solenoid Drivers and Motor Drivers

Designed for Positive-Supply Applications

Wide Supply-Voltage Range of 4.5 V to 36 V

TTL- and CMOS-Compatible

High-Impedance Diode-Clamped Inputs

Separate Input-Logic Supply

Thermal Shutdown

Internal ESD Protection

Input Hysteresis Improves Noise Immunity

3-State Outputs

Minimized Power Dissipation

Sink/Source Interlock Circuitry Prevents

Simultaneous Conduction

No Output Glitch During Power Up or

Power Down

Improved Functional Replacement for the

SGS L293

1,2EN

1A

1Y

HEAT SINK AND

GROUND

1

16

2

15

3

14

4

13

5

12

2Y

2A

6

11

7

10

VCC2

8

9

VCC1

4A

4Y

HEAT SINK AND

GROUND

3Y

3A

3,4EN

FUNCTION TABLE

(each driver)

INPUTS†

OUTPUT

A

EN

Y

H

H

H

L

H

L

X

L

Z

H = high-level, L = low-level

X = irrelevant

Z = high-impedance (off)

† In the thermal shutdown

mode, the output is in a highimpedance state regardless

of the input levels.

description

The SN754410 is a quadruple high-current half-H

driver designed to provide bidirectional drive

currents up to 1 A at voltages from 4.5 V to 36 V.

The device is designed to drive inductive loads

such as relays, solenoids, dc and bipolar stepping

motors, as well as other high-current/high-voltage

loads in positive-supply applications.

All inputs are compatible with TTL-and low-level CMOS logic. Each output (Y) is a complete totem-pole driver

with a Darlington transistor sink and a pseudo-Darlington source. Drivers are enabled in pairs with drivers 1 and

2 enabled by 1,2EN and drivers 3 and 4 enabled by 3,4EN. When an enable input is high, the associated drivers

are enabled and their outputs become active and in phase with their inputs. When the enable input is low, those

drivers are disabled and their outputs are off and in a high-impedance state. With the proper data inputs, each

pair of drivers form a full-H (or bridge) reversible drive suitable for solenoid or motor applications.

A separate supply voltage (VCC1) is provided for the logic input circuits to minimize device power dissipation.

Supply voltage VCC2 is used for the output circuits.

The SN754410 is designed for operation from − 40°C to 85°C.

Copyright 1995, Texas Instruments Incorporated

!" # $%&" !# '%()$!" *!"&+

*%$"# $ " #'&$$!"# '& ",& "&# &-!# #"%&"#

#"!*!* .!!"/+ *%$" '$&##0 *&# " &$&##!)/ $)%*&

"&#"0 !)) '!!&"&#+

• DALLAS, TEXAS 75265

• HOUSTON, TEXAS 77251−1443

POST OFFICE BOX 655303

POST OFFICE BOX 1443

1

SLRS007B − NOVEMBER 1986 − REVISED NOVEMBER 1995

logic symbol†

1A

1,2EN

2A

3A

3, 4EN

4A

logic diagram

2

3

1

EN

1, 2EN

EN

7

6

10

11

9

EN

2A

2Y

3A

3Y

3, 4EN

EN

15

1A

1Y

14

4A

4Y

2

3

7

6

10

11

9

15

14

† This symbol is in accordance with ANSI/IEEE Std 91-1984

and IEC Publication 617-12.

schematics of inputs and outputs

EQUIVALENT OF EACH INPUT

TYPICAL OF ALL OUTPUTS

VCC2

VCC1

Current

Source

Output

Input

GND

2

GND

•

POST OFFICE BOX 655303 DALLAS, TEXAS 75265

POST OFFICE BOX 1443 HOUSTON, TEXAS 77251−1443

•

1Y

1

2Y

3Y

4Y

SLRS007B − NOVEMBER 1986 − REVISED NOVEMBER 1995

absolute maximum ratings over operating free-air temperature range (unless otherwise noted)†

Output supply voltage range, VCC1 (see Note 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . −0.5 V to 36 V

Output supply voltage range, VCC2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . −0.5 V to 36 V

Input voltage, VI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36 V

Output voltage range, VO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . −3 V to VCC2 + 3 V

Peak output current (nonrepetitive, tw ≤ 5 ms) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ± 2 A

Continuous output current, IO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ± 1.1 A

Continuous total power dissipation at (or below) 25°C free-air temperature (see Note 2) . . . . . . . . 2075 mW

Operating free-air temperature range, TA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . −40°C to 85°C

Operating virtual junction temperature range, TJ . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . −40°C to 150°C

Storage temperature range, Tstg . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . −65°C to 150°C

Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 260°C

† Stresses beyond those listed under “absolute maximum ratings” may cause permanent damage to the device. These are stress ratings only, and

functional operation of the device at these or any other conditions beyond those indicated under “recommended operating conditions” is not

implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. All voltage values are with respect to network GND.

2. For operation above 25°C free-air temperature, derate linearly at the rate of 16.6 mW/°C. To avoid exceeding the design maximum

virtual junction temperature, these ratings should not be exceeded. Due to variations in individual device electrical characteristics

and thermal resistance, the built-in thermal overload protection can be activated at power levels slightly above or below the rated

dissipation.

recommended operating conditions

MIN

MAX

Output supply voltage, VCC1

4.5

5.5

V

Output supply voltage, VCC2

4.5

36

V

High-level input voltage, VIH

2

−0.3‡

5.5

V

0.8

V

−40

125

°C

Low-level input voltage, VIL

Operating virtual junction temperature, TJ

UNIT

Operating free-air temperature, TA

−40

85

°C

‡ The algebraic convention, in which the least positive (most negative) limit is designated as minimum, is used in this data sheet for logic voltage

levels.

•

POST OFFICE BOX 655303 DALLAS, TEXAS 75265

POST OFFICE BOX 1443 HOUSTON, TEXAS 77251−1443

•

3

SLRS007B − NOVEMBER 1986 − REVISED NOVEMBER 1995

electrical characteristics over recommended ranges of supply voltage and free-air temperature

(unless otherwise noted)

PARAMETER

TEST CONDITIONS

VIK

Input clamp voltage

II = − 12 mA

IOH = − 0.5 A

VOH

High-level output voltage

IOH = − 1 A

IOH = − 1 A,

MIN

TJ = 25°C

TYP†

MAX

UNIT

−0.9

−1.5

V

VCC2 −1.5

VCC2 −2

VCC2 −1.1

VCC2 −1.8

VCC2 −1.4

1

V

Low-level output voltage

IOL = 0.5 A

IOL = 1 A

IOL = 1 A,

VOKH

High-level output clamp voltage

IOK = − 0.5 A

IOK = 1 A

VCC2 + 1.4

VCC2 + 1.9

−2

Low-level output clamp voltage

−1.3

−2.5

IOZ(off)

Off-state high-impedance-state

output current

IOK = 0.5 A

IOK = − 1 A

VO = VCC2

−1.1

VOKL

VOL

IIH

IIL

High-level input current

VO = 0

VI = 5.5 V

Low-level input current

VI = 0

ICC1

Output supply current

IO = 0

ICC2

Output supply current

IO = 0

1.4

2

TJ = 25°C

1.2

V

1.8

VCC2 + 2

VCC2 + 2.5

500

−500

V

µA

A

10

µA

−10

µA

All outputs at high level

38

All outputs at low level

70

All outputs at high impedance

25

All outputs at high level

33

All outputs at low level

20

All outputs at high impedance

† All typical values are at VCC1 = 5 V, VCC2 = 24 V, TA = 25°C.

V

mA

mA

5

switching characteristics, VCC1 = 5 V, VCC2 = 24 V, CL = 30 pF, TA = 25°C

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

td1

td2

Delay time, high-to-low-level output from A input

400

ns

Delay time, low-to-high-level output from A input

800

ns

tTLH

tTHL

Transition time, low-to-high-level output

300

ns

300

ns

tr

tf

Rise time, pulse input

tw

ten1

Pulse duration

Enable time to the high level

700

ns

ten2

tdis1

Enable time to the low level

400

ns

900

ns

tdis2

Disable time from the low level

600

ns

4

Transition time, high-to-low-level output

See Figure 1

Fall time, pulse input

See Figure 2

Disable time from the high level

•

POST OFFICE BOX 655303 DALLAS, TEXAS 75265

POST OFFICE BOX 1443 HOUSTON, TEXAS 77251−1443

•

TCRT5000, TCRT5000L

Vishay Semiconductors

Reflective Optical Sensor with Transistor Output

FEATURES

• Package type: leaded

• Detector type: phototransistor

• Dimensions (L x W x H in mm): 10.2 x 5.8 x 7

• Peak operating distance: 2.5 mm

• Operating range within > 20 % relative collector

current: 0.2 mm to 15 mm

19156_2

• Typical output current under test: IC = 1 mA

C

• Daylight blocking filter

A

• Emitter wavelength: 950 nm

E

Top view

• Lead (Pb)-free soldering released

C

• Compliant to RoHS directive 2002/95/EC

accordance to WEEE 2002/96/EC

19156_1

DESCRIPTION

APPLICATIONS

The TCRT5000 and TCRT5000L are reflective sensors

which include an infrared emitter and phototransistor in a

leaded package which blocks visible light. The package

includes two mounting clips. TCRT5000L is the long lead

version.

• Position sensor for shaft encoder

and

in

• Detection of reflective material such as paper, IBM cards,

magnetic tapes etc.

• Limit switch for mechanical motions in VCR

• General purpose - wherever the space is limited

PRODUCT SUMMARY

PART NUMBER

DISTANCE FOR

MAXIMUM CTRrel (1)

(mm)

DISTANCE RANGE FOR

RELATIVE Iout > 20 %

(mm)

TYPICAL OUTPUT

CURRENT UNDER TEST (2)

(mA)

DAYLIGHT

BLOCKING FILTER

INTEGRATED

TCRT5000

2.5

0.2 to 15

1

Yes

TCRT5000L

2.5

0.2 to 15

1

Yes

Notes

(1) CTR: current transfere ratio, I /I

out in

(2) Conditions like in table basic charactristics/sensors

ORDERING INFORMATION

PACKAGING

VOLUME (1)

REMARKS

TCRT5000

Tube

MOQ: 4500 pcs, 50 pcs/tube

3.5 mm lead length

TCRT5000L

Tube

MOQ: 2400 pcs, 48 pcs/tube

15 mm lead length

ORDERING CODE

Note

MOQ: minimum order quantity

(1)

ABSOLUTE MAXIMUM RATINGS

PARAMETER

(1)

TEST CONDITION

SYMBOL

VALUE

UNIT

INPUT (EMITTER)

Reverse voltage

VR

5

V

Forward current

IF

60

mA

Forward surge current

Power dissipation

Junction temperature

Document Number: 83760

Rev. 1.7, 17-Aug-09

tp ≤ 10 µs

IFSM

3

A

Tamb ≤ 25 °C

PV

100

mW

Tj

100

°C

For technical questions, contact: sensorstechsupport@vishay.com

www.vishay.com

1

TCRT5000, TCRT5000L

Reflective Optical Sensor with

Transistor Output

Vishay Semiconductors

ABSOLUTE MAXIMUM RATINGS

PARAMETER

(1)

TEST CONDITION

SYMBOL

VALUE

UNIT

Collector emitter voltage

VCEO

70

V

Emitter collector voltage

VECO

5

V

OUTPUT (DETECTOR)

Collector current

Tamb ≤ 55 °C

Power dissipation

IC

100

mA

PV

100

mW

Tj

100

°C

Junction temperature

SENSOR

Tamb ≤ 25 °C

Total power dissipation

Ptot

200

mW

Ambient temperature range

Tamb

- 25 to + 85

°C

Storage temperature range

Tstg

- 25 to + 100

°C

Tsd

260

°C

2 mm from case, t ≤ 10 s

Soldering temperature

Note

(1) T

amb = 25 °C, unless otherwise specified

ABSOLUTE MAXIMUM RATINGS

P - Power Dissipation (mW)

300

Coupled device

200

Phototransistor

100

IR - diode

0

25

0

95 11071

75

50

100

Tamb - Ambient Temperature (°C)

Fig. 1 - Power Dissipation Limit vs. Ambient Temperature

BASIC CHARACTERISTICS

(1)

PARAMETER

TEST CONDITION

SYMBOL

IF = 60 mA

VR = 0 V, f = 1 MHz

MIN.

TYP.

MAX.

VF

1.25

1.5

Cj

17

UNIT

INPUT (EMITTER)

Forward voltage

Junction capacitance

V

pF

Radiant intensity

IF = 60 mA, tp = 20 ms

Ie

Peak wavelength

IF = 100 mA

λP

Method: 63 % encircled energy

d

Collector emitter voltage

IC = 1 mA

VCEO

70

V

Emitter collector voltage

Ie = 100 µA

VECO

7

V

VCE = 20 V, IF = 0 A, E = 0 lx

ICEO

VCE = 5 V, IF = 10 mA,

D = 12 mm

IC (2) (3)

IF = 10 mA, IC = 0.1 mA,

D = 12 mm

VCEsat (2) (3)

Virtual source diameter

21

940

mW/sr

nm

2.1

mm

OUTPUT (DETECTOR)

Collector dark current

10

200

nA

1

2.1

mA

0.4

V

SENSOR

Collector current

Collector emitter saturation

voltage

0.5

Note

Tamb = 25 °C, unless otherwise specified

(2) See figure 3

(3) Test surface: mirror (Mfr. Spindler a. Hoyer, Part No. 340005)

(1)

www.vishay.com

2

For technical questions, contact: sensorstechsupport@vishay.com

Document Number: 83760

Rev. 1.7, 17-Aug-09

TCRT5000, TCRT5000L

Reflective Optical Sensor with

Transistor Output

Vishay Semiconductors

94 9226

IF

Flat mirror

∅ = 22.5 mm

rem. 2

IC

VCC

d = working distance

D = distance

12 ± 0.2 mm

TCRT5000

7.0 ± 0.2 mm

A

96 12314

Fig. 2 - Test Circuit

Fig. 3 - Test Circuit

BASIC CHARACTERISTICS

Tamb = 25 °C, unless otherwise specified

1000

10

IC - Collector Current (mA)

IF - Forward Current (mA)

VCE = 5 V

100

10

1

0.1

0 0.2 0.4 0.6 0.8 1.0 1.2 1.4 1.6 1.8 2.0

VF - Forward Voltage (V)

96 11862

1

0.1

0.01

0.001

0.1

96 11763

1.2

1.1

0.9

0.8

0.7

0.6

- 30 - 20 -10 0 10 20 30 40 50 60 70 80 90 100

Tamb - Ambient Temperature (°C)

Fig. 5 - Relative Current Transfer Ratio vs. Ambient Temperature

Document Number: 83760

Rev. 1.7, 17-Aug-09

100

10

VCE = 5 V

I F = 20 mA

1.0

96 11762

10

Fig. 6 - Collector Current vs. Forward Current

IC - Collector Current (mA)

CTR rel - Relative Current Transfer Ratio

Fig. 4 - Forward Current vs. Forward Voltage

1

I F - Forward Current (mA)

I F = 50 mA

20 mA

1

10 mA

5 mA

2 mA

0.1

1 mA

0.01

0.1

96 11764

1

10

100

VCE - Collector Emitter Voltage (V)

Fig. 7 - Collector Emitter Saturation Voltage vs. Collector Current

For technical questions, contact: sensorstechsupport@vishay.com

www.vishay.com

3

TCRT5000, TCRT5000L

Vishay Semiconductors

Reflective Optical Sensor with

Transistor Output

1.2

VCE = 5 V

I Crel - Relative Collector Current

CTR - Current Transfer Ratio (%)

100

10

1

0.1

0.1

96 11765

VCE = 10 V

I F = 20 mA

1.0

0.8

0.6

0.4

0.2

0.0

1

10

I F - Forward Current (mA)

100

Fig. 8 - Current Transfer Ratio vs. Forward Current

0

96 11766

4

8

10 12 14 16

2

6

d - Distance to Reflecting Card (mm)

Fig. 9 - Relative Collector Current vs. Distance

PACKAGE DIMENSIONS in millimeters, TCRT5000

96 12073

www.vishay.com

4

For technical questions, contact: sensorstechsupport@vishay.com

Document Number: 83760

Rev. 1.7, 17-Aug-09

PIC32MX3XX/4XX

TABLE 29-9:

DC CHARACTERISTICS: I/O PIN OUTPUT SPECIFICATIONS

DC CHARACTERISTICS

Param.

Symbol

No.

VOL

DO10

Characteristics

OSC2/CLKO

VOH

DO20

Typical

Max.

Units

Conditions

—

—

0.4

V

IOL = 7 mA, VDD = 3.6V

—

—

0.4

V

IOL = 6 mA, VDD = 2.3V

—

—

0.4

V

IOL = 3.5 mA, VDD = 3.6V

—

—

0.4

V

IOL = 2.5 mA, VDD = 2.3V

2.4

—

—

V

IOH = -12 mA, VDD = 3.6V

1.4

—

—

V

IOH = -12 mA, VDD = 2.3V

2.4

—

—

V

IOH = -12 mA, VDD = 3.6V

1.4

—

—

V

IOH = -12 mA, VDD = 2.3V

Output High Voltage

I/O Ports

DO26

Min.

Output Low Voltage

I/O Ports

DO16

Standard Operating Conditions: 2.3V to 3.6V (unless otherwise

stated)

Operating temperature

-40°C ≤TA ≤+85°C for Industrial

-40°C ≤TA ≤+105°C for V-Temp

OSC2/CLKO

TABLE 29-10: ELECTRICAL CHARACTERISTICS: BROWN-OUT RESET (BOR)

DC CHARACTERISTICS

Param.

Symbol

No.

BO10

VBOR

DS61143H-page 158

Characteristics

BOR Event on VDD

transition high-to-low

Standard Operating Conditions: 2.3V to 3.6V (unless otherwise

stated)

Operating temperature

-40°C ≤TA ≤+85°C for Industrial

-40°C ≤TA ≤+105°C for V-Temp

Min.

Typical

Max.

Units

Conditions

2.0

—

2.3

V

—

© 2011 Microchip Technology Inc.

PIC32MX3XX/4XX

TABLE 29-11: DC CHARACTERISTICS: PROGRAM MEMORY(3)

Standard Operating Conditions: 2.3V to 3.6V

(unless otherwise stated)

Operating temperature -40°C ≤TA ≤+85°C for Industrial

-40°C ≤TA ≤+105°C for V-Temp

DC CHARACTERISTICS

Param.

No.

Symbol

Characteristics

Min.

Typical(1) Max. Units

Conditions

Program Flash Memory

D130

EP

Cell Endurance

1000

—

—

E/W

—

D131

VPR

VDD for Read

VMIN

—

3.6

V

—

D132

VPEW

VDD for Erase or Write

3.0

—

3.6

V

—

D134

TRETD

Characteristic Retention

20

—

—

Year

—

D135

IDDP

Supply Current during

Programming

—

10

—

mA

—

TWW

Word Write Cycle Time

20

—

40

μs

—

3

4.5

—

ms

—

(2)

D136

TRW

Row Write Cycle Time

(128 words per row)

D137

TPE

Page Erase Cycle Time

20

—

—

ms

—

TCE

Chip Erase Cycle Time

80

—

—

ms

—

—

—

6

μs

—

D138

LVDstartup Flash LVD Delay

Note 1:

2:

3:

Data in “Typical” column is at 3.3V, 25°C unless otherwise stated.

The minimum SYSCLK for row programming is 4 MHz. Care should be taken to minimize bus activities

during row programming, such as suspending any memory-to-memory DMA operations. If heavy bus

loads are expected, selecting Bus Matrix Arbitration mode 2 (rotating priority) may be necessary. The

default Arbitration mode is mode 1 (CPU has lowest priority).

Refer to the “PIC32MX Flash Programming Specification” (DS61145) for operating conditions during

programming and erase cycles.

TABLE 29-12: PROGRAM FLASH MEMORY WAIT STATE CHARACTERISTICS

DC CHARACTERISTICS

Required Flash wait states

Note 1:

Standard Operating Conditions: 2.3V to 3.6V

(unless otherwise stated)

Operating temperature -40°C ≤TA ≤+85°C for Industrial

-40°C ≤TA ≤+105°C for V-Temp

SYSCLK

0 Wait State

0 to 30

1 Wait State

31 to 60

2 Wait States

61 to 80

Units

Comments

MHz

—

40 MHz maximum for PIC32MX320F032H and PIC32MX420F032H devices.

© 2011 Microchip Technology Inc.

DS61143H-page 159

PIC32MX3XX/4XX

TABLE 29-13: COMPARATOR SPECIFICATIONS

Standard Operating Conditions: 2.3V to 3.6V

(unless otherwise stated)

Operating temperature -40°C ≤TA ≤+85°C for Industrial

-40°C ≤TA ≤+105°C for V-Temp

DC CHARACTERISTICS

Param.

Symbol

No.

D300

D301

D302

D303

D304

D305

Note

Characteristics

Min.

Typical

Max.

Units

—

±7.5

±25

mV

Comments

AVDD = VDD,

AVSS = VSS

VICM

Input Common Mode Voltage

0

—

VDD

V

AVDD = VDD,

AVSS = VSS

(Note 2)

CMRR

Common Mode Rejection Ratio

55

—

—

dB

Max VICM = (VDD - 1)V

(Note 2)

Response Time

—

150

400

ns

AVDD = VDD,

TRESP

AVSS = VSS

(Notes 1,2)

ON2OV

Comparator Enabled to Output

—

—

10

μs

Comparator module is

Valid

configured before setting

the comparator ON bit.

(Note 2)

Internal Voltage Reference

0.57

0.6

0.63

V

—

IVREF

1: Response time measured with one comparator input at (VDD – 1.5)/2, while the other input transitions

from VSS to VDD.

2: These parameters are characterized but not tested.

VIOFF

Input Offset Voltage

TABLE 29-14: VOLTAGE REFERENCE SPECIFICATIONS

Standard Operating Conditions: 2.3V to 3.6V

(unless otherwise stated)

Operating temperature -40°C ≤TA ≤+85°C for Industrial

-40°C ≤TA ≤+105°C for V-Temp

DC CHARACTERISTICS

Param.

No.

Symbol

Characteristics

D310

VRES

Resolution

D311

VRAA

Absolute Accuracy

D312

Note 1:

TSET

Settling

Min.

Typical

Max.

VDD/24

—

—

—

—

—

Time(1)

Units

Comments

VDD/32

LSb

—

1/2

LSb

—

10

μs

—

Settling time measured while CVRR = 1 and CVR3:CVR0 transitions from ‘0000’ to ‘1111’. This

parameter is characterized, but not tested in manufacturing.

TABLE 29-15: INTERNAL VOLTAGE REGULATOR SPECIFICATIONS

Standard Operating Conditions: 2.3V to 3.6V

(unless otherwise stated)

Operating temperature -40°C ≤TA ≤+85°C for Industrial

-40°C ≤TA ≤+105°C for V-Temp

DC CHARACTERISTICS

Param.

No.

Symbol

Characteristics

Min.

Typical

Max.

Units

Comments

D320

VCORE

Regulator Output Voltage

1.62

1.80

1.98

V

—

D321

CEFC

External Filter Capacitor Value

8

10

—

μF

Capacitor must be low series

resistance (< 1 Ohm)

D322

TPWRT

Power-up Timer Period

—

64

—

ms

ENVREG = 0

DS61143H-page 160

© 2011 Microchip Technology Inc.

PIC32MX3XX/4XX

29.2

AC Characteristics and Timing

Parameters

The information contained in this section defines

PIC32MX3XX/4XX AC characteristics and timing

parameters.

FIGURE 29-1:

LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

Load Condition 1 – for all pins except OSC2

Load Condition 2 – for OSC2

VDD/2

CL

Pin

RL

VSS

CL

Pin

RL = 464Ω

CL = 50 pF for all pins

50 pF for OSC2 pin (EC mode)

VSS

TABLE 29-16: CAPACITIVE LOADING REQUIREMENTS ON OUTPUT PINS

AC CHARACTERISTICS

Standard Operating Conditions: 2.3V to 3.6V

(unless otherwise stated)

Operating temperature -40°C ≤TA ≤+85°C for Industrial

-40°C ≤TA ≤+105°C for V-Temp

Param.

Symbol

No.

Min.

Typical(1)

Characteristics

Max.

Units

Conditions

DO56

CIO

All I/O pins and OSC2

—

—

50

pF

EC mode

DO58

CB

SCLx, SDAx

—

—

400

pF

In I2C™ mode

Note 1:

Data in “Typical” column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only

and are not tested.

FIGURE 29-2:

EXTERNAL CLOCK TIMING

OS20

OS30

OS31

OSC1

OS30

© 2011 Microchip Technology Inc.

OS31

DS61143H-page 161

GP2Y0A02YK0F

GP2Y0A02YK0F

Distance Measuring Sensor Unit

Measuring distance: 20 to 150 cm

Analog output type

■Description

■Agency approvals/Compliance

GP2Y0A02YK0F is a distance measuring sensor unit,

composed of an integrated combination of PSD

(position sensitive detector) , IRED (infrared emitting

diode) and signal processing circuit.

The variety of the reflectivity of the object, the

environmental temperature and the operating duration

are not influenced easily to the distance detection

because of adopting the triangulation method.

This device outputs the voltage corresponding to the

detection distance. So this sensor can also be used as

a proximity sensor.

■Features

1. Compliant with RoHS directive (2002/95/EC)

■Applications

1. Touch-less switch

(Sanitary equipment, Control of illumination, etc. )

2. Sensor for energy saving

(ATM, Copier, Vending machine, Laptop computer,

LCD monitor)

3. Amusement equipment

(Robot, Arcade game machine)

1. Distance measuring range : 20 to 150 cm

2. Analog output type

3. Package size : 29.5×13×21.6 mm

4. Consumption current : Typ. 33 mA

5. Supply voltage : 4.5 to 5.5 V

Notice The content of data sheet is subject to change without prior notice.

In the absence of confirmation by device specification sheets, SHARP takes no responsibility for any defects that may occur in equipment using any SHARP

devices shown in catalogs, data books, etc. Contact SHARP in order to obtain the latest device specification sheets before using any SHARP device.

Sheet No.: E4-A00101EN

Date Dec.01.2006

1

©SHARP Corporation

GP2Y0A02YK0F

■Block diagram

③VCC

②GND

Signal

processing circuit

Voltage regulator

PSD

Oscillation circuit

LED drive circuit

①VO

Output circuit

LED

Distance measuring IC

■Outline Dimensions

(Unit : mm)

Stamp

Stamp (Example)

Model name

Production month : Jan. to Sep. ; 1 to 9

Oct. ; X, Nov. ; Y, Dec. ; Z

Production year : Last digit of prod. year

Lens case

*

Light emitter side

*

Light detector side

Connector

PWB

Terminal

① Output terminal voltage

② Ground

③ Supply voltage

Note 1. Unspecified tolerances shall be ± 0.3 mm.

Note 2. The connector is made by J.S.T.TRADING COMPANY,LTD. and its part number is S3B-PH.

Note 3. The dimensions in parenthesis are shown for reference.

Note 4. The dimension marked by “*” show a distance from/to the center of an internal optical slit.

Symbol

VO

GND

VCC

Product mass : approx. 4.8g

Sheet No.: E4-A00101EN

2

GP2Y0A02YK0F

■Absolute Maximum Ratings

Parameter

Supply voltage

Output terminal voltage

Operating temperature

Storage temperature

(Ta=25℃,VCC=5V)

Symbol

VCC

VO

Topr

Tstg

Rating

-0.3 to +7

-0.3 to VCC+0.3

-10 to +60

-40 to +70

Unit

V

V

℃

℃

■Electro-optical Characteristics

Parameter

Average supply current

Measuring distance range

Output voltage

Symbol

ICC

ΔL

VO

Output voltage differential

ΔVO

(Ta=25℃,VCC=5V)

Conditions

L=150cm (Note 1)

(Note 1)

L=150cm (Note 1)

Output voltage difference between

L=20cm and L=150cm (Note 1)

MIN.

―

20

0.25

TYP.

33

―

0.4

MAX.

50

150

0.55

Unit

mA

cm

V

1.8

2.05

2.3

V

* L : Distance to reflective object

Note 1 : Using reflective object : White paper (Made by Kodak Co., Ltd. gray cards R-27・white face, reflectance; 90%)

■Recommended operating conditions

Parameter

Supply voltage

Symbol

VCC

Conditions

Rating

4.5 to 5.5

Unit

V

Sheet No.: E4-A00101EN

3

GP2Y0A02YK0F

Fig. 1 Timing chart

Vcc(Power supply)

38.3ms±9.6ms

Distance measuring operating

Vo(Output)

First measurement

Unstable output

Second

measurement

First output

nth

measurement

Second output

nth

output

MAX 5.0ms

Sheet No.: E4-A00101EN

4

GP2Y0A02YK0F

Fig. 2 Example of distance measuring characteristics (output)

3

White paper (Reflectance ratio : 90 %)

Output voltage [V]

2.5

Gray paper (reflectance ratio : 18 %)

2

1.5

1

0.5

0

0

10 20 30 40 50 60 70 80 90 100 110 120 130 140 150

Distance to reflective object L [cm]

3

15cm

20cm

2.5

Output voltage [V]

10cm

30cm

2

40cm

1.5

50cm

60cm

1

100cm

White paper (Reflectance ratio : 90 %)

0.5

Gray paper (reflectance ratio : 18 %)

150cm

0

0

0.01

0.02

0.03

0.04

0.05 0.06

0.07

0.08

0.09

0.1

Inverse number of distance [1/cm]

Sheet No.: E4-A00101EN

5

GP2Y0A02YK0F

■Notes

●Advice for the optics

• The lens of this device needs to be kept clean. There are cases that dust, water or oil and so on deteriorate

the characteristics of this device. Please consider in actual application.

• Please don’t do washing. Washing may deteriorate the characteristics of optical system and so on.

Please confirm resistance to chemicals under the actual usage since this product has not been designed against washing.

●Advice for the characteristics

• In case that an optical filter is set in front of the emitter and detector portion, the optical filter which has the most

efficient transmittance at the emitting wavelength range of LED for this product (λ = 850 ± 70nm), shall be

recommended to use. Both faces of the filter should be mirror polishing. Also, as there are cases that the characteristics

may not be satisfied according to the distance between the protection cover and this product or the thickness of the

protection cover, please use this product after confirming the operation sufficiently in actual application.

• In case that there is an object near to emitter side of the sensor between sensor and a detecting object, please use this

device after confirming sufficiently that the characteristics of this sensor do not change by the object.

• When the detector is exposed to the direct light from the sun, tungsten lamp and so on, there are cases that it can not

measure the distance exactly. Please consider the design that the detector is not exposed to the direct light from such

light source.

• Distance to a mirror reflector can not be sometimes measured exactly.

In case of changing the mounting angle of this product, it may measure the distance exactly.

• In case that reflective object has boundary line which material or color etc. are excessively different, in order to

decrease deviation of measuring distance, it shall be recommended to set the sensor that the direction of boundary line

and the line between emitter center and detector center are in parallel.

(Incorrect)

(Correct)

• In order to decrease deviation of measuring distance by moving direction of the reflective object, it shall be

recommended to set the sensor that the moving direction of the object and the line between emitter center and

detector center are vertical.

(Incorrect)

(Correct)

(Moving direction)

(Moving direction)

●Advice for the power supply

• In order to stabilize power supply line, we recommend to insert a by-pass capacitor of 10μF or more

between Vcc and GND near this product.

●Notes on handling

• There are some possibilities that the internal components in the sensor may be exposed to the excessive mechanical

stress. Please be careful not to cause any excessive pressure on the sensor package and also on the PCB while

assembling this product.

Sheet No.: E4-A00101EN

6

TIP120/TIP121/TIP122

NPN Epitaxial Darlington Transistor

• Medium Power Linear Switching Applications

• Complementary to TIP125/126/127

Equivalent Circuit

C

B

TO-220

1

1.Base

2.Collector

R1

3.Emitter

R1 @ 8kW

R2 @ 0.12k W

Absolute Maximum Ratings*

Symbol

VCBO

VCEO

R2

E

T a = 25°C unless otherwise noted

Collector-Base Voltage

Parameter

: TIP120

: TIP121

: TIP122

Collector-Emitter Voltage : TIP120

: TIP121

: TIP122

Ratings

60

80

100

Units

V

V

V

60

80

100

V

V

V

VEBO

Emitter-Base Voltage

5

V

IC

Collector Current (DC)

5

A

ICP

Collector Current (Pulse)

IB

Base Current (DC)

PC

8

A

120

mA

W

Collector Dissipation (Ta=25°C)

2

Collector Dissipation (TC=25°C)

65

W

TJ

Junction Temperature

150

°C

TSTG

Storage Temperature

- 65 ~ 150

°C

* These ratings are limiting values above which the serviceability of any semiconductor device may be impaired.

© 2007 Fairchild Semiconductor Corporation

TIP120/TIP121/TIP122 Rev. 1.0.0

www.fairchildsemi.com

1

TIP120/TIP121/TIP122 — NPN Epitaxial Darlington Transistor

October 2008

Symbol

VCEO(sus)

Parameter

Collector-Emitter Sustaining Voltage

: TIP120

: TIP121

: TIP122

ICEO

Collector Cut-off Current

ICBO

Collector Cut-off Current

Test Condition

IC = 100mA, IB = 0

Min.

Typ.

Max.

60

80

100

Units

V

V

V

: TIP120

: TIP121

: TIP122

VCE = 30V, IB = 0

VCE = 40V, IB = 0

VCE = 50V, IB = 0

0.5

0.5

0.5

mA

mA

mA

: TIP120

: TIP121

: TIP122

VCB = 60V, IE = 0

VCB = 80V, IE = 0

VCB = 100V, IE = 0

0.2

0.2

0.2

mA

mA

mA

2

mA

2.0

4.0

V

V

IEBO

Emitter Cut-off Current

VBE = 5V, IC = 0

hFE

* DC Current Gain

VCE = 3V,IC = 0.5A

VCE = 3V, IC = 3A

VCE(sat)

* Collector-Emitter Saturation Voltage

IC = 3A, IB = 12mA

IC = 5A, IB = 20mA

VBE(on)

* Base-Emitter On Voltage

VCE = 3V, IC = 3A

2.5

V

Cob

Output Capacitance

VCB = 10V, IE = 0, f =

0.1MHz

200

pF

1000

1000

* Pulse Test: Pulse Width£300ms, Duty Cycle£2%

© 2007 Fairchild Semiconductor Corporation

TIP120/TIP121/TIP122 Rev. 1.0.0

www.fairchildsemi.com

2

TIP120/TIP121/TIP122 — NPN Epitaxial Darlington Transistor

Electrical Characteristics* Ta=25°C unless otherwise noted

VBE(sat), VCE(sat)[V], SATURATION VOLTAGE

10000

hFE, DC CURRENT GAIN

VCE = 4V

1000

100

0.1

1

3.5

IC = 250IB

3.0

2.5

2.0

1.5

1.0

VBE(sat)

VCE (sat)

0.5

0.1

10

IC[A], COLLECTOR CURRENT

1

10

IC[A], COLLECTOR CURRENT

Figure 1. DC current Gain

Figure 2. Base-Emitter Saturation Voltage

Collector-Emitter Saturation Voltage

1000

10

IC[A], COLLECTOR CURRENT

Cib

10

0.1

1

10

100

1

0.1

0.01

VCB[V], COLLECTOR-BASE VOLTAGE

VEB[V], EMITTER-BASE VOLTAGE

s

5m

Cob

s

1m

100

DC

Cob[pF] Cib[pF], CAPACITANCE

s

0m

10 ms

0

50

f=0.1MHz

TIP120

TIP121

TIP122

1

10

100

VCE[V], COLLECTOR-EMITTER VOLTAGE

Figure 3. Output and Input Capacitance

vs. Reverse Voltage

Figure 4. Safe Operating Area

80

PC[W], POWER DISSIPATION

70

60

50

40

30

20

10

0

0

25

50

75

100

125

150

175

o

TC[ C], CASE TEMPERATURE

Figure 5. Power Derating

© 2007 Fairchild Semiconductor Corporation

TIP120/TIP121/TIP122 Rev. 1.0.0

www.fairchildsemi.com

3

TIP120/TIP121/TIP122 — NPN Epitaxial Darlington Transistor

Typical characteristics

ULN2002A, ULN2003A, ULN2003AI, ULN2004A

ULQ2003A, ULQ2004A

www.ti.com

SLRS027M – DECEMBER 1976 – REVISED FEBRUARY 2013

HIGH-VOLTAGE, HIGH-CURRENT DARLINGTON TRANSISTOR ARRAYS

Check for Samples: ULN2002A, ULN2003A, ULN2003AI, ULN2004A, ULQ2003A, ULQ2004A

FEATURES

1

•

•

•

•

•

500-mA-Rated Collector Current (Single

Output)

High-Voltage Outputs: 50 V

Output Clamp Diodes

Inputs Compatible With Various Types of

Logic

Relay-Driver Applications

ULN2002A . . . N PACKAGE

ULN2003A . . . D, N, NS, OR PW PACKAGE

ULN2004A . . . D, N, OR NS PACKAGE

ULQ2003A, ULQ2004A . . . D OR N PACKAGE

(TOP VIEW)

1B

2B

3B

4B

5B

6B

7B

E

1

16

2

15

3

14

4

13

5

12

6

11

7

10

8

9

1C

2C

3C

4C

5C

6C

7C

COM

DESCRIPTION

The ULN2002A, ULN2003A, ULN2003AI, ULN2004A, ULQ2003A, and ULQ2004A are high-voltage high-current

Darlington transistor arrays. Each consists of seven npn Darlington pairs that feature high-voltage outputs with

common-cathode clamp diodes for switching inductive loads. The collector-current rating of a single Darlington

pair is 500 mA. The Darlington pairs can be paralleled for higher current capability. Applications include relay

drivers, hammer drivers, lamp drivers, display drivers (LED and gas discharge), line drivers, and logic buffers.

For 100-V (otherwise interchangeable) versions of the ULN2003A and ULN2004A, see the SN75468 and

SN75469, respectively.

The ULN2002A is designed specifically for use with 14-V to 25-V PMOS devices. Each input of this device has a

Zener diode and resistor in series to control the input current to a safe limit. The ULN2003A and ULQ2003A have

a 2.7-kΩ series base resistor for each Darlington pair for operation directly with TTL or 5-V CMOS devices. The

ULN2004A and ULQ2004A have a 10.5-kΩ series base resistor to allow operation directly from CMOS devices

that use supply voltages of 6 V to 15 V. The required input current of the ULN/ULQ2004A is below that of the

ULN/ULQ2003A, and the required voltage is less than that required by the ULN2002A.

1

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of the Texas

Instruments standard warranty. Production processing does not

necessarily include testing of all parameters.

Copyright © 1976–2013, Texas Instruments Incorporated

ULN2002A, ULN2003A, ULN2003AI, ULN2004A

ULQ2003A, ULQ2004A

SLRS027M – DECEMBER 1976 – REVISED FEBRUARY 2013

www.ti.com

ORDERING INFORMATION (1)

PACKAGE (2)

TA

PDIP – N

–20°C to 70°C

SOIC – D

SOP – NS

TSSOP – PW

PDIP – N

ULN2002AN

ULN2003AN

ULN2003AN

ULN2004AN

ULN2004AN

Tube of 40

ULN2003AD

Reel of 2500

ULN2003ADR

Reel of 2500

ULN2003ADRG3

Tube of 40

ULN2004AD

Reel of 2500

ULN2004ADRG3

Reel of 2000

ULN2003A

ULN2003ANSR

ULN2003A

ULN2004ANSR

ULN2004A

Tube of 90

ULN2003APW

Reel of 2000

ULN2003APWR

Tube of 25

ULN2004A

UN2003A

ULQ2003AN

ULQ2003A

ULQ2004AN

ULQ2004AN

Reel of 2500

ULQ2003ADR

Tube of 40

ULQ2004AD

Reel of 2500

ULQ2004ADR

SOP – NS

Reel of 2000

ULN2003AINSR

ULN2003AI

PDIP – N

Tube of 425

ULN2003AIN

ULN2003AIN

Tube of 40

ULN2003AID

Reel of 2500

ULN2003AIDR

Reel of 2500

ULN2003AIPWR

SOIC – D

TSSOP – PW

(2)

ULN2002AN

ULQ2003AD

SOIC – D

(1)

Tube of 25

TOP-SIDE MARKING

Tube of 40

–40°C to 85°C

–40°C to 105°C

ORDERABLE PART NUMBER

ULQ2003A

ULQ2004A

ULN2003AI

UN2003AI

For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI

web site at www.ti.com.

Package drawings, thermal data, and symbolization are available at www.ti.com/packaging.

LOGIC DIAGRAM

9

COM

1

16

1C

1B

2

15

2C

2B

3

14

3C

3B

4

13

4C

4B

5

12

5C

5B

6

11

6C

6B

7

7B

2

Submit Documentation Feedback

10

7C

Copyright © 1976–2013, Texas Instruments Incorporated

Product Folder Links: ULN2002A ULN2003A ULN2003AI ULN2004A ULQ2003A ULQ2004A

ULN2002A, ULN2003A, ULN2003AI, ULN2004A

ULQ2003A, ULQ2004A

www.ti.com

SLRS027M – DECEMBER 1976 – REVISED FEBRUARY 2013

SCHEMATICS (EACH DARLINGTON PAIR)

10.5 kW

7.2 kW

3 kW

ULN2002A

RB

ULN/ULQ2003A: RB = 2.7 kW

ULN2003AI: RB = 2.7 kW

7.2 kW

3 kW

ULN/ULQ2004A: RB = 10.5 kW

ULN2003A, ULN2003AI, ULN2004A, ULQ2003A, ULQ2004A

All resistor values shown are nominal.

The collector-emitter diode is a parasitic structure and should not be used to conduct current. If the collector(s) go

below ground an external Schottky diode should be added to clamp negative undershoots.

Copyright © 1976–2013, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Links: ULN2002A ULN2003A ULN2003AI ULN2004A ULQ2003A ULQ2004A

3

ULN2002A, ULN2003A, ULN2003AI, ULN2004A

ULQ2003A, ULQ2004A

SLRS027M – DECEMBER 1976 – REVISED FEBRUARY 2013

www.ti.com

ABSOLUTE MAXIMUM RATINGS (1)

at 25°C free-air temperature (unless otherwise noted)

MIN

VCC

VI

TA

50

V

Clamp diode reverse voltage (2)

50

V

Input voltage (2)

30

V

500

mA

Output clamp current

500

mA

Total emitter-terminal current

–2.5

A

See Figure 14 and

Figure 15

Operating free-air temperature range

Package thermal impedance (3)

θJA

UNIT

Collector-emitter voltage

Peak collector current

IOK

MAX

(4)

–20

70

ULN200xAI

–40

105

ULQ200xA

–40

85

ULQ200xAT

–40

105

D package

73

N package

67

NS package

64

PW package

108

D package

36

N package

54

°C

°C/W

θJC

Package thermal impedance (5)

TJ

Operating virtual junction temperature

150

°C

Lead temperature for 1.6 mm (1/16 inch) from case for 10 seconds

260

°C

150

°C

Tstg

(1)

(2)

(3)

(4)

(5)

(6)

(6)

ULN200xA

Storage temperature range

–65

Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings

only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating

conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

All voltage values are with respect to the emitter/substrate terminal E, unless otherwise noted.

Maximum power dissipation is a function of TJ(max), θJA, and TA. The maximum allowable power dissipation at any allowable ambient

temperature is PD = (TJ(max) – TA)/θJA. Operating at the absolute maximum TJ of 150°C can affect reliability.

The package thermal impedance is calculated in accordance with JESD 51-7.

Maximum power dissipation is a function of TJ(max), θJC, and TA. The maximum allowable power dissipation at any allowable ambient

temperature is PD = (TJ(max) – TA)/θJC. Operating at the absolute maximum TJ of 150°C can affect reliability.

The package thermal impedance is calculated in accordance with MIL-STD-883.

ELECTRICAL CHARACTERISTICS

TA = 25°C

PARAMETER

VI(on)

On-state input voltage

TEST

FIGURE

Figure 6

TEST CONDITIONS

ULN2002A

MIN

TYP

MAX

VCE = 2 V,

IC = 300 mA

II = 250 μA,

IC = 100 mA

0.9

1.1

13

II = 350 μA,

IC = 200 mA

1

1.3

II = 500 μA,

IC = 350 mA

1.2

1.6

VCE(sat)

Collector-emitter saturation voltage

Figure 4

VF

Clamp forward voltage

Figure 7

IF = 350 mA

Figure 1

VCE = 50 V,

II = 0

50

Figure 2

VCE = 50 V,

TA = 70°C

II = 0

100

VI = 6 V

500

IC = 500 μA

ICEX

Collector cutoff current

II(off)

Off-state input current

Figure 2

VCE = 50 V,

II

Input current

Figure 3

VI = 17 V

IR

Clamp reverse current

Ci

Input capacitance

4

Submit Documentation Feedback

Figure 6

VR = 50 V

VI = 0,

1.7

50

1.25

100

50

f = 1 MHz

V

V

V

μA

μA

65

0.82

TA = 70°C

2

UNIT

25

mA

μA

pF

Copyright © 1976–2013, Texas Instruments Incorporated

Product Folder Links: ULN2002A ULN2003A ULN2003AI ULN2004A ULQ2003A ULQ2004A

ULN2002A, ULN2003A, ULN2003AI, ULN2004A

ULQ2003A, ULQ2004A

www.ti.com

SLRS027M – DECEMBER 1976 – REVISED FEBRUARY 2013

ELECTRICAL CHARACTERISTICS

TA = 25°C

PARAMETER

TEST

FIGURE

TEST CONDITIONS

ULN2003A

MIN

TYP

ULN2004A

MAX

MIN

TYP

IC = 125 mA

VI(on)

On-state input voltage

Figure 6

VCE = 2 V

2.4

IC = 250 mA

2.7

6

IC = 275 mA

7

ICEX

Collector cutoff current

8

II = 250 μA,

IC = 100 mA

0.9

1.1

0.9

1.1

II = 350 μA,

IC = 200 mA

1

1.3

1

1.3

II = 500 μA,

IC = 350 mA

1.2

1.6

1.2

1.6

Figure 1

VCE = 50 V,

II = 0

50

50

Figure 2

VCE = 50 V,

TA = 70°C

II = 0

100

100

Figure 5

VF

Clamp forward voltage

Figure 8

IF = 350 mA

II(off)

Off-state input current

Figure 3

VCE = 50 V,

TA = 70°C,

VI = 6 V

50

VI = 3.85 V

II

Input current

Figure 4

2

65

1.7

50

0.93

Clamp reverse current

Ci

Input capacitance

Figure 7

VI = 5 V

VR = 50 V

VI = 0,

μA

TA = 70°C

f = 1 MHz

2

V

μA

65

1.35

VI = 12 V

IR

V

500

1.7

IC = 500 μA

V

3

IC = 350 mA

Collector-emitter

saturation voltage

UNIT

5

IC = 200 mA

IC = 300 mA

VCE(sat)

MAX

15

0.35

0.5

1

1.45

50

50

100

100

25

15

25

mA

μA

pF

ELECTRICAL CHARACTERISTICS

TA = 25°C

PARAMETER

VI(on)

On-state input voltage

TEST FIGURE

Figure 6

ULN2003AI

TEST

CONDITIONS

VCE = 2 V

MIN

TYP

IC = 200 mA

2.4

IC = 250 mA

2.7

IC = 300 mA

VCE(sat)

Collector-emitter saturation voltage

Figure 5

II = 250 μA,

IC = 100 mA

II = 350 μA,

II = 500 μA,

II = 0

ICEX

Collector cutoff current

Figure 1

VCE = 50 V,

VF

Clamp forward voltage

Figure 8

IF = 350 mA

II(off)

Off-state input current

Figure 3

VCE = 50 V,

II

Input current

Figure 4

VI = 3.85 V

IR

Clamp reverse current

Figure 7

VR = 50 V

Ci

Input capacitance

Copyright © 1976–2013, Texas Instruments Incorporated

VI = 0,

MAX

V

3

0.9

1.1

IC = 200 mA

1

1.3

IC = 350 mA

1.2

1.6

50

1.7

IC = 500 μA

UNIT

50

15

V

1.35

mA

50

μA

25

pF

Submit Documentation Feedback

Product Folder Links: ULN2002A ULN2003A ULN2003AI ULN2004A ULQ2003A ULQ2004A

μA

μA

65

0.93

f = 1 MHz

2

V

5