Lecture 13 Pin config

Lecture XIII 8086 Pin configuration

Wisam I Hasan

Objectives:

Upon completion you will be able to:

1.

2.

Describe the 8086 pins

Understand µp DC c/cs and fan out to logic families

3.

4.

Use clock generator chip (8284A) & how to provide clock to µp

Connect buffers & latches to the buses

5.

6.

7.

interpret timing diagram

Describe wait states & connect circuitry to various number waits

Describe the difference between MIN & MAX modes

Microprocessors

Wisam I Hasan 2

Pin out of

8086

Microprocessors

Wisam I Hasan 3

Pin description

40 – pin dual in line packages (DIP) (what is differences with

8088?)

8086 is a 16 bit

µp (16 for both data and address) ; pins

AD

0

to AD bus.

15

{address & data} multiplexed address/data

During first clock cycle AD

0 bits of address.

to AD

15 are the low-order 16

The other 4 lines (to form 20) Are multiplexed with the status signals; A

16

/S

3

, A

17

/S

4

, A

18

/S

5

, and A

19

/S

6

.

During the first clock period of a bus cycle (read or write cycle), the entire 20-bit address is available on these lines

During all other cycles for memory and I/O operations, AD

AD

15 contain the 16-bit data and S become status lines

0

to

3

, S

4

, S

5

, and S

6

Microprocessors

Wisam I Hasan 4

continued

A

16

/S

3

& A

17

/S

4

lines are decoded as follows:

function

0 0 Extra segment

0 1

1 0

Stack segment

Code or no segment

1 1

Data segment

So by decoding these lines and the using the decoder outputs as chip selects for memory chips, up to 4 MB

(1 MB per segment) can be provided

This mechanism provides a degree of protection by preventing erroneous write operation to one of the segment and destroying information in that segment

Microprocessors

Wisam I Hasan 5

Continued

A

18

/S

5

and A

19

/S

6

are used as A

18

and A

1 st clock period of instruction execution.

19

during the

If an I/O instruction is executed they stay LOW during the 1 st clock period (why?)

During all other cycles; A

18

/S

5

indicates the status of the 8086 interrupt enable flag and A

19

/S

6

becomes S

6 and a LOW on this pin indicates that 8086 is on the bus.

During a hold acknowledge clock period, 8086 tristates the A

19

/S

6

pin thus allows other to take control of system bus

The 8086 tristates AD

0

to AD

15

during interrupt acknowledge or hold acknowledge cycles

Microprocessors

Wisam I Hasan 6

Power Supply requirements

Requires + 5.0 V with tolerance of +-

10%

Draws a maximum supply current of 350 mA

Operates from 0-82 C ambient temperature

Other versions to increase range such as 80C86 CMOS version which requires

10 mA and work at temperatures -4 to

107 C

Microprocessors

Wisam I Hasan 7

DC c/cs

I/P c/cs

O/P c/cs

It is impossible to connect without knowing the I/P & O/P current capability

I/P c/cs is compatible to all standard logic

Standard logic 0 is 0.40 V (difference 0.05 V)

The difference reduces the noise immunity level 400 mV (0.8 –

0.45) to 350 mV 1

This reduce noise immunity may result problem with long wires or too many loads.

It’s recommended that no more than 10 O/P voltages to a single pin without buffer

Microprocessors

Wisam I Hasan 8

Continued

The table below lists some of the common logic families & the recommended fan out from 8086

The best of component type is an LS, 74ALS, 74HC

Refer to page 287-288 for detailed pin configuration

Microprocessors

Wisam I Hasan 9

Some of the pin functions

BHE/S

7

is used as BHE (bus high enable) during the 1 cycle of instruction execution. st clock

The 8086 outputs a LOW on this pin during read, write, and interrupt acknowledge cycles in which data are to be transferred in a high-order byte (AD

15

-AD

8

) of the data bus.

BHE can be used in conjunction with AD0 to select memory banks 1

During all other cycles, BHE/S

7 is used as S7, and the 8086 maintains the output level (BHE) of the 1 st clock cycle on this pin

RD is LOW whenever the 8086 is reading data from memory or an I/O lactations

TEST is an output pin and is only used by the WAIT instruction.

The 8086 enters a wait state after execution of WAIT instruction until a LOW is seen on TEST pin.

INTR is the maskable interrupt input 2 .INTR must be held at HIGH level until recognized to generate interrupt

Microprocessors

Wisam I Hasan 10

RESET pin

The system reset input signal

Must be HIGH for at least 4 clock cycles to be recognized 1 .

It causes the 8086 to initialize registers DS, SS, ES, IP, and flags to all zeros. It also initializes CS to FFFF H.

Upon removal of the RESET signal from this pin 8086 will fetch its next instruction from 2 ?

When the 8086 detects the +ve going edge of a pulse on

RESET, it stops all activities until the signal goes LOW.

When RESET is LOW initializes the system as follows

8086 component

Flags

IP

CS

DS

SS

ES

Queue

Microprocessors

Wisam I Hasan

Content

Clear

0000H

FFFFH

0000H

0000H

0000H

Empty

11

How to generate RESET signal

Using 8284; which has a

Schmitt trigger input

(RES) for generating

RESET from LOW active external reset.

To generate reset from power up, the reset input must remain below 1.05

V for 50 µs after Vcc has reached the minimum supply voltage of 4.5 V.

(see fig 8-4 p.293 Barry)

Microprocessors

Wisam I Hasan 12

The 8284A Clock Generator

The 8284A is an Auxiliary component to the 8086 µp

Without the clock generator, many additional cct. Are required to generate the clock (CLK)

The 8284A provides the following functions or signals:

Clock generation

RESET synchronization

TTL level peripheral clock signal

Fig. 8-2 p291 Barry. Illustrate the pin configuration of 8284A

Microprocessors

Wisam I Hasan 13

The internal structure of 8284

Microprocessors

Wisam I Hasan 14

The operation of clock section

Microprocessors

Wisam I Hasan 15

Operation of RESET section

Microprocessors

Wisam I Hasan 16

Microprocessors

Wisam I Hasan 17

Microprocessors

Wisam I Hasan 18

Microprocessors

Wisam I Hasan 19

Microprocessors

Wisam I Hasan 20

Fully buffered 8086

Microprocessors

Wisam I Hasan 21

Microprocessors

Wisam I Hasan 22

Simplified Write Cycle

Microprocessors

Wisam I Hasan 23

Microprocessors

Wisam I Hasan 24

Simplified Read Signal

Microprocessors

Wisam I Hasan 25

Microprocessors

Wisam I Hasan 26

Microprocessors

Wisam I Hasan 27

Microprocessors

Wisam I Hasan 28

Microprocessors

Wisam I Hasan 29

Microprocessors

Wisam I Hasan 30

Microprocessors

Wisam I Hasan 31

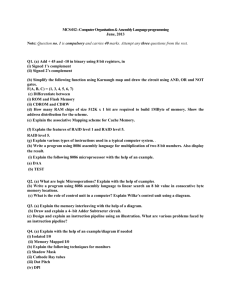

HW

1.

2.

Find the equivalent equation to describe the clock generating section in terms of R, C, V, and t.

Study the systems of the stepper motor and the temperature control system thoroughly and give your feedback in at least 5 points.

Microprocessors

Wisam I Hasan 32