Steven D. Pyle - Ronald F. DeMara

advertisement

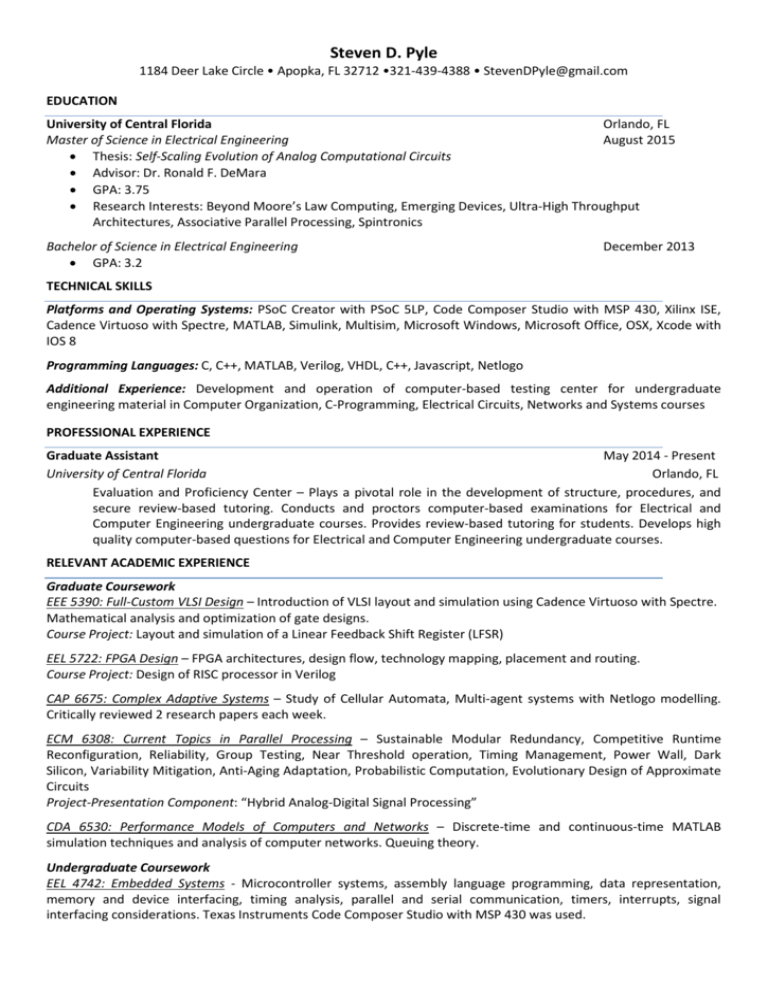

Steven D. Pyle 1184 Deer Lake Circle • Apopka, FL 32712 •321-439-4388 • StevenDPyle@gmail.com EDUCATION University of Central Florida Orlando, FL Master of Science in Electrical Engineering August 2015 • Thesis: Self-Scaling Evolution of Analog Computational Circuits • Advisor: Dr. Ronald F. DeMara • GPA: 3.75 • Research Interests: Beyond Moore’s Law Computing, Emerging Devices, Ultra-High Throughput Architectures, Associative Parallel Processing, Spintronics Bachelor of Science in Electrical Engineering • GPA: 3.2 December 2013 TECHNICAL SKILLS Platforms and Operating Systems: PSoC Creator with PSoC 5LP, Code Composer Studio with MSP 430, Xilinx ISE, Cadence Virtuoso with Spectre, MATLAB, Simulink, Multisim, Microsoft Windows, Microsoft Office, OSX, Xcode with IOS 8 Programming Languages: C, C++, MATLAB, Verilog, VHDL, C++, Javascript, Netlogo Additional Experience: Development and operation of computer-based testing center for undergraduate engineering material in Computer Organization, C-Programming, Electrical Circuits, Networks and Systems courses PROFESSIONAL EXPERIENCE Graduate Assistant May 2014 - Present University of Central Florida Orlando, FL Evaluation and Proficiency Center – Plays a pivotal role in the development of structure, procedures, and secure review-based tutoring. Conducts and proctors computer-based examinations for Electrical and Computer Engineering undergraduate courses. Provides review-based tutoring for students. Develops high quality computer-based questions for Electrical and Computer Engineering undergraduate courses. RELEVANT ACADEMIC EXPERIENCE Graduate Coursework EEE 5390: Full-Custom VLSI Design – Introduction of VLSI layout and simulation using Cadence Virtuoso with Spectre. Mathematical analysis and optimization of gate designs. Course Project: Layout and simulation of a Linear Feedback Shift Register (LFSR) EEL 5722: FPGA Design – FPGA architectures, design flow, technology mapping, placement and routing. Course Project: Design of RISC processor in Verilog CAP 6675: Complex Adaptive Systems – Study of Cellular Automata, Multi-agent systems with Netlogo modelling. Critically reviewed 2 research papers each week. ECM 6308: Current Topics in Parallel Processing – Sustainable Modular Redundancy, Competitive Runtime Reconfiguration, Reliability, Group Testing, Near Threshold operation, Timing Management, Power Wall, Dark Silicon, Variability Mitigation, Anti-Aging Adaptation, Probabilistic Computation, Evolutionary Design of Approximate Circuits Project-Presentation Component: “Hybrid Analog-Digital Signal Processing” CDA 6530: Performance Models of Computers and Networks – Discrete-time and continuous-time MATLAB simulation techniques and analysis of computer networks. Queuing theory. Undergraduate Coursework EEL 4742: Embedded Systems - Microcontroller systems, assembly language programming, data representation, memory and device interfacing, timing analysis, parallel and serial communication, timers, interrupts, signal interfacing considerations. Texas Instruments Code Composer Studio with MSP 430 was used. 2|Page Steven Pyle EEL 4140: Analog Filter Design – Passive and active analog filter design. Sallen-Key and Butterworth high, low, and band-pass filter design. Current Generalized Immittance Biquad design. RESEARCH EXPERIENCE Masters Thesis May 2014-Present Title – Self-Scaling Evolution of Analog Computational Circuits Mentors – Dr. Ronald F. DeMara, Dr. Azadeh Vosoughi, Dr. Debashis Chanda Developed a method to intrinsically evolve analog computational circuits with a Self-Scaling Genetic Algorithm to improve performance as well as the computationally-tractable range of the hardware Senior Design Title – MaRC S-Park: Magnetic Resonant Coupled Smart Parking Utilized magnetic resonance coupling to wirelessly charge an electric RC car Jan 2013-December 2013 Manuscript accepted to 2015 NASA/ESA Conference on Adaptive Hardware and Systems Computer Architecture Lab, CECS, UCF May 2014 – Jan 2015 Title - Self-Scaling Evolution of Analog Computation Circuits with Digital Accuracy Refinement Mentor – Dr. Ronald F. DeMara 3 Evolution of analog computational circuits (𝑥𝑥 2 , 𝑥𝑥 3 , √𝑥𝑥, √𝑥𝑥 ) to compute solutions and perform range scaling, followed by use of error metric of this circuit for accuracy refinement on reconfigurable digital fabric OTHER EXPERIENCE Volunteer at IEEE Symposium Series on Computational Intelligence 2014 IEEE Computational Intelligence Society Attendee registration and distribution of conference materials Ensured that the services provided by the hosting hotel were of highest quality Resolved any issues that arose with participants Dec 2014 Orlando, FL Customer Service Clerk and Grocery Clerk Jan 2006 – May 2011 Publix Supermarkets Inc. Orlando, FL Delegated tasks with minimal supervision, Took pride in the quality and speed with which tasks were accomplished Trained new employees in store protocols, job responsibilities, food handling, and expectations References Dr. Ronald F. DeMara Professor Department of Electrical Engineering and Computer Science University of Central Florida (407) 823-5916 ronald.demara@ucf.edu Dr. Parveen F. Wahid Professor Department of Electrical Engineering and Computer Science University of Central Florida (407) 823-2610 Parveen.Wahid@ucf.edu John Edison Instructor Department of Electrical Engineering and Computer Science University of Central Florida (407) 823-0159 JEdison@knights.ucf.edu