Particle Detectors Chapter

Muon Cooling technical note Technical Note

P. Jarron EP-MIC

A Macropixel Silicon Tracker

Introduction

A macropixel silicon detector is proposed for the muon tracking of the Muon Cooling Experiment. It consists of 4 modules of two planes, each plane containing an array of ladder assemblies of readout chips on silicon sensors. The sensors are patterned with pixels of 0.25mm or 0.5mm dimensions. In the hybrid pixel configuration, the readout chips are bump-bonded to the silicon sensors.

Minimum radiation length is the crucial design issue of the muon tracking detector, and therefore minimum thickness and radiation length are the main constraints on the mechanical construction, which should be extremely light. Realistic assumptions for the smallest feasible thickness are around 150 microns for the Si sensor wafers, and

200um (possibly down to 150um) for the readout die from thinned pixel chip wafers, respectively.

It is proposed to adopt the Si sensors and readout chip of the ALICE hybrid pixel detector, already in an advanced testing stage, for the construction of this detector. In the present case, pixel detector staves (linear arrays of ladders) need to cover an area of approximately 30cm in diameter. This can obtained by stacking staves of different length in a regular octagonal pattern.

More advanced design solutions such as a MCM-Detector and amorphous-silicon deposited over on-wafer ASIC are more attractive in terms of minimum thickness and coverage, but will require a preliminary R&D effort, over 18 months or so, to evaluate these relatively new technologies and assess their feasibility. The readout electronic concept integrated in the ASIC can be based on the existing circuits developed for the ALICE-LHCb pixel detector and the NA60 fast low noise preamplifier with well established performance. The ASIC development in CMOS

0.25um requires an MPW submission and engineering run before a production run (48 wafers) can confidently be launched.

Configuration of the Macropixel silicon sensor and hybrid module construction

Hybrid based on ALICE pixel design

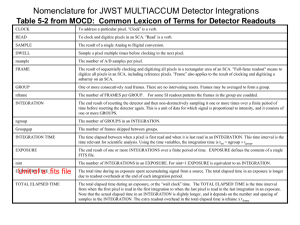

An octagonal array of the required dimension, obtained by stacking ALICE ladders, is illustrated in Fig.1. If this solution is adopted, the most efficient approach would be to use directly the ALICE pixel design, as shown in Fig.2, in collaboration with the ALICE pixel team.

Because of the presence of end of column logic in the readout ASIC, a dead region of ≈ 3 to 4 mm is inevitable, since the staves are not overlapping. This is actually the main limitation of this solution, and it is for this reason that the two other approaches would be more suited to the Muon Cooling experiment.

Hybrid based on square 6cm x 6cm MCM-D silicon sensors

Ideally, 30cm diameter silicon sensor without dead region is preferable (Why?). A MCM-D construction offers the possibility to build a 6cm x 6cm silicon sensor area without dead area, only a small distance of few hundred micron in between 6cm MCM-D modules would remained. However, this approach requires the fabrication of large area

MCM-D without any previous experience of this scale. A design – not yet completed – has been developed for the

ATLAS pixel detector with a MCM-D size of Xcm, but further R&D effort is necessary to develop a large MCM-

D module.

Hybrid based on amorphous silicon amorphous sensor

This would be the best possible solution for the Si tracker of the Muon Cooling Experiment, with the minimum radiation length and the improved X-ray rejection. Radiation hardness to a hadron fluence exceeding 10 16 p/cm 2 is also an advantage in the final use of the cooling channel. However, this technology is not yet mature and requires a substantial R&D effort of one year to assess the feasibility of the a-Si:H detector deposition technique on electronic wafer.

Muon tracker layout based on the ALICE silicon pixel ladder

The pixel technology developed by ALICE and the CERN EP-MIC group seems to be suitable for the construction of the muon tracker. The target thickness values could be 150 microns (200um already achieved) for the sensor and

200um for the chip, respectively (a development programme of wafer thinning after bump deposition is well advanced). Each ladder consists of a silicon pixel sensor 70.72 mm x 16.8mm with 5 chips bump-bonded to it. Pixel segmentation is 32 rows of 425micron-pixel length by 256 columns of pixel width of 50 microns. There is a dead sensitive area when ladders are not overlapping corresponding to bonding regions and end of column logic, which is about 4 mm at a pitch of 16.8 mm.

To complete the front-end electronics system, one would also need to adopt from ALICE the PILOT control chip and the GOL serialiser-driver chip. These two chips are located at the edge of each stave, serving one or two ladders.

Figure 1 ALICE silicon pixel ladder 70.72 mm x 16,8mm scale 1/1.

Figure 2 Arrangement of 32 ALICE silicon sensor ladders to form a detector plane with a shape that can be placed in a circular tube. Diameter is about 29 cm. Connections are not shown. Scale ½.

Cooling radiation length

By gas flow. The total power consumption by plane 36 x5 x 0.7W= 126W/plane

Overall cost estimate

FE electrics and sensors

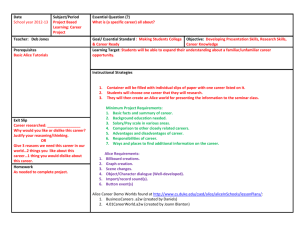

The table below shows preliminary cost estimates based on the following assumptions:

good die yield ≈ 35 % (from ALICE engineering run)

yield of bump bonding and ladders assembly ≈ 60 % (preliminary and probably rather conservative)

spares 25%

Item kEuro

Number Unit cost Cost

Pixel wafer processing & dicing 12 1.5 17.1

Sensor wafer mask

Sensor wafers production

Sensor wafer processing & dicing

Placement

1

14

14

213

2.5

1.5

1.5

0.2

2.5

21.3

20.5

42.5

Cost (1 plane)

Total cost of readout chips, sensors and bump-bonding (4x2 planes)

Other elements

PILOT and GOL chips

substrate hybrid (or flex)

mechanics

cooling

power supplies and cables

DAQ

Very preliminary estimate

Grand Total

103.9

830KEuro

450K Euro

1350K Euro