Lab 8 Seven- Segment Display Module

advertisement

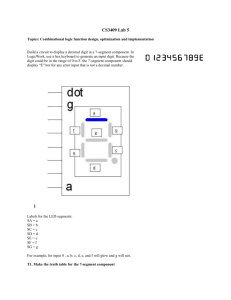

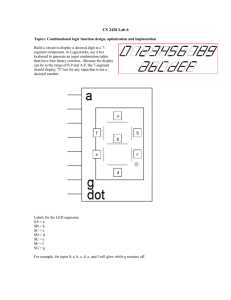

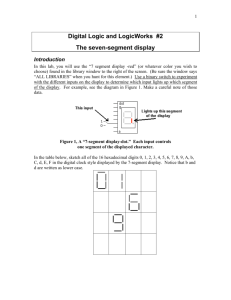

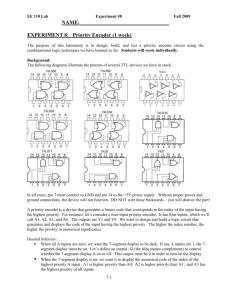

Revised: 3/31/14/GCC CENG 3112 Lab for Digital Circuits Experiment 8 Seven- Segment Display Module Purpose: The purpose of this lab is to design and implement a 7-segment display using Multisim and also to implement it in VHDL module . Prelab : 1. Draw the truth table for the7- segment display that displays BCD numbers (0 to 9), having A , B , C and D as inputs and a,b,c,d,e,f,g as outputs. 2. Using a TTL data book, review 74LS47 (Driver for 7-segment display), design a circuit using 74LS47 and 7- segment display. If your display is common cathodes and you use a 74ls47 as the driver, what do you do to interface the 74ls47 and the 7-segment display? 3. Derive equations from the truth table (using K- map ) for the following: F(A,B,C,D) = function for a, etc. 4. When you realize these circuits at the same time what do you expect the result to be? Verify your answer using truth tables. Equipment: Multisim NiElvis CPLD Xilinx Software I.Laboratory Procedure (Multisim): Part 1: Simulation Using Multisim construct a circuit that consists of the word generator and the logic analyzer. You will find these under the "Instruments" button. Set up: Word generator: Set the word generator to internal clocking with the frequency of 1 KHz. Select an initial address of 0000 and set the final address to 000F. Set the pattern to count up. This will generate a timing diagram that shows all possible combinations of the inputs. Logic analyzer: Set the logic analyzer to internal clocking with the frequency of lKHz and set the clocks per division to 2. Connect the outputs of the word generator to the logic analyzer and run the simulation. Verify that the output is that of a mod 16 counter. Revised: 3/31/14/GCC NOTE: 1. For this experiment set the clock to 1 Hz. 2. 7-segment displays have a common anode or a common cathode. (use the common anode with the 74ls47 and a common cathode for the 74ls48. 3. Tie the ground to ground; other leads ((Test Input)’, (Blanking)’, and so on.) need to be high. Revised: 3/31/14/GCC Part 2: Discrete Circuit Implementation. Implement the circuit that you designed in the Prelab section . Verify that the output of 7-segment display matches with your truth table. Demonstrate your output to the TA and print a copy of the circuit . 1 Note: the chips are common cathode and the 4511 will work with them. II. Laboratory Procedure (VHDL) Part 1. Simulation Open the Project Navigator window to start a new project in Xilinx. Using the tutorial as a guide, follow the steps to design the 7-segment display circuit. Make sure to write the VHDL equations in your VHDL Module so that you may be able to simulate and view the waveform. After having the VHDL code tested, make sure to run ISE-Simulator. View the waveform and test it against your truth table. Print a copy for your lab book. Remember that the testbench will be for ABC. Part 2. Implementation After simulating the result follow the steps needed to implement the circuit on the CPLD. Be sure to document your steps in your lab book. Have a teaching assistant initial your lab book when you have demonstrated a working circuit. Conclusion: In your lab book, discuss your observations and conclusions and briefly explain whether circuit simulation or actually constructing the circuit is more supportive of your learning and understanding the material.