CSE 140L Lab 1 part 4 turorial

advertisement

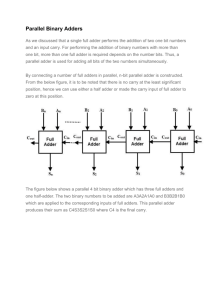

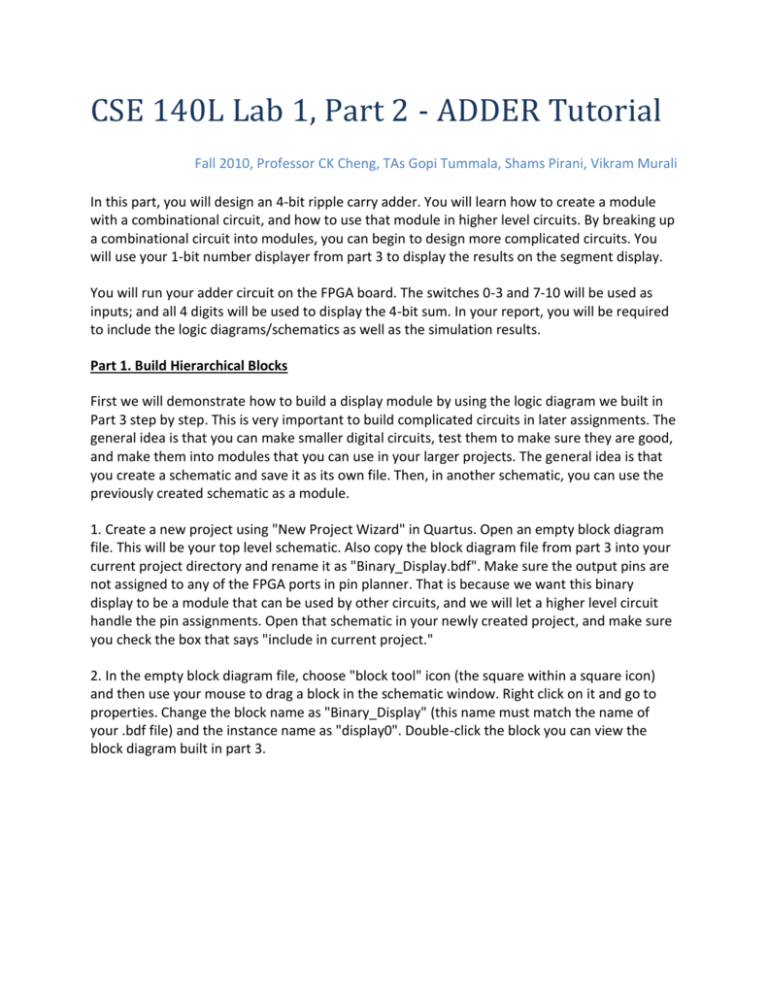

CSE 140L Lab 1, Part 2 - ADDER Tutorial Fall 2010, Professor CK Cheng, TAs Gopi Tummala, Shams Pirani, Vikram Murali In this part, you will design an 4-bit ripple carry adder. You will learn how to create a module with a combinational circuit, and how to use that module in higher level circuits. By breaking up a combinational circuit into modules, you can begin to design more complicated circuits. You will use your 1-bit number displayer from part 3 to display the results on the segment display. You will run your adder circuit on the FPGA board. The switches 0-3 and 7-10 will be used as inputs; and all 4 digits will be used to display the 4-bit sum. In your report, you will be required to include the logic diagrams/schematics as well as the simulation results. Part 1. Build Hierarchical Blocks First we will demonstrate how to build a display module by using the logic diagram we built in Part 3 step by step. This is very important to build complicated circuits in later assignments. The general idea is that you can make smaller digital circuits, test them to make sure they are good, and make them into modules that you can use in your larger projects. The general idea is that you create a schematic and save it as its own file. Then, in another schematic, you can use the previously created schematic as a module. 1. Create a new project using "New Project Wizard" in Quartus. Open an empty block diagram file. This will be your top level schematic. Also copy the block diagram file from part 3 into your current project directory and rename it as "Binary_Display.bdf". Make sure the output pins are not assigned to any of the FPGA ports in pin planner. That is because we want this binary display to be a module that can be used by other circuits, and we will let a higher level circuit handle the pin assignments. Open that schematic in your newly created project, and make sure you check the box that says "include in current project." 2. In the empty block diagram file, choose "block tool" icon (the square within a square icon) and then use your mouse to drag a block in the schematic window. Right click on it and go to properties. Change the block name as "Binary_Display" (this name must match the name of your .bdf file) and the instance name as "display0". Double-click the block you can view the block diagram built in part 3. 3. Right-click the block, choose "Block Properties" in the menu and then "I/O" tab, add the input and output ports you want to have for this block. Here we have only 1 input which is the bit we want to display, and 7 outputs which correspond to the 7 segments in the digit. The port names must be matched with the names of input and output ports in the block diagram file Binary_Display.bdf. So if your original Binary_display schematic was labeled A to G for the outputs and input for the input, you would need to write that for the I/O in the block properties of your block module. 4. You now have a module! From here we can connect the module to additional modules using wires or to output/input pins, similar to what you have been doing before. For the Binary_display, we obviously want to connect the module to output pins, and set those pins to the approrpriate FPGA pins for the segments in digit 0, so create the 7 output pins and assign the pins in pin planner. Save your design. 5. Connect these pins to the block with a wire. Change the type of each wire from "Conduit Line" to "Node Line" by right clicking on the wire segment. Now you need to name the wire. In this case, go ahead and name it something like a_wire (for the a output). Do this by double clicking the wire and making sure the entire wire is selected, and then right clicking and going into properties and giving it that name. 6. Double click each joint point of the wire and the block. In the "Mapper Properties" pop-up window, choose "Mappings" tab and you will see two fields: "I/O on block" and "Signals in node". The name of the first field (I/O on block) corresponds to the module. This field must match the corresponding port name in Binary_Display. The name of the second must be the same as the wire name. Basically you are creating a mapping between the module and the wire. IMPORTANT: Make sure that the second field matches the wire name all the time, otherwise you will get compilation error. 7. Compile your design. You now have made a module, and can use this to connect with other modules. Making the binary display module allows you to focus on the logic of your circuit, rather than on worrying about outputting to the segment digit displays. Also, you can use the same block for all four digits. The only thing that changes is that the output pins of each block would match the actual FPGA pins for that digit. For this project, you will be using all for digits so go ahead and prepare your top level schematic with four of those binary display modules, with each of the modules connected to the correct pin on the FPGA. 8. Right now we do not have anything connected to the binary display module. That is because we want to eventually connect our full adder module to the binary display module. To do this, you follow the steps similar to what we did above for connecting the binary display module to the output pin. We will explain this when we explain how to make your full adder from two half adders. Part 2. Create a Half Adder A half adder has only two inputs: addends A and B, and also produces two outputs: sum S and carry-out Cout. The truth table of a half adder has been given in CSE140 class. The logical expressions of S and Cout can are as follows: Create a new schematic with two gates to build a half adder. We won't attach the binary display modules to your half-adder, because we want to use the half adder as a module for the full adder, which you will do next. Part 3. Create a 1-bit Full Adder from Half Adders Make a new schematic and call it full-adder or something. A full adder has three inputs: two input bits A and B, and a carry-in Cin. The adder adds up the three inputs, and generates a sum bit S and a carry-out Cout. The truth table is also given in class. We can deduce the logic expressions of S and Cout as follows: To understand how we can build the full adder from half adders, one remembers that the two addends A, B, carry-in Cin as well as the sum S are of weight 1, while the carry-out Cout is of weight 2. We first use a half adder to add up A and B, generating an intermediate sum S_int and an intermediate carry-out Cout_int1. We then use another half adder to add up the intermediate sum S_int and the carry in Cin, producing the final sum S and another intermediate carry-out Cout_int2. Cout_int1and Cout_int2 can never be both 1, hence are ORed together to generate the final carry-out Cout. The logic expression for Cout can be rewritten as: Such a design is pictured in the following figure. Hence, to build a full adder, first use the logic diagram you created for a half adder as a block, then follow the above diagram to construct the full adder. You should now have a schematic that looks something like the above picture. Simulate it to make sure it's correct. To connect the two half adders to each other, we follow steps similar to above. First we want to connect a wire between the sum from the first half adder to the second half adder. Name this wire (something like "wire1" is fine, you can make it more descriptive). Then for each module/wire junction, you want to go to mapping properties and make sure that "I/O on block" matches the port name in the module, and "Signals in node" matches the wire name. In our case, the junction on the first half-adder would probably have "sum" as the I/O on block value and "wire1" as the node value. The junction on the second half-adder would probably have something like "b" or "sum_input_y" or whatever you decided to call your inputs for I/O on block. Something like the above is what you should have. Note, the input and output names here are kind of random, so feel free to name the inputs, outputs, and wires that make sense to you. We aren't done yet however. We want a 4-bit adder. So now at our top level schematic, we want to chain 4 of those 4-bit adders in a row. We connect the 4 bit outputs to the 4 binary display modules we previously created. Because bit 0 has no carry in, you can go ahead and attach a ground-input to the first 1-bit adder. So you would have three schematics, a top level schematic (which must have the same name as your project name) which would be your 4-bit adder, a full adder schematic which contains two half adders connected together, a half adder schematic, and your binary display schematic. The top level schematic should have 4 1-bit full adders chained together, and 4 1-bit binary display modules. All of your pin assignments to connect to the FPGA board will be done on this top level schematic. Compile your design and test it on board. Also perform the functional and timing simulation, as taught in part 1.