IEBL weekly progress report Student Name: Renjie Chen Project

advertisement

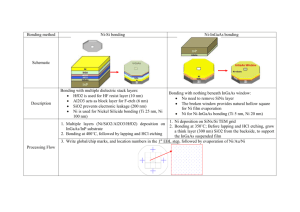

IEBL weekly progress report Student Name: Renjie Chen Project Title: Self-aligned Ni-InGaAs Contact for III-V MOSFET MISFET on Si Week of 07/01/2013 – 07/07/2013 Summary: In the first week arriving at CINT, I finished the training for all the usable equipment. I was qualified to operate ALD, CVD, E-beam evaporator, RTA, lapper, and photolithography equipment. For EBL & SEM, I’m able to use independently now, but haven’t been authorized to book the time (great). I’ll check with Doug and John of their available time for qualification, and during the meanwhile Minh/Daisy will help to book the time. Several runs of Ni-silicide bonding were done in order to check the bonding strength at elevated temperature, but the sample separated during cutting, which is due to the large thickness of InGaAs/InP wafer compared with the small bonding area. Lapping needs to be done before cutting the cross-section (This is an important point; I hope this provides the solution for the problem; we will need to cap the surface with InP or InGaAs during the heating experiments). Ni-InGaAs bonding was also tested on both planer Ni film and PL patterned Ni lines, the former was bonded at 250 °C for 20 min while the later was not. Previously in NTU, the patterned bonding issue was solved by double layer photoresist and elongated bonding time in order to get ride of resist residuals. Ni-silicide bonding: I followed daisy’s recipe for Ni-silicide bonding, and tried to get familiar with this fabrication flow and figure out the steps that needs more attentions. What is the thickness of the Ti/Ni layers? How did you clean the samples? The first two runs were was not successful. If the operation is slow while clipping InGaAs/InP and Si together after BOE dip, or if the surface is not cleaned properly, the silicidation bonding will not happen. I also observed the separation between HfO2 and SiO2, because I forgot to run a conditioning recipe for SiO2 CVD growth after other users running different recipe. Figure 1: Failed Ni-silicide bonding with the separation in between SiO2 and HfO2. Microscope image of Si surface shows the bonding area, and the golden color indicates the SiO2 while red color indicates the HfO2. Several dusts on top are the bonded islands. After modifying each step, the bonding was successful. However, when I’m trying to cut the cross-section and test bonding strength at elevated temperature, the sample separated during cutting. I think this is because the bonding area is too small compared with the IEBL weekly progress report large thickness of InGaAs/InP wafer. Lapping needs to be done before cutting the crosssection. Several more bonded samples have been prepared, and the annealing test will be done in tomorrow. Please test one sample directly at 500 C for ½ hour without cutting. Figure 2: Separation of Ni-silicide bonding during cutting. Red color on top of Si wafer is the HfO2, indicating all the HfO2/SiO2/Ni has been transferred to the Si side. good Ni-InGaAs bonding: Ni-InGaAs bonding was also tested on both planer Ni film and PL patterned Ni lines. The former was bonded at 250 °C for 20 min, while the later was not successful even at 250 °C for 1 h. Figure 3: Microscope image of InGaAs bonded with planer Ni film after lapping. Why does it look so dark? Any roughness on surface or is it totally consumed with NiInGaAs Photolithography patterned Ni lines After bonding at 250 °C for 1h Figure 4: The patterned Ni lines was were clean from microscope, while the bonding with InGaAs failed even at 250 ℃ for 1h. Some dirt can be observed IEBL weekly progress report after bonding, which might be the photoresist residuals coming out during annealing. Was the NiOx removed by NH4OH? How soon was this done before the bonding? Previously in NTU, the patterned bonding issue was solved by double layer photoresist and elongated bonding time in order to get ride of resist residuals. I’ll also try to modify the lithography and annealing condition with current equipment. Yes, make sure first that sample suface preparation and cleaning are identical? Plan for Next Week: - Do lapping to the bonded Ni-silicide samples that I currently had, and then cut cross-sections for annealing test. - Take some Ni-silicide bonding samples to carry on the later on processes, in order to get familiar with EBL writing, RIP what etching? etching, gate definition, and measurements. - Observe TEM operation whenever I have time, and I might also try to learn FIB for future TEM sample preparations. Fellow follow Dr. Minh with the procedure to fabricate devices on TEM grid. - Design the photo-mask for self-aligned Ni-InGaAs project, and try to go through the alignment with EBL to write S/D and later on gate. Hope it can be finished within this week. Here the drawing of the designed patterns, expecting i am looking forward to for your suggestions.