docx - Mars at UMHB - University of Mary Hardin

advertisement

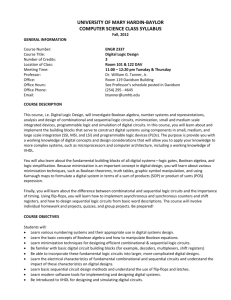

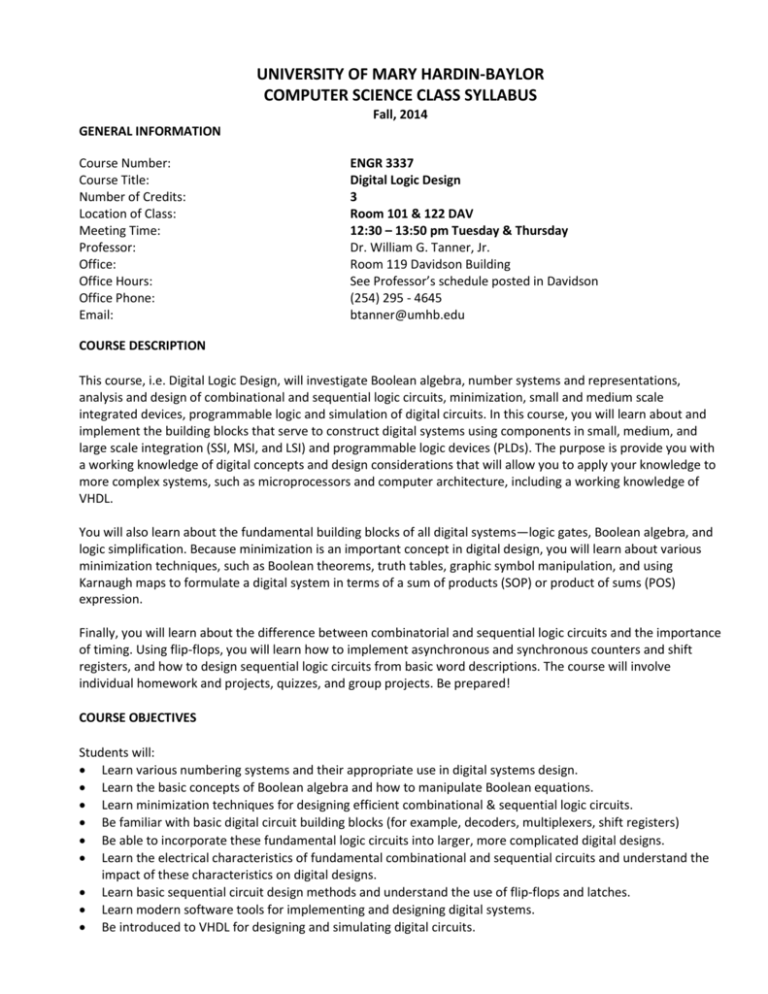

UNIVERSITY OF MARY HARDIN-BAYLOR COMPUTER SCIENCE CLASS SYLLABUS Fall, 2014 GENERAL INFORMATION Course Number: Course Title: Number of Credits: Location of Class: Meeting Time: Professor: Office: Office Hours: Office Phone: Email: ENGR 3337 Digital Logic Design 3 Room 101 & 122 DAV 12:30 – 13:50 pm Tuesday & Thursday Dr. William G. Tanner, Jr. Room 119 Davidson Building See Professor’s schedule posted in Davidson (254) 295 - 4645 btanner@umhb.edu COURSE DESCRIPTION This course, i.e. Digital Logic Design, will investigate Boolean algebra, number systems and representations, analysis and design of combinational and sequential logic circuits, minimization, small and medium scale integrated devices, programmable logic and simulation of digital circuits. In this course, you will learn about and implement the building blocks that serve to construct digital systems using components in small, medium, and large scale integration (SSI, MSI, and LSI) and programmable logic devices (PLDs). The purpose is provide you with a working knowledge of digital concepts and design considerations that will allow you to apply your knowledge to more complex systems, such as microprocessors and computer architecture, including a working knowledge of VHDL. You will also learn about the fundamental building blocks of all digital systems—logic gates, Boolean algebra, and logic simplification. Because minimization is an important concept in digital design, you will learn about various minimization techniques, such as Boolean theorems, truth tables, graphic symbol manipulation, and using Karnaugh maps to formulate a digital system in terms of a sum of products (SOP) or product of sums (POS) expression. Finally, you will learn about the difference between combinatorial and sequential logic circuits and the importance of timing. Using flip-flops, you will learn how to implement asynchronous and synchronous counters and shift registers, and how to design sequential logic circuits from basic word descriptions. The course will involve individual homework and projects, quizzes, and group projects. Be prepared! COURSE OBJECTIVES Students will: Learn various numbering systems and their appropriate use in digital systems design. Learn the basic concepts of Boolean algebra and how to manipulate Boolean equations. Learn minimization techniques for designing efficient combinational & sequential logic circuits. Be familiar with basic digital circuit building blocks (for example, decoders, multiplexers, shift registers) Be able to incorporate these fundamental logic circuits into larger, more complicated digital designs. Learn the electrical characteristics of fundamental combinational and sequential circuits and understand the impact of these characteristics on digital designs. Learn basic sequential circuit design methods and understand the use of flip-flops and latches. Learn modern software tools for implementing and designing digital systems. Be introduced to VHDL for designing and simulating digital circuits. COURSE MATERIALS Textbook Stephen Brown and Zvonko Vranesic, Fundamentals of Digital Logic with VHDL Design, 3rd ed. McGraw-Hill Higher Education, 2009. Other items A flash drive is required for this class (a 16 GB drive to a 64 GB USB drive is recommended). COMPUTING LABORATORY Current account on the CSE Server (mars.umhb.edu) will be provided for which you have paid a laboratory fee. Sufficient disk space on the server should be available, but if you wish to maintain a backup copy of your work, you will need to purchase a sufficient number CDRs to do so. COURSE POLICY AND PROCEDURES 1. Grading: The final grade calculation will be reached according to the distribution described on page 68 of the 2009 - 2010 UMHB Catalog. The final course grade will be computed by the following percentages: Class participation & Laboratory Assignments Unit Examinations (3) Final Examination 20% 60% 20% 2. Attendance: Each student is expected to attend ALL scheduled classes and will be held responsible for all class work and assignments. Continued absences will result in an unsatisfactory grade report for the course, e.g. missing more than six sessions. To be counted present, a student must be in the classroom during the scheduled class or lab time for at least 80% of schedule time. 3. Cell phones: Each student will turn off all cell phones at the beginning of class and will not be allowed to be used during any examinations. 4. Examinations: Each student is required to be present for ALL examinations. If an extreme emergency occurs, and you cannot make the examination time, a student should make every effort to contact the professor by email, telephone or in person to receive permission to miss the examination. Permission will be granted only in the case of extenuating circumstances. 5. Makeup examinations: Each student who wishes to take a “makeup examination” must make arrangements with the professor to take the examination. A “makeup examination” must be scheduled during office hours BEFORE the next scheduled examination. If a student fails to seat for a “makeup examination” before the next scheduled examination, that student will receive a ZERO for the examination he/she missed. 6. Assignments: All assignments will be due on the DUE-DATE indicated in the course schedule. They are due at the beginning of a class period. 7. Final Examination: The final examination will be comprehensive and will be requisite for all students. NO MAKEUP WILL BE GIVEN FOR THE FINAL EXAM. SCHEDULE FOR FALL 2014 - ENGR 3337 DIGITAL LOGIC DESIGN Month Date Reading Assignment Text Laboratory Assignment Aug Aug 26 28 Introduction - Syllabus Chapter 1: Design Concepts B&V B&V Introduction Digital Logic Lab 0 Sep Sep 02 04 Chapter 2: Intro. To Logic Circuits Chapter 2: Intro. To Logic Circuits B&V B&V Digital Logic Lab 1 Digital Logic Lab 1 Sep Sep 09 11 Chapter 4: Optimized Implementation Chapter 4: Optimized Implementation B&V B&V Digital Logic Lab 2 Digital Logic Lab 2 Sep Sep 16 18 Chapter 4: Optimized Implementation Chapter 3: Implementation Technology B&V B&V Digital Logic Lab 3 Digital Logic Lab 3 Sep Sep 23 25 Chapter 3: Implementation Technology REVIEW OF CHAP 2 - 4 B&V B&V Digital Logic Lab 4 Digital Logic Lab 4 Sep Oct 30 02 EXAM #1 (Chap 2- 4) Chapter 3: Implementation Technology B&V B&V Digital Logic Lab 5 Digital Logic Lab 5 Oct Oct 07 09 Chapter 5: Number Representation Chapter 5: Number Representation B&V B&V Digital Logic Lab 6 Digital Logic Lab 6 Oct Oct 14 16 Chapter 5: Number Representation Chapter 6: Combinational - Circuits B&V B&V Digital Logic Lab 7 Digital Logic Lab 7 Oct Oct 21 23 Chapter 6: Combinational - Circuits REVIEW OF CHAP 3, 5, 6 B&V B&V Digital Logic Lab 8 Digital Logic Lab 8 Oct Oct 28 30 EXAM #2 (Chap 3, 5, 6) Chapter 7: Flip-Flops, Registers, Count. B&V B&V Digital Logic Lab 9 Digital Logic Lab 9 Oct Nov 04 06 Chapter 7: Flip-Flops, Registers, Count. Chapter 7: Flip-Flops, Registers, Count. B&V B&V Digital Logic Lab 10 Digital Logic Lab 10 Nov Nov 11 13 Chapter 8: Synchronous Sequential Cir. Chapter 8: Synchronous Sequential Cir. B&V B&V Digital Logic Lab 11 Digital Logic Lab 11 Nov Nov 18 20 Chapter 8: Synchronous Sequential Cir. REVIEW OF CHAP 7 - 8 B&V B&V Digital Logic Lab 12 Digital Logic Lab 12 Nov Nov 25 27 EXAM #3 (Chap 5 - 6) THANKSGIVING Dec Dec 02 04 Chapter 9: Asynchronous Sequential Cir. Chapter 9: Asynchronous Sequential Cir. Dec 09 FINAL (Chaps 1 - 8) IN CLASS HOLIDAYS B&V CUMULATIVE EXAM