IEEE Paper Template in A4 (V1)

advertisement

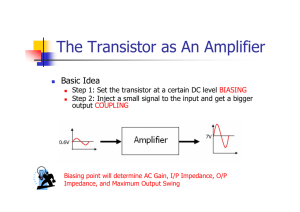

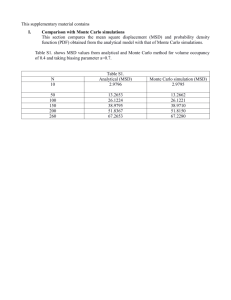

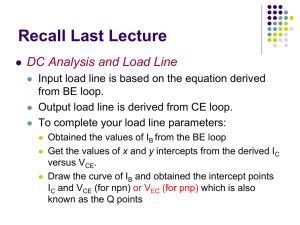

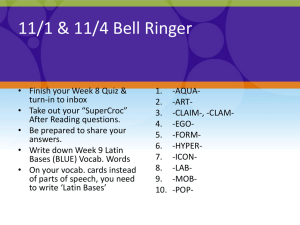

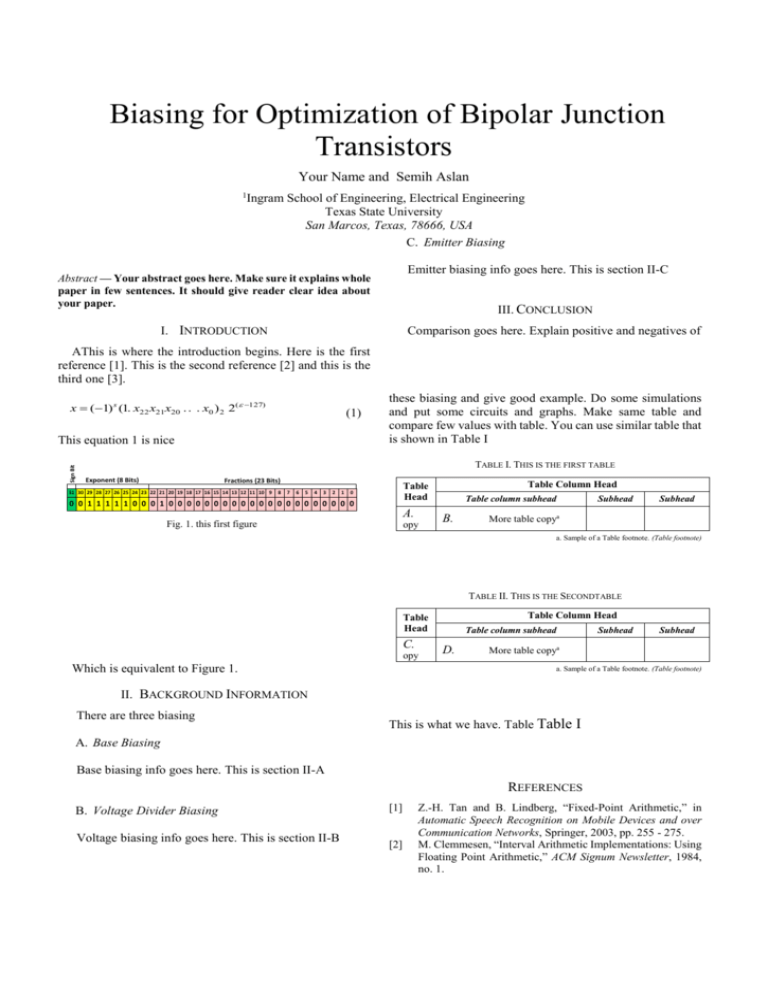

Biasing for Optimization of Bipolar Junction Transistors Your Name and Semih Aslan 1 Ingram School of Engineering, Electrical Engineering Texas State University San Marcos, Texas, 78666, USA C. Emitter Biasing Emitter biasing info goes here. This is section II-C Abstract — Your abstract goes here. Make sure it explains whole paper in few sentences. It should give reader clear idea about your paper. III. CONCLUSION I. INTRODUCTION Comparison goes here. Explain positive and negatives of AThis is where the introduction begins. Here is the first reference [1]. This is the second reference [2] and this is the third one [3]. x (1) s (1. x22 x21x20 . . . x0 ) 2 2( 127) (1) Sign Bit This equation 1 is nice these biasing and give good example. Do some simulations and put some circuits and graphs. Make same table and compare few values with table. You can use similar table that is shown in Table I TABLE I. THIS IS THE FIRST TABLE Exponent (8 Bits) Fractions (23 Bits) 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 Table Column Head Table Head 0 0 0 1 1 1 1 1 0 0 0 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 A. Fig. 1. this first figure Table column subhead c opy B. Subhead Subhead a More table copy a. Sample of a Table footnote. (Table footnote) TABLE II. THIS IS THE SECONDTABLE Table Column Head Table Head C. c opy Which is equivalent to Figure 1. Table column subhead D. Subhead Subhead a More table copy a. Sample of a Table footnote. (Table footnote) II. BACKGROUND INFORMATION There are three biasing This is what we have. Table Table I A. Base Biasing Base biasing info goes here. This is section II-A REFERENCES B. Voltage Divider Biasing Voltage biasing info goes here. This is section II-B [1] [2] Z.-H. Tan and B. Lindberg, “Fixed-Point Arithmetic,” in Automatic Speech Recognition on Mobile Devices and over Communication Networks, Springer, 2003, pp. 255 - 275. M. Clemmesen, “Interval Arithmetic Implementations: Using Floating Point Arithmetic,” ACM Signum Newsletter, 1984, no. 1. [3] E. DUMAN, H. CAN, and E. AKIN, “FPGA Modules for Conversions between Fixed and Floating-point in Quartus-II Environment,” International Journal of Electrical & Computer Sciences, 2010, vol. 10, no. 6, pp. 120-124.