Fabrication of Nanoscale Patterns using Interferometric Lithography

advertisement

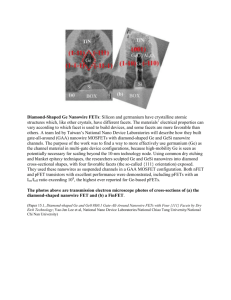

Fabrication of Nanoscale Patterns using Interferometric Lithography By Jay Taylor, Anabil Chauduhri, and Dr. Steve Brueck Introduction: Technology is simply growing smaller and the ability to fabricate or build extremely small components is at the core of the emerging field known as nanotechnology. Most of us have heard of nanotechnology but few know many applications in this field or how these nanostructures can be built. To give the reader a reference to the size that nanotechnology has reached, figure 1 shows a human red blood’s cell compared to the size of a man-made SRAM cell. This SRAM cell consists of eight transistors and is used for memory storage in a computer. [3] The cell was fabricated using a fabrication technique known as photolithography. This technique will be Figure 1 outlined in this paper as well as a similar technique, Interferometric Lithography (IL), which was used for the fabrication experiments described in this paper. In addition to these techniques, three problems that IL can help solve will also be addressed: more efficient solar panels, the fabrication of a green LED source, and the construction of nanowire field-effect transistors. There are two chemicals that make Photolithography and IL possible, a photoresist and its corresponding developing solution, and will be described in the next section. Photoresist: A photoresist is an organic polymer that will change its solubility when exposed to a certain frequency of light. Throughout this paper this frequency is 8.45*10^14 Hz or 355nm. If you recall the energy of a photon is directly related to its frequency, and the energy associated with the photon is responsible for the chemical reaction taking place in the photoresist (E = hv, where E is the energy of this photon h is Planck’s constant and v is the frequency of light). There are two types of photoresist, positive and negative, and each responds to the photons’ energy differently. In a positive photoresist, the polymer, before exposure to light, is in long chains (Figure 2a). The energy within the photon will interact with the polymer and begin to break it down. The smaller pieces of the photoresist are more soluble than the long chain because the pieces have less surface area and exhibit a weaker interaction with the neighboring chains. As a result, the region exposed becomes more soluble and dissolves quicker than the region unexposed. The other type of photoresist is negative photoresist and it works the other way. Before exposure to light, the organic polymer is in smaller pieces (Figure 2b). The energy associated with the frequency of the photon combines the subunits and results in longer chains. These longer chains have more surface area and have a stronger interaction with neighboring chains. As a result the exposed region becomes less soluble than the unexposed region. The Developing Solution corresponds to the photoresist and its purpose is to dissolve the more soluble (i.e. the smaller polymer chains) photoresist. These two chemicals are used to fabricate a large range of structures. The only question that remains is: how do you only expose certain regions of the photoresist to light, while keeping light away from other regions? This is the difference between the techniques of Photolithography and IL. [6] Introduction to Photolithography: Photolithography is the process of using an optical mask to carve patterns into photoresist. An optical mask is a glass slide that has pieces of metal adhered to the underside of the mask. These pieces of metal effectively block the light from shining through the mask. Figure 3 illustrates how this can be used to carve patterns into the photoresist. [6]The photoresist serves as scaffolding to the structures that will be constructed. Once this scaffolding is placed other materials, selected for their optical or electrical properties can replace this scaffolding. This techniques work well, but there are several limitations to photolithography and is why IL was used throughout these projects. One such Figure 3Metal strips prevent light from passing limitation is that an optical mask can only yield one pattern, through and changing the chemical composition and which works great in industry, when many of the same solubility of the photoresist layer beneath it. This structures need to be produced. In research, however, the altered photoresist can then be developed and a development of identical structures is not always useful. If a new pattern will appear in this layer. structure is desired with this set-up a new optical mask needs to be purchased. Optical masks can get expensive and this approach can easily become very costly. [1]There is also a physical limitation on how narrow the metal strip blocking the light can get. Currently this width is about 1 µm. This limitation can be overcome through the addition of various lenses that will shrink the pattern incident on the photoresist layer, but the addition of these lenses can get expensive. Current exposure tools used in industry are around $40 million -$60 million.[1] Industry because of its larger budget and need to produce identical patterns can ignore these limitations, but for research purposes these limitations cannot be ignored and is the reason throughout these experiments Interferometric Lithography was used instead. Interferometric Lithography (IL): Instead of blocking the incident light with metal, IL uses properties intrinsic in light to create regions of low and high intensity. Light can be thought of as a wave and waves have their own unique properties. When two waves come into contact with one another the two waves will combine and this combination is known as interference. This interference results in a new wave containing elements of its two wave components. The new resulting wave is simply the addition of the two wave components’ amplitude at any given point in the wave. For example, if there is a point in space where the two resulting wave corresponds to peaks in the amplitudes than the resultant wave will have a larger or more Figure 4 This shows two waves interfering and where the two waves combine there intense peak, known as constructive interference. Inversely if at are periodic regions of high and low another point in space the resulting wave consists of one wave’s intensity. IL exploits these periodic peak and another wave’s trough then at that point the amplitude or patterns and can be used instead of intensity of that wave will be negligible, known as destructive photolithography to create nanoscale [5] patterns in photoresist.[5] interference. If we take a beam of light and break it up, then force this light to recombine then a periodic and predictable interference pattern will result from this recombination and nanoscale structures can be built.[1]There are multiple ways of breaking up light and forcing it to recombine and in the scope of the experiments carried out in this paper only two were used. The light needed to create this interference pattern ideally contains: one wavelength, is coherent or maintains its phase over a workable distance, and each beam has the same polarization. Laser light has all these characteristics and is used in IL. The first set-up that was used utilizes a Lloyd’s mirror for creating the interference. Light comes from a laser passes through a beam expander, and then part of that expanded beam hits the sample directly and the other part is reflected off of a mirror and then combines with the part of the beam hitting the sample. This technique is good in that by adjusting the angle of that mirror the pitch, or the distance that this pattern repeats, is changed. The pitch of this pattern is calculated by the equation: 𝜆 Pitch = 2𝑛𝑆𝑖𝑛∅ , where λ is the wavelength of the light, n is the refractive index of the medium through which the sample is being exposed and θ is the angle-ofincidence of the light. This set-up has can have pitches ranging from 4µm to 180nm.This is a very powerful tool in fabricating many structures used in microelectronics. A set back to this IL set-up is that if the angle-of-incidence (θ) gets close to zero or close to 90° the interference region also becomes Figure 5 This is the Lloyd’s mirror set- small. This can become a problem, when the application requires a pitch of more than 3µm because the area of interference gets almost too small to up for creating interference patterns. work with. Another technique that keeps the width of interference of practical size is the use of an optical prism. A wide beam of coherent light is shined onto the top of a prism, as illustrated in Figure 6. The prism will then bend this light onto itself creating an interference pattern. When the refracted light leaves the prism, it will bend again and the interference region will enlarge to a point then decrease until it is no more. The pitch of the corresponding interference is modeled by the same formula. [6] Pitch = 𝜆 2𝑛𝑆𝑖𝑛∅ , where λ is the wavelength of the light, n is the refractive index of the material outside the prism and φ is the angle represented in Figure 6. The width of the interference pattern at its widest region is given by the following equation. Figure 6Light will be bent by the prism and this bending will create an interference pattern with an interference region of practical size when a larger pitch is desired. 𝑛𝑖 W tan∅ 𝑛𝑖 𝑊𝐼 = 2[𝑊𝑡𝑎𝑛∅ (𝑡𝑎𝑛 (∅ − arcsin ( sin∅))) + ( − W (tan (∅ − arcsin ( sin∅))) tan(90° − ∅) 𝑛𝑡 4 2 𝑛𝑡 , where WI is the width of the interference, W is the width of the bottom of the prism and φ is the angle shown in the diagram, ni is the index of refraction of the medium outside the prism, and nt is the index of refraction of the prism. The widest part of this interference is found at a distance away from the prism equal to: d= 𝑊 𝑛𝑖 − 𝑊𝑡𝑎𝑛∅ (tan (∅ − 𝑎𝑟𝑐𝑠𝑖𝑛 ( 𝑠𝑖𝑛∅))) 2 𝑛𝑡 , where d is the distance from the prism. These are two ways in which interference patterns can be generated and then used to fabricate nanoscale patterns, which are useful in a variety of applications, but first there are two processing steps that were used throughout these applications that are important to mention. Anti-Reflection Coating (ARC): An Anti-Reflection Coating is used to stop the incident light reflecting off of the substrate and causing additional patterns, or standing wave patterns to appear on the photoresist. Throughout the fabrication in this paper a bottom antireflection was used, which is placed between the photoresist and the substrate. For this antireflection coating to work as designed it needs to be the proper thickness so that the thickness of the light reflected off of the substrate destructively interferes with the light shining through the ARC. Destructive interference only happens when the two interfering rays are out of phase by 180° or π radians, which corresponds to a path length difference of λ/2. The thickness of this film must follow the equation: 𝑡ℎ𝑖𝑐𝑘𝑛𝑒𝑠𝑠 = 1 2 (𝑚+ )𝜆 2𝑛 , where m is any integer, and n is the index of refraction of the ARC. The ARC used here had an index of refraction of 1.81. [13] If m was 0 this corresponded to a thickness of 50nm and if m was 1 this corresponded to a thickness of 150nm. The figure below shows two different photoresist patterns, in one the ARC had the right thickness and in the other the ARC did not have the right thickness. Anti-Reflection coating lengths ~70nm ~150nm Figure 7 On the figure to the left, notice the standing wave patterns along the sides the wall. This is due to the ARC not being the right thickness. The figure to the right the ARC was the right thickness and no standing wave patterns are present. Etching: Etching is the process of removing certain materials from your sample. There is wet etching, which uses chemicals to accomplish this or dry etching which uses plasma. Etching is a common processing step and can be very selective in removing only the desired material away from the sample. [6]This process will not be discussed further in this paper, but it is important to know that etching was researched heavily in order to allow for the fabrication of all three applications that are covered in this paper. Introduction to Photovoltaic Cells: Semiconductors exhibit a phenomenon known as the photoelectric effect, which is the phenomenon that when light is incident onto a material it produces a current. Recall that the amount of energy corresponding to light is equal to: E = hν, where h is Planck’s constant and ν is the frequency of the light. In order for a semiconductor to produce a current the incident photon must have energy greater than the semiconductors band-gap energy. If the incident light has energy less than this band-gap energy, no current will be produced. On the other hand, if the light Figure 8 plots band-gap Energy in eV verses has energy much greater than this band gap energy the excess efficiency and shows some commonly used energy is released as heat. The semiconductors used in solar cells semiconductors band gap energy. [11] have a band-gap energy large enough, so that it obtains the largest amount of electricity from the suns solar spectrum. This corresponds to a band-gap energy of the optimal semiconductor to be about 1.4eV.[2]In the current solar cell market, Silicon is the semiconductor that is most commonly used because it is abundant in the earth and it has an effective band-gap energy for solar cell applications. Figure 8 is a figure plotting efficiency per band-gap energy as well as the associated band-gap energies and efficiencies of commonly used semiconductors for solar cells. The maximum efficiency using just a single semiconductor is under 35%. A set back to silicon is that it has an indirect band-gap. The band-gap energy is the difference between the minimum value of the conduction band and the maximum value of the valence band. These values do not always correspond to the same momentum of the electron. In an indirect band-gap semiconductor, like silicon, the trough of the conduction band is at a different momentum than the peak of the valence band. An electron can still move between the valence band and the conduction band in an indirect band-gap material, but the electron not only must interact with a photon to gain the energy, but it must also must interact with a phonon, or the vibration quanta in the crystal lattice to move into the conduction band. Because three particles have to interact in order for this effect to be observed, indirect band-gaps are always less efficient than direct band-gap semiconductors. In a direct band-gap material the peak of the valence band and the trough of the conduction band correspond to the same momentum in the electron. [30] In order to raise the maximum efficiency of these cells and make them a better source for energy production, several direct band-gap semiconductors are being layered on top of each other so that the band-gaps of multiple semiconductors are utilized and as much electricity can be gathered as possible. Figure 9 The picture to the right represents a direct band-gap and the picture to the right represents an indirect band-gap. Direct band-gap materials are preferred for semiconductor applications. Concentrated Multi-Junction Solar Cells A multi-junction solar cell is a material with different semiconductors layered on top of each other. If larger band-gap semiconductors are placed at the top of the cell then they will only absorb the higher energy light and the lower energy photons will permeate through the cell until it reaches a semiconductor with equal band-gap energy. [11]In theory, if you have an infinite number of direct band-gap semiconductors each which a different band-gap energy, then all of the wavelengths in the suns solar spectrum will get absorbed and converted into electricity. However, an infinite number of semiconductors is impractical and these semiconductors can get fairly expensive, so what is commonly done is only a few semiconductors are selected and a lot of that semiconductor material is replaced with optical material as to concentrate the light onto the multi-junction semiconductor and this is what is known as a Concentrated Multi-Junction Solar Cell. [15] With a Concentrated Multi-Junction system, recorded breaking efficiencies have been achieved. Carlos Algora has demonstrated a record breaking dual-junction solar cell of GaInP/GaAs with an efficiency of 32.6% concentrated at 1000 suns.[16] Currently they are working on a triple-junction GaInP/GaInAs/Ge cell that theoretically can get efficiencies up over 40%.[15] Cost is still somewhat of a factor with these concentrated multi-junction solar cells and currently these cells will be applied to space technologies, but as efficiency increases and manufacturing and installation costs decrease then these cells will be more available for terrestrial applications. Figures 8 and 9 give a glimpse into the cost and efficiencies of concentrated multi-junction solar cells. [15] Figure 10 As efficiency and concentration increases cost per Watt of power produced decreases and will continuously decrease the more Watts that are produced.[15] Figure 11 This shows the theoretical efficiencies of 2 junctions and infinite junction solar cells and then how the resistance of the semiconductors hurt efficiency at high concentration.[15] Fabrication of Multi-Junction Photovoltaic Cells: A solar cell consists of a top and bottom metal contact with the semiconductor material between them. The idea of the photovoltaic cell is to send electrons to the bottom contact. By doing this a potential difference between the top and bottom metal contact is created and a current is produced. This is essentially what is done in a battery and is why for many years a solar panel was known as a solar battery. To get the electrons to flow down the semiconductor material diode junctions are put in between the different layers of semiconductor material. These junctions are simply semiconductor material with impurities spread out in them designed to influence the flow of electrons in the semiconductor, called doping. This junction acts as a diode meaning that electrons are forced to flow in only one direction. Practically that means that there are two layers each doped differently with the p-doped on top of the N-doped material, current always flows from a p-doped material to an n-doped material. [16]Figure 10 shows a representation of what I have described. Figure 12 The figure to the left shows a crude diagram of Carlos’ Multi-Junction solar cell and the figure to the left shows the suns solar spectrum. The band gap energies of the semiconductor absorb a range of the suns energy which has been correlated next to the band gap energy listings. The fabrication process was a collaboration effort between the Center of High Technology Materials (CHTM) at the University of New Mexico and the Instituto de Microelectrónica de Madrid (IMM) at the National Centre for Microelectronics in Madrid Spain. The process begins in Spain by the creation of the semiconductor material. This material is grown by molecular beam epitaxy (MBE), which grows the different semiconductor layers in a very ordered and controlled manner. Currently, the samples that were fabricated only contained a single GaAs layer, so that the Spain group can optimize their processing steps before the more expensive triple junction substrate material is used. Next a layer of SiO2 is grown, which is an insulating material that will later be etched away. The samples were then shipped to New Mexico. A layer of Anti-reflection coating followed by a layer of Photoresist will be added on top of the SiO2. IL will then be used to create nanoscale patterns at a 2.5µm pitch with a critical dimension of 300nm. This sample will then have a thin layer of chromium deposited on top and then Acetone will be used to remove the photoresist gratings, so the remaining sample will have trenches where the photoresist patterns used to be and a chrome layer where there were previously no photoresist. An illustration of these processing steps is shown below: Figure 13 This is an illustration of the process flow that was carried out at the Center for High Technology Material (CHTM). After this step the sample was then shipped back to Spain for additional processing steps. In the diagram the place where this step was done is listed, IMM is the Instituto de Microelectrónica de Madrid. Figure 15 Fabrication processes by the Spain collaborator The finished product has four isolated solar cells with metal contacts on the top and bottom of the cell. The small wires between the two top metal contacts were produced by IL and are approximately 300 nm in width and are spaced 2,500nm apart. These patterns were fabricated using the Lloyd’s mirror set-up, which constituted an angle-of incidence to be 4°. This was done successfully and the samples were mailed to Spain on July-2-2012. The center in Spain is now currently working to optimize their processing steps. Below are two images showing two different processing steps done at the CHTM. Figure 16 This is are Scanning Electron Microscope picture of the samples being shipped to Spain at two different legs in the fabrication process. On the left this is after the samples have been exposed and developed by the photo resist. To the right, this is the sample after chrome deposition and photoresist Lift-off. The dimensions of these samples are a 300nm CD and a 2.5µm pitch. Light Emitting Diodes (LED): Figure 17 This is a basic representation of the movement of electrons and holes in a LED. Electrons and holes combine and the electron will move to a lower energy level releasing photons. This effect is short lived without a current flowing throughout the material. The second project of this summer was the fabrication of a Light Emitting Diode (LED) source capable of lasing green light. Before the fabrication process is outlined, a brief outline of LEDs is presented. The most commercially available type of LED is a semiconductor diode that emits light when an electron meets a hole and the electron falls into a lower energy level. This occurs because when an electron falls from its conduction band to the valence band it releases energy in the form of electromagnetic radiation. This electromagnetic radiation is only observed, when the band-gap energy, or the energy difference between the conduction band and the valence band, is between 3.1eV to 1.7eV. This corresponds to electromagnetic radiation between 400nm -750nm, which is in the visible spectrum. [21] This combination of electrons and holes can be expedited, when an n-doped semiconductor, which has an excess of electrons, is placed next to a p-doped material, which has an excess of holes, as seen in Figure 13a. Electrons and holes near this p-n junction will combine and photons will be released. This effect is short lived, unless there is a potential difference across the junctions to create a current, like figure 13c. Electrons will then continue to meet with holes and when they meet electromagnetic radiation will continuously be released, resulting in a light source. [21] The research in LEDs is primarily with regard to engineering semiconductors with band-gap energies between 3.1eV and 1.7eV, which corresponds to visible light. This has been the subject of LED research for the past few decades and a lot of progress has been made. Red LEDs commonly use an AlGaInP or a AlGaAs source and blue LEDs use a InGaN source. These are good sources for LEDs not only because they have the right band-gap energy to for their respective colors, but they also have a direct band-gap, which increases their efficiency to emit light. A less efficient way to produce other colors is to introduce a phosphor into the diode. This takes higher energy light and through the process of fluorescence emits lower energy light. Fluorescence by its nature is always going to result in a decrease in efficiency because a higher energy photon is absorbed and remitted as lower energy light and that left over energy is given off as heat. This is how commercial green and yellow LEDs emit light. [22] A white LED is simply the overlap many LED colors. The push for direct green LEDs would result in high efficiency white LEDs. The efficiency of converting electricity into light is a huge concern within the U.S. Department of Energy as 18% of the total electricity used by the United States is used to light our homes and businesses. [30] If more efficient lighting sources can be produced and used than this percent will lessen and money can be saved. To give an idea of efficiency in common home lighting sources: incandescent bulbs are at most 4% efficient, Fluorescent bulbs are about 12% efficient[18], and if a direct green LED would be fabricated, then these LEDs would be close to 50% efficient. The DOE pushes for more efficient lighting sources because if a direct green LED source can be produce and this technology replaces all incandescent and fluorescent lights than this would reduce the world’s total energy consumption for lighting by 25% which translates to roughly $15 billion in the first year alone and $120 billion over a 20 year span. [19] This obviously has huge economic implications, but the problem remains in fabricating green LED sources. Data has suggested that cubic-GaN can be a great green LED source, however, c-GaN does not grow regularly at practical temperatures, but it has been grown in between hexagonal-GaN by a process known as metal organic vapor-phase epitaxy. GaN typically forms in a hexagonal crystalline arrangement but with this technique, cubic-GaN can be grown [23] and this process is outlined below. Fabrication of potential green LED emitters The fabrication begins with a silicon wafer and a layer of ARC and photoresist is coated than exposed at about 2.5° to give a pitch of 4µm. ARC was then etched away by CF4 plasma, then the sample was coated in chrome and acetone lift-off was done to remove the photoresist. The remaining ARC under the PR patterns were etched away and then the bare silicon was etched using a 40% KOH solution at 60°C to obtain v-grooves. These grooves are about 800nm wide and approximately 550nm deep and spaced 4µm a part. The chrome was then removed using a chrome etchant. Hexagonal Gallium Nitride (h-GaN) was then grown in the grooves and Cubic Gallium Nitride (c-GaN) was then able to grow between the two layers of hexagonal-Gallium Nitride. This whole process is seen in figure 14. Figure 18 The above fabrication process should work just fine based off the literature and previous work done at the University of New Mexico, but it did not work out as well as hoped. Problems primarily arose during process 6, the KOH etching stage, where the silicon was etched primarily at the edge of the silicon gaps and not in the middle. It was found that better patterns worked if a layer of Antireflection coating was placed below the layer of photoresist, expose the sample than etch the ARC layer using CF4 plasma. The CF4 selectively etches only the ARC and not the photoresist, then a layer of chrome were to be placed, lift-off be done and then finally the KOH etch then the chrome etch. This method gave us better V-grooves that could be used to eventually grow the cubic-Gallium Nitride. This is illustrated in figure 15. Figure 19 Picture to the right is the fabrication process without the addition of ARC and the picture to the right is the process with the ARC. As seen the process with the arc results in better v-groove formation. One issue with the v-grooves that still needs to be worked out is the evenness of the etching within the grooves. The small lines that are seen within the groove need to be removed before the GaN can be grown. These inconsistencies are believed to be caused by improper alignment of the wafer before IL. KOH works by etching along the <1, 1, 1> face of crystalline silicon. This refers to the miller index of the three dimensional plane of the crystal lattice structure. [31] If the samples are aligned properly the <1, 1, 1> face of silicon should be consistent throughout the entirety of the groove. Previously as cubic-GaN has been grown with the presence of these grooves and the resulting c-GaN wires have been non-uniform and additional processing steps have been more difficult to do with the non-uniform c-GaN nanowires. Once uniform grooves have been fabricated, then the samples will be shipped to Rensselaer Polytechnic Institute (RPI), where the hexagonal and cubic GaN will be grown. Figure 20 shows illustrations of the final product from previous work done with RPI. The University of New Mexico has previously sent v-groove samples to RPI, which are what the pictures below are from. The grooves were narrower and spaced much closer together than the samples currently being fabricated. Additionally to the GaN growth InGaN quantum wells are placed on top of the c-GaN in order to control the number of photons leaving the nanowire. Figure 20 This shows TEM pictures of cubic-GaN growth. In figure (c) a definite difference in crystal form is observed. The growth of these GaN nanowires and the growth, in the future, are done at Rensselaer Polytechnic Institute. Photoluminescence data of c-GaN that has been previously synthesized has been gathered from the previous samples sent to RPI and suggests that c-GaN nanowires can laze green light, but more data needs to be gathered to confirm these results. The goal of this research was to provide more v-groove samples that were wider and spaced further apart, so that RPI can grow the c-GaN and more photoluminescence data can be gathered. Nanowire based Field Effect Transistors My last project that I was able to be a part of this summer was the fabrication of GaAs Nanowire based Field Effect Transistors. Electronic transport studies of nanowires are both an interesting field of study not only for the advancement of science in general, but also for implications in the electronics industry. [28] The objective of this research is to not only design a way to fabricate these semiconductor nanowire transistors but to also study the effect of high energy Figure 21 This is a representation of a radiation on these intrinsically radiation resistant materials. A nanowire field-effect transistor that this nanowire is essentially a one dimensional electrically conductive research can fabricate material. Much nanowire research has been done by using growing vertical nanowires by techniques such as metal-catalyzed vapor liquid solid (VLS) growth, but an issue is taken these vertical nanowires and integrating them into circuits.[cite] An alternative method that this project is pursuing is growing these nanowires already incorporated in these circuits. Industry has created nanowires 22nm and even 14nm using those $60 million optical steppers, as mentioned earlier. Research with a much lower budget must come up with other ways of designing nanowires on the same scale. In order to create these nanowire transistors, wires must be placed far enough apart so that a source, gate, and drain can be incorporated with the nanowire, illustrated in figure 21. In Interferometric Lithography the more space between the gratings the less narrow these lines become. The limit of the thickness that could be fabricated by just using one exposure at a three micron pitch was around 250nm for the CD. In order to get around this limitation, a double exposure was used to get narrower lines spaced far apart. With this method, a 100nm line with a 3µm pitch was able to be obtained, but the height of these lines was 500nm and these lines toppled over easily. The photoresist was later spun on at higher speeds, which decreased the height of the photoresist layer. Many experiments were completed in order to narrow the lines in the photoresist with just one exposure and what was observed was that there was not enough difference in the intensity of the light below 250nm that could only simply reduce the width of the line without removing line entirely. This double exposure is a way to get a larger change in intensity over a much narrower region, while still getting the separation needed to fabricate the nanowire FETs. Figure 22This is an illustration of how exposing a sample at two different pitches can yield a sample with very narrow lines with a wide pitch The Fabrication of Nanowires A silicon wafer was first coated with a thin layer of SiO2 by CPVD (~100nm), then coated by a layer of ARC and Photoresist. The sample was double exposed where the first exposure had a pitch of 300nm, and the second exposure had a pitch of 3µm. The process flow is shown below in Figure 23. The growing of the nanowires is done by molecular beam epitaxy and the GaAs nanowires only grows on the silicon and the SiO2 mask will block the GaAs growth, as seen in figure 24. The gate, source, and drain, are fabricated using traditional photolithography and processing steps, which will not be discussed in this paper. Due to time constraints, the fabrication of the nanowire beyond step 2, the double exposure, was not completed. This work will nonetheless continue beyond the summer and the process that will be taken is listed below. Figure 23 This is the really narrow lines that this double exposure technique creates. A major problem with this is when these line get too narrow, they begin to topple over, as illustrated in the right illustration Figure 24 This is the processing steps of the fabrication of the GaAs nanowires. The thicknesses of the layers are skewed in the representation. The actual thickness of the ARC is 160nm and the thickness of the photoresist is around 400nm. Figure 25 The figure to the left shows the stages of the growth process of the GaAs nanowires and the figure to the right shows a TEM picture of a GaAs picture with the miller indices by the planes of the nanowire. Future Work: Interferometric Lithography is a powerful tool that can be used in numerous applications. In this paper, three different applications and their fabrication processes were described. In the case of the solar cell project, once the processing steps of the Spain collaborator have been optimized, than the triple junction solar cell will be fabricated and efficiency measurements will be taken and the results will be published. For the LED project, the next step is for Rensselaer Polytechnic Institute to grow cubic-GaN and layer quantum wells on top and gather photoluminescence data. This data will determine the next step of the project. In the case of fabricating nanowire FEDs, the nanowires need to be fabricated and the wires will be studied. In all of the projects, there is a lot left to do before products based off these technologies will be commercially available. IL is a great tool that is capable of fabricating many structures and the process outlined in this paper, in particularly double exposure to get really narrow lines far apart and the use of an optical prism to increase the size of the interference region are key techniques in expanding the applications associated with IL. These two processes have been written about in previous literature, but as far as I am aware not described as they have been in this paper. Appendix: Conditions for the Exposure in Solar Cell project: The samples were spin coated with icon16, Anti-Reflection coating, at 2500rpm for 60 seconds then hard contact baked for 90 seconds at 205°C. SPR505, photoresist was then spin coated at 4000rpm for 40 seconds and baked for 90 seconds at 95°C. The IL exposure was done from a 40-100 Infinity Nd: YAG laser coming off of the 3rd harmonic corresponding to 355nm UV light. Interference was created using the Lloyd’s mirror set-up. The exposure was done at 75mj pulsed at 100htz for 38 seconds at an angle-of-incidence of 4°. The sample was then developed for 60 seconds in a 3:1 (MF 319: water) diluted developing solution. Conditions for the exposure in the LED project: The samples were spin coated with icon16, Anti-Reflection coating, at 2500rpm for 60 seconds then hard contact baked for 90 seconds at 205°C. SPR505, photoresist was then spin coated at 4000rpm for 40 seconds and baked for 90 seconds at 95°C. The IL exposure was done with the same laser using the Lloyds mirror technique for interference. The exposure was done at 75mj pulsed at 100htz for 25 seconds at a 2.5° angle-ofincidence. The sample was then developed for 60 seconds in a 3:1 (MF 319: water) diluted developing solution. Conditions for the exposure in the LED project: The samples were spin coated with icon16, Anti-Reflection coating, at 2500rpm for 60 seconds then hard contact baked for 90 seconds at 205°C. SPR505, photoresist was then spin coated at 4500rpm for 40 seconds and baked for 120 seconds at 95°C. The IL exposure was done with the same laser using the Lloyds mirror technique for interference. The first exposure was done at 75mj pulsed at 100htz for 45 seconds at a 3.5° angleof-incidence. A second exposure was then completed at 75mj pulsed at 100htz at a 36.6° angle-of-incidence. The sample was then developed for 60 seconds in a 3:1 (MF 319: water) diluted developing solution. Additional parameters adjusted for the Nanowire project: In trying to fabricate 100nm critical dimension with a 3µm pitch the parameters that were tested were: power of laser from 75mj-100mj at a 5mj increase, the time of developing from 60 seconds to 120 seconds at a 15 second interval between, and the strength of the developing solution. The time of exposure was also adjusted from 35-50 seconds at a 5 second interval the narrowest lines from a single exposure came from 95mJ exposing for 45 seconds with a 3:1 diluted developing solution. References [1] D. Xia, Z Ku, S. C. Lee, and S. R. J. Brueck, Adv. Mater. 2011, 23, 147-179. [2] G. Knier, (http://science.nasa.gov/science-news/science-at-nasa/2002/solarcells/; accessed 12/2009). [3] K. Kuhn, 2cd international CMOS Variability Conference – London 2009. [4] M. A. Martin, K. Emery, Y. Hishikawa, W. Warta, and E. D. Dunlop Prog. Photovolt: Res. Appl. 2012; 20: 12-20. [5] Phy.si Constructive and Destructive Interference (http://www.phy.si/2012/02/constructive-anddestructive.html; accessed 7/2012). [6] R.B. Darling, EE-527 (http://mmrc.caltech.edu/PVD/manuals/PhysicalVaporDeposition.pdf; accessed 7/2012). [7] S. C. Lee, A. Stintz, and S. R. J. Brueck, J. Appl. Phys, Vol. 91, No. 5, 1 March 2002. [8] S. C. Lee, K. Malloy, and S. R. J. Brueck, J. Appl. Phys., Vol. 90, No. 8, 15 October 2001. [9] S. R. J. Brueck, Proc. IEEE 2005, 93, 1704. [11] The Solar Energy Group at the University of Sydney (http://www.physics.usyd.edu.au/app/solar/research/pv.html; accessed 7/2012). [12] X. Chen, S Zaidi, and S. R. J. Brueck, J. Vac. Sci. Technol. B 14(5), Sep/Oct 1996. [13] Understanding Brewer Science ARC Products, Brewer Science slide show. [14] I. Garcia, I. Ray-Stolle, B. Galiana, and C. Algora, J. Appl. Phys., Vol. 94, 053509, 2009. [15] C. Algora, I. Ray-Stolle, I. Garcia, B. Galiana, M. Baudrit, P. Espinet, E. Barrigón, and J. González, IEEE, 001571, 2009. [16] K. Seeger, Semiconductor Physics An Introduction – 7ed., Berlin, 1999. [17] Department of Energy, Lifetime of White LEDs (http://apps1.eere.energy.gov/buildings/publications/pdfs/ssl/lifetime_white_leds_aug16_r1.pdf; accessed 7/29/2012). [18] Department of Energy, Energy Savings Potential of Solid-State Lighting in General Illumination Applications (http://apps1.eere.energy.gov/buildings/publications/pdfs/ssl/backgrounder_energy-savings-forecast.pdf; accessed 7/29/2012). [19] Department of Energy, Solid State Lighting (http://www1.eere.energy.gov/buildings/ssl/sslbasics_ledbasics.html; accessed 7/29/2012). [20]T. Gessmanm, and E. F. Schubert, J. Appl. Phys., Vol 95, 05, 1 March 2004. (http://www.ecse.rpi.edu/~schubert/Reprints/2004%20Gessmann%20and%20Schubert%20(JAP)%20Highefficiency%20AlGaInP%20LEDs%20for%20SSL%20applications.pdf; accessed 7/29/2012). [21] F.A. Ponce, D. P. Bour, Nature, Vol 386, 27, March 1997. [22]T. Harris and W. Fenlon, How Stuff Works (http://eleronic.howstuffworks.com/led1.htm; accessed 7/29/2012). [23] S.C. Lee, X.Y. Sun, S.D. Hersee, S.R.J. Brueck, Journal of Crystal Growth 272 (2004) 2–8. [24] S.C. Lee, X.Y. Sun, S.D. Hersee, S.R.J. Brueck, Journal of Crystal Growth 279 (2005) 289–292. [25] S. C. Lee, C. J. M. Stark, T. Detchprohm,** Y. B. Jiang,*** C. Wetzel, and S. R. J. Brueck, CUBIC InxGa1xN/GaN MULTI-QUANTUM WELLS GROWN ON A (111)-FACETED V-GROOVE FABRIBATED INTO A Si(001) SUBSTRATE, pending publication. [26] S. C. Lee, B. Pattada, Stephen D. Hersee, Ying-Bing Jiang, and S. R. J. Brueck,IEEE JOURNAL OF QUANTUM ELECTRONICS, VOL. 41, NO. 4, APRIL 2005. [27] S.R.J. Brueck, Nanoscale Semiconductor Electronics Proposal in Response to BAA-VS-06-05 (Call 0018). [28]S. C. Lee, A. Chaudhuri, N. Youngblood and S. R. J. Brueck, in cooperation with A. Sharma, D. Telesca, and C. Mayberry, III-V Nanowire Devices for Radiation Effect Studies, gomacmanuscript. [29] University of Cambridge, Direct and Indirect Band Gap Semiconductors , (http://www.doitpoms.ac.uk/tlplib/semiconductors/direct.php; accessed 7/31/2012). [30] U.S. Energy Information Administration, How much electricity is used for lighting in the United States? ,(http://www.eia.gov/tools/faqs/faq.cfm?id=99&t=3; accessed 7/31/2012). [31] University of Cambridge, Miller Indices, (http://www.chem.qmul.ac.uk/surfaces/scc/scat1_1b.htm; accessed 7/31/2012).