VLSI Testing Term Project

advertisement

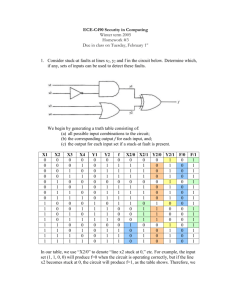

VLSI Testing Term Project Final Report Topic: Combinational Circuit Diagnosis Tool Members: R94943075 許欽雄 P94921005 王有成 R94921045 陳信成 Jan 8 2006 1. Project Description & Expected Goal to Achieve: a. In this project, we are going to develop a tool that can diagnose the failure circuit. The input data are netlist, failure trace and test pattern, the program will be able to tell which fault causes the circuit failure. Our goal is to find which fault causes the circuit failure. b. Fault signature can be obtained from fault simulation and these signatures can form a dictionary. By searching for matchings between failure trace and dictionary, we can have the list of possible faults. c. During our project development, we will make reference to the academic fault simulation tool from Virginia Polytechnic Institute University. This is a very good chance for us to learn the experience of how to implement a well-developed software tool. 2. Algorithm Flow (Shown in Fig 1.): Netlist Graph Construction Test Pattern Fault Reduction Failure Trace Fault Simulation Fault Signature and Failure Trace Matching Partial Fault Dictionary Resulting Diagnosed Faults Fig 1. Stage Test Pattern Failure Trace Net list Fault Reduction Function name Parse_Patterns Parse_FT Parser Backtracing Parity GoodMachine LogicSimulation Fault Simulation FaultSimulation FaultLogicComputation Partial Fault Dictionary Match Matching Match Function Description: (1)Parse_Patterns: Parse input test pattern file into binary format. (2)Parse_FT: Parse failure trace file into binary format. (3)Parser: Parse the net list file to construct the data structure; include nodes,edges, and relation between gate input and gate output. (4)Backtracing & Parity & GoodMachine: detail description later. (5)LogicSimulation: Build the order of evaluation and compute the node value. (6)FaultSimulation: Generate the fault signature. (7)FaultLogicComputation: Evaluate the node value recursively. (8)Match: Incremental compare the bit of partial dictionary with the bit of failure trace. 3. Graph Construction: (1) Transform the original circuit hyper-graph (Shown in Fig 2.) to a simple graph. (Shown in Fig 3.) Gate edge Net vertex (2) Fault lists are stored in vertices. A multi-terminal net will store all the faults of its branches. Each vertex will also contain the driving gate function for later evaluation. Fig 2. Fig 3. 4. Fault Reduction: (1) Backtracing: Backtrack from failing primary outputs and check if the faults exist in the intersection of failing PO supporting cones. (Shown in Fig 4.) For each test pattern, we start the back tracing from each failing PO. Recursively trace each in-edge. Mark the intersected vertices for the fault list generation. (Shown in Fig 5.) suspect fault position . Fig 5. Fig 4. (2) Parity: For a suspect fault, it should be able to generate a faulty behavior that consist with failure trace and use the policy “v ⊕ p = f” to reduce the faults, where v is stuck at value, f is observed error value and p is number of inversions. (Shown in Fig 6.) Fig 6. This strategy is integrated into the data structure construction stage. Two possible cases which should not be reduced. <1> Re-converging fan-out (Shown in Fig 7.) even # of inverters … PO odd # of inverters Fig 7. The fault of a branch stem with re-converging fan out may not be able to perform the parity reduction. <2> XOR gate (Shown in Fig 8.) (3) Good Machine Simulation: The observable fault would be able to generate a faulty value which is different from good circuit. The good simulation starts from the primary input and propagate toward the primary output. The simulation only performs on nodes with reduced faults. The simulation will stop if no faults appear in the following nodes. (Shown in Fig 9.) For a suspect fault, the stuck-at value should differ from good value in failing pattern. For each test pattern, evaluate the node according to the PO DFS order. (Shown in Fig 10.) Fig 9. (4) Fault Simulation: Partial Fault Directory Matching Create the partial fault dictionary by reduced fault simulation. (1)Inject a suspect fault (2)For each test pattern, evaluate the node according to the erroneous PO and then compute the faulty node value for the suspect fault. (3)Remove the suspect fault if the result does not match with the failure trace. (4)Continue until all suspect faults are simulated or only one faults left in the list. 5. Experimental Result: (CPU = 3.2GHz, RAM = 3GB) Circuit # gates # c17 6 Test Length 7 injected fault c432 160 83 c1908 880 83 G16 SA1 NAND2_54/ln1 SA1 G33 SA0 c6288 2416 46 NOR2_46/ln1 SA0 # Diagnosed faults 5 Circuit # c17 Correct diagnosis? Yes CPU time 0.00 s 2.49 MB 1 c432 Yes 0.01 s 2.49 MB 1 c1908 Yes 0.02 s 2.79 MB 2 c6288 Yes 0.06 s 2.97 MB memory 6. Speed up: (1) In fault simulation stage, we use recursive method to get the expect faulty value; in good machine simulation, we build the order tree to evaluate it. In order to reduce the faults of the cone, we should build the order tree to reduce all possible faults which is not the suspect faults. If we use the same method in these two stages, the runtime will increase two times. (2) We combine the match stage with partial dictionary stage, and then incrementally compare the bit of partial dictionary with the bit of failure trace. If one bit mismatch, we will ignore it and compare next fault. This saves about ten times runtime. 7. Extra bonus: Although the suggestion of problem description is “You can modify an existing academic SSF fault simulators developed by Professor Ha in Virginia Polytechnic Institute University.”, we write all of the source code of each component instead of modifying existing source code. 8. Contribution of every member: (1)Initial proposal : (2)Project progress report: (3)Writing program: (4)Program debugging: (5)Project presentation: (6)Final report: (7)Extra bonus and speed up: 許欽雄, 陳信成, 王有成 許欽雄, 陳信成, 王有成 許欽雄 許欽雄, 陳信成, 王有成 陳信成 王有成 許欽雄 Appendix: Diagnosis tool manual: Command Make make mode_run make mode make c17 make c432 make c1908 make c6288 Files: Final_submission.tgz: ISCAS85_verilog/ (Benchmark) source_code/ Makefile data_structure.cpp diagnosis.cpp parser.cpp util.cpp test.v test.pat test.failuretrace diagnosis* README Description Compile the source code. Execute the program and then enter some filenames with the suggestion. Recompile and execute the program. Execute the program with c17 circuit. Execute the program with c432 circuit. Execute the program with c1908 circuit. Execute the program with c6288 circuit.