RC CIRCUITS

advertisement

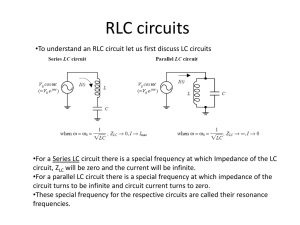

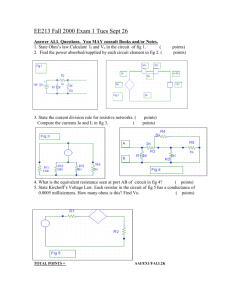

DEVRE TEORİSİ II DENEY 9 SABİT FREKANSLI RLC DEVRELERİ 9.1 AMAÇLAR 9.2.2 Sabit frekanslı RLC devrelerinin incelenmesi. a) Serie RLC devresi b) Paralel RLC devresi 9.2 TEMEL BİLGİLER 9.2.1 Serie RLC Devresi Şekil 9.1a’daki RLC devresini ele alalım. a) b) Reaktans ( ) Resistance ( ) ZC j 1 C Z L jL Z R c) d) Voltaj (V) Direnç ( ) Resistance ( ) Reaktif Güç (VA) Resistance ( ) VC j 1 I C Resistance ( U)C VL jL I V j 1 2 I C U L jL I 2 V VR R I Voltaj (V) Resistance ( ) UR R I 2 Fig. 9.1 Sinüzoidal voltaj kaynağı ile sürülen seri RLC Devresi: a) Devre diyagramı, b) Empedans üçgeni, c) Voltaj üçgeni , ve d) Güç üçgeni. Devredeki her pasif elemanın empedansı aşağıdaki gibi ifade edilir, Z R R R0 (9.1a) Z L jL L90 (9.1b) ZC j 1 1 90 . C C (9.1b) 1 Reel Güç (w) Resistance ( ) DEVRE TEORİSİ II DENEY 9 Bu sonuçlarla kullanılarak voltaj kaynağından görülen toplam empedans aşağıdaki gibi ifade edilir. 1 1 Z Z R Z L Z C R j L j R j L C C 1 1 1 R L tan L / R C C 2 2 (9.2) Z R R referans seçilerek; 9.1 ve 9.2 eşitliği kullanılarak empedans üçgeni Şekil 9.1b’de gibi çizilir. Tüm elemanlardan geçen ortak akım 9.3a eşitliğinde verilmiştir I V Z V , 1 R j (L ) C genliği ise 9.3b eşitliğinde hesaplanmıştır. V . I 1 2 2 R (L ) C (9.3a) (9.3b) I I akım fazörü referans alınarak devredeki gerilimler 9.4a, 9.4b, 9.4c ve 9.4c eşitliklerindeki ifade edilebilir. VR R I R I0 , (9.4a) VL jL I L I90 , (9.4b) VC j 1 1 I I 90 , C C (9.4c) 1 V VR VL VC R j L I, C 2 1 2 R L C I tan 1 L 1 / R . C (9.4d) Obviously VL leads VR by 90 and VC lags VR by 90 , and V leads VR by 1 tan 1 L / R . Since each voltage is obtained by multiplying the associated C impedance by I , the plot of the voltage phasors (voltage triangle) is similar to the impedance traingle and it is shown in Fig. 9.1c. 2 DEVRE TEORİSİ II DENEY 9 The complex power flowing to each component and the total complex power supplied by the source are given as U R VR I * VR I R I ( I ) R I 2 , (9.5a) U L VL I * VL I jL I ( I ) jLI 2 , (9.5b) U C VC I * VC I j 1 1 2 I (I ) j I , C C U U R U L U C R (9.5c) 1 2 j L I . C 9.5d) Hence P Re (U ) RI 2 , (9.6a) 1 2 Q Im (U ) L I , C (9.6b) =Power angle = tan 1 L R p.f. =Power factor = Cos 1 C , (9.6c) R 1 R 2 L C 2 . (9.6d) 1 L , otherwise it is lagging. The power triangle C is similar to the the ones obtained for the impedance and voltages, and it is shown in Fig. 9.1d. The power is leading if Q 0 , i.e., 9.2.2 Parallel RLC Circuit The Parallel RLC circuit is shown in Fig. 9.2. Similar results given for the series RLC circuit can be derived for this circuit as well. This is left to student as part of the preliminary work. 9.3 PRELIMINARY WORK 1) Consider the parallel RLC circuit shown in Fig. 9.2a. Let the source be a sinusoidal current driver with an angular frequency . As in the steps parallel to the ones given for the series RLC circuit, answer the followings: 3 DEVRE TEORİSİ II DENEY 9 a) b) c) d) Fig. 9.2 Parallel RLC circuit: a) Circuit diagram, b) Admittance triangle, c) Current triangle, and d) Power triangle. a) Find the admittance of each passive component. Draw the admittance triangle in Fig. 9.2b showing YR , YL , YC , and the total admittance Y seen by the source. b) Express the voltage phasor V in terms of R, L, C, , and I. c) Assuming V as reference, express the component currents. I R , I L , I C , and I in terms of component values, , and V. Find the phase angle of each current phasor and plot the current triangle as Fig. 9.2c. d) Find the expression for the complex power for each component and the total complex power supplied by the source in terms of component values, , and V. What are the total real and reactive powers, the power angle, and the power factor? Draw the power triangle. (Your plots must be self explanatory, i.e., indicate the proper expression for each vector on the plots.) Answer: 4 DEVRE TEORİSİ II DENEY 9 2) The series RLC circuit used in the experiment is shown in Fig. 9.3 where V has 2 kHz frequency and 2 V pp. a) b) c) Compute the impedance Z R , Z L , Z C , Z and fill them in Table 9.3. Compute the parameters associated with the voltages shown in Table 9.2, and complete the theoretical columns of this table. Compute the powers indicated in Table 9.4 and fill in the theoretical columns of this table. Answer: 3) The parallel RLC circuit used in the experiment is shown in Fig. 9.4 where V has 2 kHz frequency and 2 V pp. Ignore the effect of 1 resistor used to measure the current I. a) b) c) Compute the admittances YR , YL , YC , Y and fill them in Table 9.6. Compute the parameters associated with the currents shown in Table 9.5, and compute the theoretical columns of this table. Compute the powers indicated in Table 9.7 and fill in the theoretical columns of this table. Answer: 5 DEVRE TEORİSİ II DENEY 9 9.4 EQUIPMENT AND MATERIALS The list of equipment and materials used in this experiment is shown in Table 200.1. Fill in the last three column of this table after investigating the equipment supplied on your experiment table. Record any damage, if exists any while performing the experiment, and its way of occurrence in the allocated space of this table in detail. You can also write the difficulties you are confronted with when using the equipment, and your suggestions and critics related with the equipment you used. Table 200.1 Equipment and materials list. No: Equipment 1 Cathode Ray Ociloscope 2 Function Generator 3 1 Plug in Board 4 Bridging Plugs 5 Connecting Probes and Cables 6 1 F Capacitor 7 220 and 1 Resistors 8 18 mH Inductor (1000 turns) Record of damage or other comments: Model Serial No: Office Stock No: 9.5 EXPERIMENTAL WORK 9.5.1 Series RLC Circuit 1) Set up the series RLC circuit shown in Fig. 9.3. Set the signal generator to sinusoidal wave with 2 kHz frequency. Fig. 9.3 Series RLC circuit for Exercise 9.5.1 Adjust the level V as to 2 V pp and measure VR by using CRO. Note the phase of V taking that of VR as reference. Record V (pp), VR (pp), and phase of V in Table 9.2. Plot the wave shapes of and VR in Fig. 9.6. 6 DEVRE TEORİSİ II DENEY 9 2) Without changing the frequency and the output level of the signal generator, arrange the order of the circuit elements, more explicitly interchange the places of R and L. Then measure the pp value and phase of VL by CRO. Record these values in Table 9.2. Plot the time variation of VL in Fig. 9.x. 3) Repeat Step 2 for the capacitor. Measure VC by CRO, record its pp value and phase in Table 9.2, and its time wave in Fig. 9.6. 9.5.2 Parallel RLC Circuit 1) Set up the parallel RLC circuit shown in Fig. 9.4. Set the signal generator to sinusoidal wave with 2 kHz frequency. Adjust the level V to 2 V pp. Measure I and its phase with respect to V. Record the results in Table 9.5. Plot the variation of i (t ) and iR (t ) on Fig. 9.7. (Not: 1 is used to measure the current; it can be ignored for calculations. Therefore iR (t ) v(t ) / 220 .) Fig. 9.4 Parallel RLC circuit modified for measuring the total current I. 2) Remove 1 resistor used to measure I. Replace it in series with the inductance as shown in Fig. 9.5. Measure I L and its phase with respect to V. Record the results in Table 9.5. Plot the variation of iL (t ) on Fig. 9.7. 7 DEVRE TEORİSİ II DENEY 9 Fig. 9.5 Parallel RLC circuit modified for measuring the current I L . 3) Remove 1 resistor and connect it in series with the capacitor to measure iC (t ) . Measure iC and its phase, record the results in Table 9.5. Plot the variation of iC (t ) on Fig. 9.7. 9.6 RESULTS AND DISCUSSION 1. The results of Exercise 9.5.1 for the series RLC circuit are shown in Table 9.2 and Fig. 9.3. Complete Table 9.2 from the experimental phase relations in this table, compute the time-lead or time-lag (delay) of each waveform in Fig. 9.6 and show them on the figure explicitly. Using the experimental data record in this table is taken while performing the experiment, complete the experimental columns of Tables 9.3 and 9.4. Table 9.2 Theoretical and experimental data for the series RLC circuit in Fig. 9.3 Theoretical Voltage (V) pp (V) rms (V) Experimental phase () V VR VL VC 8 pp (V) rms (V) phase () DEVRE TEORİSİ II DENEY 9 Fig. 9.6 Time variation of the component voltages v (t ) , vR (t ) , v L (t ) , vC (t ) in the series RLC circuit of Fig. 9.3. Table 9.3 Theoretically and experimentally computed values of impedances for the series RLC circuit of Fig. 9.3. Theoretical Impedance ( ) Rectangular form Experimental Polar form Rectangular form Polar form ZR ZL ZC Z Table 9.4 Theoretically and experimentally computed values of powers for the series RLC circuit of Fig. 9.3. Theoretical Power (W) Rectangular form Experimental Polar form PR PL PC P Power factor pf cos 9 Rectangular form Polar form DEVRE TEORİSİ II DENEY 9 2. Draw the impedance, voltage and power triangles on scale for the series RLC circuit in Fig. 9.8 by using the theoretical (bold lines) and experimental (dashed lines) data present in Tables 9.3, 9.2, 9.4, respectively a) b) c) Fig. 9.8 a) Impedance, b) Voltage, and c) Power triangles for the series RLC circuit in in Fig. 9.4. 3. The results of Exercise 9.5.2 for the Parallel RLC circuit are shown in Table 9.5 and Fig. 9.7. Complete Table 9.5 from the experimental phase relations in this table, compute the time-lead or time-lag (delay) of each waveform in Fig. 9.7 and show them on the figure explicitly. Using the experimental data record in this table is taken while performing the experiment, complete the experimental columns of Tables 9.6 and 9.7. Table 9.5 Theoretical and experimental data for the parallel RLC circuit in Fig. 9.4. Current (mA) Theoretical pp (mA) rms (mA) Experimental phase () pp (mA) rms (mA) phase () I IR IL IC Fig. 9.7 Time variation of the component voltages i (t ) , i R (t ) , iL (t ) , iC (t ) in the parallel RLC circuit of Fig. 9.4. 10 DEVRE TEORİSİ II DENEY 9 Table 9.6 Theoretically and experimentally computed values of admittances in the parallel RLC circuit of Fig. 9.4. Theoretical Admittance Rectangular Polar ( ) form form Experimental Rectangular form Polar form YR YL YC Y Table 9.7 Theoretically and experimentally computed values of powers for the parallel RLC circuit of Fig. 9.4. Theoretical Experimental Power Rectangular Rectangular ( mVA ) Polar form Polar form form form UR UL UC U Power factor cos 4. Draw the admittance, current and power triangles on scale for the parallel RLC circuit in Fig. 9.4 by using the theoretical (bold lines) and experimental (dashed lines) data. a) b) c) Fig. 9.9 a) Admittance, b) Current, and c) Power triangles for the parallel RLC circuit in in Fig. 9.4. 5. Are the theoretical and experimental vector triangles drawn in Fig. 9.8 and 9.9 consistent. If not, what are the possible reasons? 11 DEVRE TEORİSİ II DENEY 9 6. Why 1 resistor is used in the experiment? Why its effect is negligible? Discuss the possibilities of using a higher resistance, 100 for example, and a lower resistance, 0.01 for example. 7. Explain the reason for the change of the power factor from lagging to leading or from leading to lagging as the structure of the circuit is changed from series to parallel or vice versa although the same component values and input voltages are used. 12