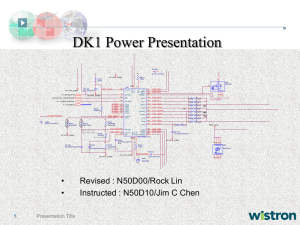

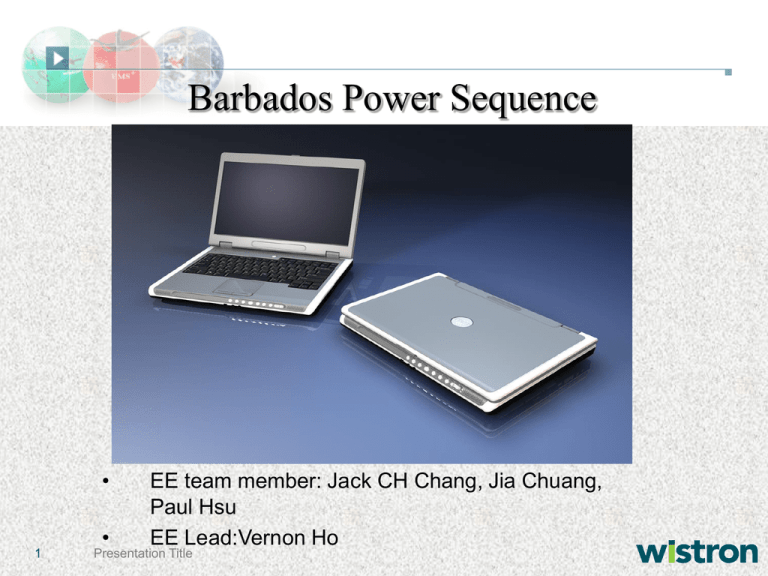

Barbados_Power sequence

advertisement

Barbados Power Sequence • 1 • EE team member: Jack CH Chang, Jia Chuang, Paul Hsu EE Lead:Vernon Ho Presentation Title Barbados Block Diagram Intel Mobile CPU Cl ock Generator ICS954226/CV140PAG 3 Barbados Block Diagram Dothan: 1.6BGHz/1.73GHz 1.87GHz/2AGHz/2.1GHz Celeron:1.4GHz/1.5GHz/1.6GHz 4,5 Project code:91.4C401.001 PCB P/N :04242 REVISION :SD System DC/DC 400/533MHz 4.3GB/s HOST BUS 200-PIN DDR2 SODIMM UNBUFFERED DDR2 SODIM M Socket 11 DDRII 400/533MHz MAX8734A Alviso GM(915) LVDS AGTL+ CPU I/F RGB CRT CRT Port 43 S-VIDEO 15 14.1" W XGA 14 INTEGRATED GRAHPICS TV OUT AT93C46 25 LVDS, CRT I/F BCM 4401KQLG 6,7,8,9 DMI I/F 33 SMBus ODD Bay 20 Silicon Image SII3811 (MARVELL 8040) 21 IDE 21 LINE OUT MIC IN 100MHz Primary IDE Ri cho 832 Intel ICH6-M SATA ETHERNET(10/100Mb) OP AMP MAX4411ETP RJ45 CONN 43 42 MAX1909 PW R_ SRC BATT+ 43 MDC Modem 1.5 40 PW R_ SRC +1 .0 5VRUN +1 .5 VSUS CPU DC/DC ISL6217 38 PW R_ SRC VCC_CORE DDR2 DC/DC PW R_ SRC PCI Bus / 33MHz Mini-PCI 802.11a/ b/ g LPC I/F Azalia CODEC STAC 9200 26 MAX8743 41 TI 51116 SATA +1 .8 VSUS +0 .9 VRUN +0 .9 VSUS_ D D R2 VREF 28 PCI/PCI BRIDGE Power Switch 20 16,17,18,19 PCI Express/USB2.0 26 ExpressCard SLOT 20 PCB LAYER USB 2.0 RJ11 CONN 7in1 CONN 22 ATA 66/100 AZALIA 27 7in1 1394 CONN 23 22,23 AC97 2.2/AZALIA ACPI 1.1 OP AMP TAPA6017 INT.SPKR 1394 1394 7in1 USB 2.0 (2+2+2+2) 27 32 KBC SMSC LPC47354 MAC III 29,30 USB*4 32 Bl uetooth 32 2 +5 VSUS System DC/DC Thermal Sensor HDD PW R_ SRC Battery Charger ATMEL 24 EMC6N300 OUTPUTS +3 VSRC DDR Memory I/F UNBUFFERED DDR2 SODIM M Socket 12 39 INPUTS Presentation Title Int. KB Touch Pad 34 BIOS MX29LV008BBTC-90G 31 L1:TOP L2:Signal L3:GND L4:Signal L5:Signal L6:VCC L7:GND L8:BOT Power on sequence block diagram 3 Please link to >>>>>> Presentation Title How can we know Macallen3 is working? 1) Use probe to touch the DBG2 pin 2 ( DEBUG_OUT ) without inserting AC adapter. 2) As for oscilloscope, set up Trigger Mode : Normal. 3) Final step that have to insert AC adapter but do not press Power Button. 4) Eventually, we should have 4 set of pulses as below. 4 Presentation Title Good Signal From Macallen 5 Presentation Title Procedure Of Checking Macallen Pulses a) If we couldn’t have such pulses from Macallen3. b) Please go back to check the signal step by step. +3.3VRTC +3VALW DEBUG_OUT X3( PIN 1, 2, XTAL ). c) There are several circuit portion listed below. 6 Presentation Title Macallen3 need VCCRTC Power 1 C59 3 SC1U25V -U C60 0 SCD1U25V3K X 2 R51 4 10K R2 2 1 PWR_SRC +3_3V RT C U53 SHDN# OUT GND IN MA X1615 EUK -GP 3 2 1 2 5 5/3# C59 6 SC1U10V 3KX 1 4 CH751H-40P T VCCRTC D30 1 2 RT C1 1 R52 0 1KR2 2 VCCRTC_D D29 1 CH751H-40P T 2 2 VCCRTC_CON 1 2 MH1 MH2 1 PWR GND MH1 MH2 BA T-CON2-U-GP 22.70031.001 Page 29 7 Presentation Title C58 6 SC1U10V 3KX Macallen3 receive ACAV_IN 8 Presentation Title Macallen3 output ALWON 9 Presentation Title Macallen3 Reset and Start Working See Page 30 Reset Macallen 10 Presentation Title Macallen3 Output Pulses 11 Presentation Title Procedure Of Checking No Power Issues • First Case: No +3VALW and +5VALW power a) Firstly, check if Charger U5 pin6 ACAV_IN drive high? b) Check U13 pin 20 V+ get 19.5V? +3VALW and +5VALW power use LDO to generate. b) Check if ALWON is high?(3.3V signal) See page 42 and 39. 12 Presentation Title Procedure Of Checking No Power Issues • Symptom : 3 LED light turn on entirely First Case: a) Firstly, you can jump to check VCC_CORE power plane. b) Does CPU power comes up? c) If doesn’t . Please go back to check with the power sequence from beginning as +5VSUS/+3VSUS +1.8VSUS_PG SUSPWROK RUN_ON +1.05VRUN_PWRGD RUNPWROK . d) These action will check which power plane have no power up. 13 Presentation Title Procedure Of Checking No Power Issues Second Case: a) Assumed that CPU voltage can attain 0.9 Volt above. b) We may prove that the rest of power plane before VCC_CORE power plane would be fine. c) Afterward, please check with PLT_RST1# GTL_CPURST# . d) If PLT_RST1# still can’t exist, we can check the following signal RESET_OUT( From Macallen3) IMVP_PWROK. ICH_PWROK e) If GTL_CPURST# can’t driven high, go back to check the PLT_RST1#. f) In addition, we can check whether reference voltage( 2/3 Vcc_IO ) for GMCH correct or not, that is, H_VREF ( R108 pin 2) 14 Presentation Title Procedure Of Checking No Power Issues 1) If both PLT_RST1# and GTL_CPURST# driven high. We’ll keep tracking the next signal which connect between CPU and GMCH, that is, GTL_ADS#. ( Fig.1 ). 2) We can assume that CPU may failure if we can’t get these pulses in Fig.1. 3) Another case is only show up one pulse in Fig.1 that we can suspect the failure in U32 ( Bios Rom ) or CPU NG. 15 Presentation Title Fig.1 ( GTL_ADS# ) GTL_ADS# is the “first signal” generated by CPU , 18 16 GTL_ADS# Presentation Title CPU to NB Test pad only . LPC_LFRAME# WAVEFORM COME OUT AFTER GTL_ADS# PRODUCED BY CPU 17 Presentation Title CPU access BIOS data flow VCC Clock VCC Clock GTL_ADS# CPU DMI N/B GTL_TRDY# GTL_CPURST# GTL_D#(63:0) 18 VCC Clock Presentation Title VCC Clock LPC_LFRAME # S/B DMI A(19:0) KBC LAD(3:0) Reset VCC BIOS KBC_D(7:0) Reset Barbados Power Sequence Waveform Please reference to Proto-1.0 board power sequence. 19 Presentation Title Keyboard LEDs Error code Please see attached file=> Power Event log: 20 Presentation Title