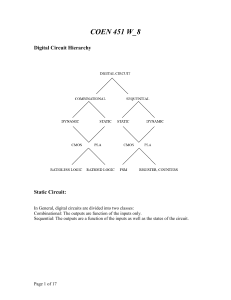

Static CMOS Gates

advertisement

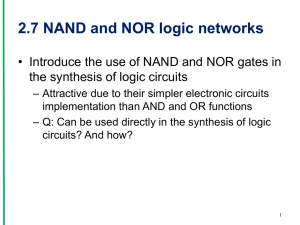

Lecture 5 Static CMOS Gates Jack Ou, Ph.D. 2-Input NOR Gate F can only be pulled up if A=B=0 V F can be pulled down by either A=1 or B=1. (Or Both) 2-Input NAND Gate F can only be pulled down if both A=B=1. F will be pulled up if either A or B is 0 V. NAND Gates NOR Gates 2-Input AND Gate NAND 2-Input OR Gate NOR Alternative Implementation for High Fanin Gates Steps for Generating Non-Trivial Static CMOS Logic Circuits 1. Implement the pull-down (NMOS)circuit using 𝐹 – Useful technique: DeMorgan’s Theorem 2. Synthesize the dual of the pull-down circuits using PMOS DeMorgan’s Theorem • The complement of a function can be obtained by – Replacing each variable with its complement – Exchange the AND and OR functions • Example – 𝐴 + 𝐵 𝐶 = 𝐴 + 𝐵 + 𝐶 = 𝐴𝐵+𝐶 Dual • The dual of any logic function can be obtained by exchanging the AND and OR operations. – ab ↔a+b – (a+b)c ↔ab+c A fictional AND Circuit The current flows only when both A and B are closed. Fictional OR Circuit The current flows when either A or B is closed. Implementation • Use transistors in series to implement a logical AND function • Use transistors in parallel to implement a logical OR function OAI Circuit ( 𝐴 + 𝐵 𝐶) XOR/XNOR Mux Determine a Boolean Expression a Schematic 1. Determine 𝐹 implemented by a NMOS pulldown network. 2. Complement 𝐹 to obtain F. 2-Input XOR 𝐴0𝐴1(A0+A1 XNOR 𝐴0𝐴1(A0+A1) 𝐴0 𝐴1 𝐴0 + 𝐴1 𝐴0𝐴1 CMOS Gate Sizing Device Sizing • Obtain the same delay as the inverter for the rise/fall cases. – ReffN=12.5 Kohm/SQ, ReffP=30 Kohm/SQ – Reff=Reff(L/W) – ReffP/ReffN=2.4 – To achieve the same delay, (assume LP=LN, WP=2.4WN, WP/WN is approximately 2. Size Devices for the Worst Case • Series transistors: Increase W to reduce Reff. • Parallel transistors: assume the worst case, i.e. only one of the parallel transistor is ON. Transistor Sizing Without Velocity Saturation Figure 5.2 Assumption: Equal rise delay and fall delay Consideration: Effective Resistance Inverter Inverter tPHL tPHL=64.045 pS NAND2 Test Circuit NAND2 tPHL tPHL=66.01 pS Effective Width • Transistors in Series – W1||W2||W3 • Transistors in Parallel – W+W2+W3 Trade-Off Increase W to reduce the effective Resistance for the pull down network. The area is increased. FO4 Fanout ratio: total capacitance driven by a gate dividing by its input capacitance VTC of Gates Adjust VS • Knob: – χ as defined in EQ. 4.15 – Increase WNLP/LNWP to decreased VS. – Decrease WNLP/LNWP to increased VS. Switching Voltage of a NAND Gate Both inputs tied together: effective WN=W, WP=4W, VS shifts to the right. Both input A=high, sweep VB: effective WN=2W, WP=2W, VS shifts to the left. Switching Voltage of a NOR Gate Both inputs tied together: effective WN=2W, WP=2W, VS shifts to the left. Both input A=ground, sweep VB: effective WN=W, WP=4W, VS shifts to the right.