exp6_lecture

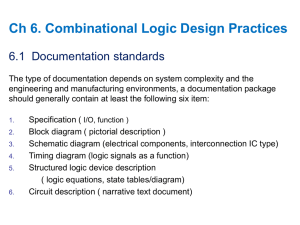

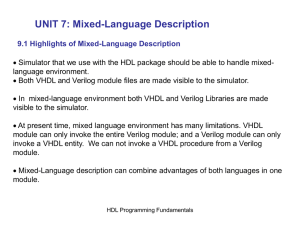

advertisement

Experiment 6 Combinational Building Blocks: Encoders and Decoders Lab 4 Comments: • The Main Points: – Simulation: • allowed you to test a circuit before you actually built the circuit • Simulator was based on device models • Device models were used to simulate propagation delays in actual devices • Static logic hazards were located, tested (they caused glitches), and removed. Lab 4 Comments: • Procedure Ordering in lab report • report should have close to logical flow of what you did in experiment: 1) procedure, 2) results/data, 3) observations… 1) procedure, 2) results/data, observations… etc. • Don’t use command style of writing in lab reports • Use engineering notation: MHz, kHz, ms, μs, ns (order of magnitudes of 3) • Use some horse sense: stand back and verify your results make sense! Lab 5 Comments: • The Main Points: – – The logic analyzer is a test device that is used to view the signal activity of an actual circuit (as opposed to the simulated circuit of Lab 4). The Xilinx Design Methodology was the steps you took to: 1. model a circuit 2. simulate the model 3. implement a circuit (on the CPLD) with the same output characteristics of the model – Implementing circuits on the CPLD was much easier than wiring the circuit using discrete logic gates (previous experiments). Lab 5 Comments: • • • • • • Title and annotate timing diagrams (and all diagrams for that matter) Don’t allow your VHDL code to wrap: examine your outputs before you submit them Put a title banner on all your VHDL files Put some comments into your VHDL code Print your VHDL code from Xilinx environment and include with your report (don’t put code into body of report) Print timing simulations from ModelSim and include with your report: don’t cut and paste Instructional Objectives: • To learn concurrent statement in VHDL. • To design combinational building blocks in VHDL and to implement them on the CoolRunner II CPLD. Instructional Objectives: • To learn concurrent statement in VHDL. • To design combinational building blocks in VHDL and to implement them on the CoolRunner II CPLD. VHDL Basics • ENTITY– black box description of circuit that declares inputs and outputs, their type, and their size • ARCHITECTURE – what’s inside the box…. Specifies the implementation of your circuit VHDL Entity ENTITY modulename IS PORT ( input1 : IN STD_LOGIC; input2 : IN STD_LOGIC; output1 : OUT STD_LOGIC_VECTOR(0 TO 7); output2 : OUT STD_LOGIC); END modulename; VHDL Architecture ARCHITECTURE myarch OF modulename IS internal signal declarations; BEGIN concurrent statement1; concurrent statement2; concurrent statement3; END myarch; Concurrent Statements: Signal Assignment (<=) ARCHITECTURE my_arch OF module_name IS SIGNAL internal_sig : STD_LOGIC; BEGIN -- a comment begins with two hyphens internal_sig <= input1 AND input2; output1 <= “10101010”; output2 <= internal_sig XOR output1(3); END my_arch; Concurrent Statements: Conditional Signal Assigment ARCHITECTURE myarch OF modulename IS BEGIN output2 <= b WHEN (sel = “01”) ELSE c WHEN (sel = “10”) ELSE d WHEN (sel = “11”) ELSE a; -- default END myarch; Concurrent Statements: Selected Signal Assignment ARCHITECTURE myarch OF modulename IS BEGIN WITH sel SELECT output2 <= b WHEN “01”, c WHEN “10”, d WHEN “11”, a WHEN OTHERS; END myarch; XCRPlus Development Board Xilinx CoolRunner CPLD 64 macrocells Xilinx Design Methodology 1) VHDL source code is used to generate a description of your circuit design. 2) The VHDL source code generated in step 1) is translated into a form which can be used by other software used in the design flow. 3) The Test Bench Waveform software is used to generate signals which are used to verify proper circuit operation in the ModelSim XE simulator. 4) The circuit inputs and outputs are internally “mapped” to CPLD pins which are externally hardwired to input and output devices on the XCRP board. 5) The circuit design is downloaded into the CPLD. 6) Proper operation of the circuit is verified. XCRPlus Development Board a f •Active high •Common cathode connected to GND via a transistor 7-Segment LED Displays g e c d cat1 b Experiment 6 Overview P1: Design and implement a Binary-Coded-Decimal (BCD) to 7-segment Display Decoder P2: Design and implement an 8:3 Priority Encoder P3: Integrate the circuit from the two previous steps and use the BCD-7seg Decoder to display your output Digital Alarm System 7-Seg Decoder Priority Encoder Connect to ground 4 switches (sensors) I7 I6 I5 I4 I3 I2 I1 I0 B3 B2 B1 B0 Y2 Y1 Y0 AA-AG CATH STROBE Alarm Control Key Comparator Break-in 4 switches (access code) I3 I2 I1 I0 EQ OFF/ON_L Armed Alarm