PERFECT Empower Project: Prototype Software

advertisement

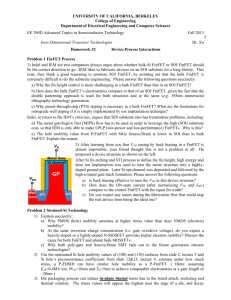

PERFECT Empower Project: Prototype Software Releases PI: Massoud Pedram Co-PIs: Murali Annavaram and Kaushik Roy (Purdue) July 17, 2014 DARPA Perfect Releases: Overview • Device Releases (nominal devices) • 5nm gate length FinFET devices (7nm effective channel length) from Prof. Kaushik Roy’s group) • 7nm gate length FinFET devices (10nm effective channel length) with two threshold voltages • 14nm bulk CMOS devices • Cell Library Releases • 5nm gate length FinFET cell libraries for near- and super-threshold operations • 7nm gate length FinFET cell libraries with two threshold voltages for near- and super-threshold operations • 14nm CMOS cell libraries for near- and super-threshold operations • 16nm CMOS (PTM) cell libraries for near- and super-threshold operations • Architecture-level Releases • PCACTI 2 Device Releases: 5nm Gate Length FinFET • 5nm gate length (7nm channel length) FinFET devices • SPICE-compatible Verilog-A models • Based on NEMO5 simulator, which uses quantum transport models (e.g., atomistic simulator) • Three different device models depending on the degree of gate underlap • The most advanced device model in the release • Available on the PERFECT Wiki site and NanoHub 3 Device Releases: 7nm Gate Length FinFET • 7nm gate length (10nm channel length) FinFET devices with two different threshold voltages • SPICE-compatible Verilog-A models • Includes low-threshold FinFET devices with a threshold voltage of 0.2V-0.25V as well as high-threshold devices with a threshold voltage of 0.3V-0.35V • Based on Synopsys TCAD suite (i.e., Sentaurus), which uses semi-classical transport models with quantum correction • Beta release available on the PERFECT Wiki site and http://atrak.usc.edu/downloads/packages/ 4 Device Releases: 14nm CMOS Devices • 14nm CMOS devices developed by Prof. Pedram’s team • SPICE-compatible Verilog-A models • Based on Synopsys TCAD suite (i.e., Sentaurus) • Beta release available on the PERFECT Wiki site and http://atrak.usc.edu/downloads/packages/ • May be compared with the PTM 16nm bulk CMOS device models of Prof. Yu Cao’s team at Arizona State University 5 Device Releases: Ongoing Work • The beta releases of 5nm gate length and 7nm gate length FinFET devices are nominal device models • No accounting for the process variation effects yet • Nominal device model parameters may have to be changed in order to do proper design centering • Must develop new models for a few critical corners 6 Cell Library Releases: 5nm Gate Length FinFET • Standard cell libraries based on 5nm gate length (7nm channel length) FinFET devices • Can be used for circuit synthesis • Beta release available on the PERFECT Wiki site and http://atrak.usc.edu/downloads/packages/ • Containing the following libraries: • 5nm gate length FinFET library operating at 0.3V supply voltage level (near-threshold operation) • 5nm gate length FinFET library operating at 0.45V supply voltage level (super-threshold operation) 7 Cell Library Releases: 7nm Gate Length FinFET • Standard cell libraries based on multi-threshold 7nm gate length (10nm channel length) FinFET devices • Beta release available on the PERFECT Wiki site and http://atrak.usc.edu/downloads/packages/ • Containing the following libraries: • FinFET_7nm_HVT_0300.lib: Standard cell library of high-threshold FinFET devices operating at 0.3V supply voltage level (nearthreshold) • FinFET_7nm_HVT_0450.lib: Standard cell library of high-threshold FinFET devices operating at 0.45V supply voltage level (superthreshold) • FinFET_7nm_LVT_0300.lib: Standard cell library of low-threshold FinFET devices operating at 0.3V supply voltage level (nearthreshold) • FinFET_7nm_LVT_0450.lib: Standard cell library of low-threshold FinFET devices operating at 0.45V supply voltage level (superthreshold) 8 Cell Library Releases: 14nm and 16nm CMOS • Standard cell libraries based on 14nm CMOS devices • Containing the following libraries: • 14nm CMOS library at 0.55V supply voltage level (near-threshold operation) • 14nm CMOS library at 0.70V supply voltage level (super-threshold operation) • 14nm CMOS library at 0.80V supply voltage level (performance-boosted operation) • Standard cell libraries based on 16nm PTM CMOS devices • Containing the following libraries: • 16nm CMOS library at 0.50V supply voltage level (near-threshold operation) • 16nm CMOS library at 0.70V supply voltage level (super-threshold operation) • Beta release available on the PERFECT Wiki site and http://atrak.usc.edu/downloads/packages/ 9 Cell Library Releases: Ongoing Work • Incorporating wire load modeling in the standard cell library • Wire load library will be released soon • Generating (l-based) physical cells for layout 10 Architecture-level Releases: PCACTI • PCACTI: A delay, power, and area modeling tool for cache and memory systems for deeply-scaled FinFET devices supporting multiple voltage regimes • Extension over the widely-used CACTI tool for bulk CMOS devices • Addresses key shortcomings of current releases of CACTI: • Support only planar CMOS devices from 90nm to 22nm technology nodes • Rely on outdated (and somewhat inaccurate) technological parameters – Extracted from 2005 ITRS predictions • Support only conventional 6T SRAM cell designs – An 6T SRAM cell optimized for 130nm process is adopted for all technology nodes – The impact of VDD scaling and device mismatches have been ignored 11 PCACTI: Novel Features • Features of PCACTI (previously named FinCACTI): • Accurate technology parameters for deeply-scaled (7nm gate length) FinFET devices • ON/OFF currents for N- and P-type fins (for temperatures ranging from 300K to 400K) • SPICE-compatible Verilog-A models to derive gate- and circuit-level parameters • E.g., PMOS to NMOS size ratio, stack effect factor, DC noise margin of FinFET-based SRAM cells • Accurate area and capacitance models for FinFET devices • Layout area, power, and access delay calculations for FinFET-based 6T and 8T SRAM cells • Architectural support for the 8T SRAM cells • Multiple voltage support for SRAM cells • Updated interconnect-related electrical parameters • Based on 2012 version of the ITRS • XML-based interfaces for specifying cache configuration, SRAM cell, technological parameters, etc. 12 PCACTI: Status and Near-Future Plans • Current version supports 7nm gate length FinFET devices (low threshold device), 14nm CMOS devices (our model), and 16nm PTM CMOS devices • Supports two operating voltage levels (near- and super-threshold) for each technology node • In the process of adding support for 22nm and 32nm CMOS devices for completeness as well as various versions of the 5nm gate length FinFET devices 13 PCACTI: Releases, Reference, Results • Releases of PCACTI under the PERFECT Wiki page and http://atrak.usc.edu/downloads/packages/ • PCACTI.zip file for download and web interface • Reference: • A. Shafaei, Y. Wang, X. Lin, and M. Pedram, “FinCACTI: Architectural analysis and modeling of caches with deeply-scaled FinFET devices,” Proc. of the IEEE Computer Society Annual Symposium on VLSI, July 2014, Best paper award. • Sample Results for a 16KB, 4-way set-associative, L1 cache • • 7nm gate length FinFET (our device design) at VDD = 0.3V and VDD = 0.45V 14nm CMOS (our device design) at VDD = 0.55V and VDD = 0.8V 14 PCACTI: Web Interface 15 Longer Term Plans for PCACTI • Planned work: • Enhancing SRAM cell stability and reduce leakage: • FinFET-based SRAM cells with multi-threshold devices • FinFET-based SRAM cells dual-gate control capability • Performing variability-aware design of SRAM cells: Joint optimization of VDD and SRAM cell configuration • Start using new models provided by PCACTI along with architectural modeling and simulation tools such as GPUWattch and McPAT for doing power/performance characterizations and optimizations at the architecture and system levels 16