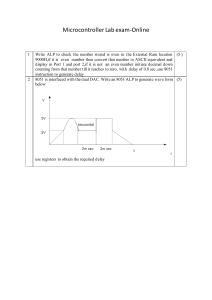

Contents: Introduction Block Diagram and Pin Description of the 8051 Registers Some Simple Instructions Structure of Assembly language and Running an 8051 program Memory mapping in 8051 8051 Flag bits and the PSW register Addressing Modes 16-bit, BCD and Signed Arithmetic in 8051 Stack in the 8051 LOOP and JUMP Instructions CALL Instructions I/O Port Programming Introduction General-purpose microprocessor CPU for Computers No RAM, ROM, I/O on CPU chip itself Example:Intel’s x86, Motorola’s 680x0 CPU GeneralPurpose Microprocessor Many chips on mother’s board Data Bus RAM ROM I/O Port Address Bus General-Purpose Microprocessor System Timer Serial COM Port Microcontroller A smaller computer On-chip RAM, ROM, I/O ports... Example:Motorola’s 6811, Intel’s 8051, Zilog’s Z8 and PIC 16X CPU RAM ROM A single chip I/O Port Serial Timer COM Port Microcontroller Microprocessor vs. Microcontroller Microprocessor CPU is stand-alone, RAM, ROM, I/O, timer are separate designer can decide on the amount of ROM, RAM and I/O ports. expansive versatility general-purpose Microcontroller • CPU, RAM, ROM, I/O and timer are all on a single chip • fix amount of on-chip ROM, RAM, I/O ports • for applications in which cost, power and space are critical • single-purpose Microprocessor vs. Microcontroller Microprocessor: general-purpose CPU Emphasis is on flexibility and performance Generic user-interface such as keyboard, mouse, etc. Used in a PC, PDA, cell phone, etc. Microcontroller: microprocessor + memory on a single chip Emphasis is on size and cost reduction The user interface is tailored to the application, such as the buttons on a TV remote control Used in a digital watch, TV remote control, car and many common day-to-day appliances Harvard and von Neumann Architectures Harvard Architecture—a type of computer architecture where the instructions (program code) and data are stored in separate memory spaces Example: Intel 8051 architecture von Neumann Architecture—another type of computer architecture where the instructions and data are stored in the same memory space Example: Intel x86 architecture (Intel Pentium, AMD Athlon, etc.) MCU Fetch-Execute Cycle Fetch operation—retrieves Program Counter (PC) an instruction from the location in code memory pointed to by the program counter (PC) Execute operation— executes the instruction that was fetched during the fetch operation. In addition to executing the instruction, the CPU also adds the appropriate number to the PC to point it to the next instruction to be fetched. Code Memory F e t c h + CPU To other peripherals Microcontroller Architectures Microcontroller architecture refers to the internal hardware organization of a microcontroller Each hardware architecture has its own set of software instructions called assembly language that allows programming of the microcontroller Some of the popular microcontroller architectures Intel 8051 Zilog Z80 Atmel AVR Some Microcontroller Producers Texas Instruments Microchip Silicon Labs Intel Corporation Analog Devices Atmel Corporation Dallas Semiconductor Fujitsu Semiconductor Europe National Semiconductor STMicroelectronics ZiLog Freescale Semiconductor Infineon Technologies Three criteria in Choosing a Microcontroller meeting the computing needs of the task efficiently and cost effectively • speed, the amount of ROM and RAM, the number of I/O ports and timers, size, packaging, power consumption • easy to upgrade • cost per unit 2. availability of software development tools • assemblers, debuggers, C compilers, emulator, simulator, technical support 3. wide availability and reliable sources of the microcontrollers. 1. Block Diagram External interrupts Interrupt Control On-chip ROM for program code Timer/Counter On-chip RAM Timer 1 Timer 0 CPU OSC Bus Control 4 I/O Ports P0 P1 P2 P3 Address/Data Serial Port TxD RxD Counter Inputs The 8051 Microcontroller—A Brief History In 1980, Intel introduced the 8051, relevant today after more than two decades First device in the MCS-51® family of 8-bit microcontrollers In addition to Intel there are other second source suppliers of the ICs, who make microcontrollers that are compatible with the 8051 architecture. In recent years some companies have incorporated many different and additional features into 8051 In 2000, Silicon Laboratories introduced a field programmable, mixed-signal chip (C8051F020) based on the 8051 core CPU Is 8-bit Still Relevant? “n-bit” – the “n” refers to the data bus width of the CPU, and is the maximum width of data it can handle at a time PCs with 64-bit microprocessors are becoming common Over 55% of all processors sold per year are 8-bit processors, which comes to over 3 billion of them per year!* 8-bit microcontrollers are sufficient and cost-effective for many embedded applications More and more advanced features and peripherals are added to 8-bit processors by various vendors 8-bit MCUs are well-suited for low-power applications that use batteries *Note: Statistics from Embedded.com Article ID# 9900861, Dec 2002 Example System: RC Car Antenna Forward RF Transmitter Microcontroller Antenna RF Receiver Microcontroller Front Electric Motor (Left/Right) Reverse Left Right Controls Power Power Voltage Regulator Voltage Regulator Batteries Batteries Rear Electric Motor (Fwd/Reverse) Car lights (LEDs) Comparison of the 8051 Family Members Feature ROM (program space in bytes) RAM (bytes) Timers I/O pins Serial port Interrupt sources 8051 4K 128 2 32 1 6 8052 8K 256 3 32 1 8 8031 0K 128 2 32 1 6 8051 and 8052 The feature set of the 8052 is the superset of the 8051 In addition to all the features of the 8051, the 8052 includes 128 bytes internal RAM (total of 256 bytes) A third 16-bit timer, with new modes of operation Additional SFRs to support the third timer The Silicon Labs C8051F020 builds upon the 8052, and adds further features The term “8051” is typically used in place of “8052”, and also refers to the 8051 architecture C8051F020 Data Memory (RAM) Internal Data Memory space is divided into three sections Lower 128 Upper 128 Special function register (SFR) There are 256 bytes of memory space physically, the Upper 128 and SFRs share the same addresses from location 80H to FFH. Appropriate instructions should be used to access each memory block Lower 128—Register Banks and RAM General Purpose RAM (80 bytes) Bit-addressable Area (16 bytes) Register Banks (8 bytes per bank; 4 banks) Special Function Registers (SFRs) SFRs provide control and data exchange with the microcontroller’s resources and peripherals Registers which have their byte addresses ending with 0H or 8H are byte- as well as bitaddressable Some registers are not bitaddressable. These include the stack pointer (SP) and data pointer register (DPTR) Summary of SFRs Accumulator (ACC) and B register ACC (also referred to as A) is used implicitly by several instructions B is used implicitly in multiply and divide operations These registers are the input/output of the arithmetic and logic unit (ALU) Program status word—PSW Shows the status of arithmetic and logical operations using multiple bits such as Carry Selects the Register Bank (Bank 0 - Bank 3) Stack pointer—SP Data pointer—DPTR (DPH and DPL) 16-bit register used to access external code or data memory Timer Registers—TH0, TL0, TH1, TL1, TMOD, TCON Used for timing intervals or counting events Parallel I/O Port Registers—P0, P1, P2 and P3 Serial Communication Registers—SBUF and SCON Interrupt Management Registers—IP and IE Power Control Register—PCON Pin Description of the 8051 PDIP P1.0 P1.1 P1.2 P1.3 P1.4 P1.5 P1.6 P1.7 RST (RXD)P3.0 (TXD)P3.1 (INT0)P3.2 (INT1)P3.3 (T0)P3.4 (T1)P3.5 (WR)P3.6 (RD)P3.7 XTAL2 XTAL1 GND 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 8051 (8031) 40 39 38 37 36 35 34 33 32 31 30 29 28 27 26 25 24 23 22 21 Vcc P0.0(AD0) P0.1(AD1) P0.2(AD2) P0.3(AD3) P0.4(AD4) P0.5(AD5) P0.6(AD6) P0.7(AD7) EA/VPP ALE/PROG PSEN P2.7(A15) P2.6(A14) P2.5(A13) P2.4(A12) P2.3(A11) P2.2(A10) P2.1(A9) P2.0(A8) Pins of 8051(1/4) Vcc(pin 40): Vcc provides supply voltage to the chip. The voltage source is +5V. GND(pin 20):ground XTAL1 and XTAL2(pins 19,18): These 2 pins provide external clock. Way 1:using a quartz crystal oscillator Way 2:using a TTL oscillator Example 4-1 shows the relationship between XTAL and the machine cycle. Pins of 8051(2/4) RST(pin 9):reset It is an input pin and is active high(normally low). The high pulse must be high at least 2 machine cycles. It is a power-on reset. Upon applying a high pulse to RST, the microcontroller will reset and all values in registers will be lost. Reset values of some 8051 registers Way 1:Power-on reset circuit Way 2:Power-on reset with debounce Pins of 8051(3/4) /EA(pin 31):external access There is no on-chip ROM in 8031 and 8032 . The /EA pin is connected to GND to indicate the code is stored externally. /PSEN & ALE are used for external ROM. For 8051, /EA pin is connected to Vcc. “/” means active low. /PSEN(pin 29):program store enable This is an output pin and is connected to the OE pin of the ROM. See Chapter 14. Pins of 8051(4/4) ALE(pin 30):address latch enable It is an output pin and is active high. 8051 port 0 provides both address and data. The ALE pin is used for de-multiplexing the address and data by connecting to the G pin of the 74LS373 latch. I/O port pins The four ports P0, P1, P2, and P3. Each port uses 8 pins. All I/O pins are bi-directional. Figure 4-2 (a). XTAL Connection to 8051 Using a quartz crystal oscillator We can observe the frequency on the XTAL2 pin. C2 XTAL2 30pF C1 XTAL1 30pF GND Figure 4-2 (b). XTAL Connection to an External Clock Source N C Using a TTL oscillator XTAL2 is unconnected. EXTERNAL OSCILLATOR SIGNAL XTAL2 XTAL1 GND Example : Find the machine cycle for (a) XTAL = 11.0592 MHz (b) XTAL = 16 MHz. Solution: (a) 11.0592 MHz / 12 = 921.6 kHz; machine cycle = 1 / 921.6 kHz = 1.085 s (b) 16 MHz / 12 = 1.333 MHz; machine cycle = 1 / 1.333 MHz = 0.75 s RESET Value of Some 8051 Registers: Register PC ACC B PSW SP DPTR RAM are all zero. Reset Value 0000 0000 0000 0000 0007 0000 Figure 4-3 (a). Power-On RESET Circuit Vcc + 10 uF 31 30 pF 11.0592 MHz 19 EA/VPP X1 8.2 K 30 pF 18 X2 9 RST Figure 4-3 (b). Power-On RESET with Debounce Vcc 31 10 uF EA/VPP X1 30 pF X2 RST 9 8.2 K Pins of I/O Port The 8051 has four I/O ports Port 0 (pins 32-39):P0(P0.0~P0.7) :P1(P1.0~P1.7) Port 2(pins 21-28):P2(P2.0~P2.7) Port 3(pins 10-17):P3(P3.0~P3.7) Each port has 8 pins. Named P0.X (X=0,1,...,7), P1.X, P2.X, P3.X Ex:P0.0 is the bit 0(LSB)of P0 Ex:P0.7 is the bit 7(MSB)of P0 These 8 bits form a byte. Each port can be used as input or output (bi-direction). Port 1(pins 1-8) Registers A B R0 DPTR DPH DPL R1 R2 PC PC R3 R4 R5 R6 R7 Some 8-bitt Registers of the 8051 Some 8051 16-bit Register Some Simple Instructions MOV dest,source MOV MOV MOV MOV A,#72H A, #’r’ R4,#62H B,0F9H MOV MOV MOV DPTR,#7634H DPL,#34H DPH,#76H MOV P1,A ; dest = source ;A=72H ;A=‘r’ OR 72H ;R4=62H ;B=the content of F9’th byte of RAM ;mov A to port 1 Note 1: MOV A,#72H After instruction “MOV ≠ MOV A,72H A,72H ” the content of 72’th byte of RAM will replace in Accumulator. 8086 MOV MOV MOV MOV 8051 AL,72H AL,’r’ BX,72H AL,[BX] MOV MOV A,#72H A,#’r’ MOV A,72H MOV A,3 Note 2: MOV A,R3 ≡ ADD A, Source ;A=A+SOURCE ADD A,#6 ;A=A+6 ADD A,R6 ;A=A+R6 ADD A,6 ;A=A+[6] or A=A+R6 ADD A,0F3H ;A=A+[0F3H] SETB CLR SETB SETB SETB SETB SETB bit bit C P0.0 P3.7 ACC.2 05 ; bit=1 ; bit=0 ; CY=1 ;bit 0 from port 0 =1 ;bit 7 from port 3 =1 ;bit 2 from ACCUMULATOR =1 ;set high D5 of RAM loc. 20h Note: CLR instruction is as same as SETB i.e: CLR C ;CY=0 But following instruction is only for CLR: CLR A ;A=0 Bit Addressable Page 359,360 SUBB A,source ;A=A-source-CY SETB C SUBB A,R5 ;CY=1 ;A=A-R5-1 ADDC A,source SETB C ADDC ;CY=1 A,R5 ;A=A+source+CY ;A=A+R5+1 DEC INC byte byte ;byte=byte-1 ;byte=byte+1 INC DEC DEC R7 A 40H ; [40]=[40]-1 CPL A ;1’s complement Example: L01: MOV CPL MOV ACALL SJMP NOP & RET & RETI All are like 8086 instructions. A,#55H ;A=01010101 B A P1,A DELAY L01 CALL JUMP ANL - ORL - XRL EXAMPLE: ANL A,#08H ANL ANL A,08H A,R5 RR – RL – RRC – RLC A EXAMPLE: RR A MUL & DIV MUL MOV MOV MUL DIV MOV MOV DIV A,B A,#25H B,#65H A,B AB A,#25 B,#10 A,B ;A*B ;25H*65H=0E99 ;B=0EH, A=99H ;A = A/B, B = A mod B ;A=2, B=5 Structure of Assembly language and Running an 8051 program EDITOR PROGRAM ORG MOV MOV MOV ADD ADD HERE: SJMP HERE END 0H R5,#25H R7,#34H Myfile.lst A,#0 A,R5 A,#12H Myfile.asm ASSEMBLER PROGRAM Other obj file Myfile.obj LINKER PROGRAM Myfile.abs OH PROGRAM Myfile.hex Memory mapping in 8051 ROM memory map in 8051 family 4k 0000H 8k 32k 0000H 0000H 0FFFH DS5000-32 8751 AT89C51 1FFFH 8752 AT89C52 7FFFH from Atmel Corporation from Dallas Semiconductor RAM memory space allocation in the 8051 7FH Scratch pad RAM 30H 2FH Bit-Addressable RAM 20H 1FH Register Bank 3 18H 17H 10H 0FH 08H 07H 00H Register Bank 2 (Stack) Register Bank 1 Register Bank 0 8051 Flag bits and the PSW register PSW Register CY AC F0 RS1 RS0 Carry flag Auxiliary carry flag Available to the user for general purpose Register Bank selector bit 1 Register Bank selector bit 0 Overflow flag User define bit Parity flag Set/Reset odd/even parity RS1 RS0 Register Bank OV -- P PSW.7 PSW.6 PSW.5 PSW.4 PSW.3 PSW.2 PSW.1 PSW.0 CY AC -RS1 RS0 OV -P Address 0 0 0 00H-07H 0 1 1 08H-0FH 1 0 2 10H-17H 1 1 3 18H-1FH Instructions that Affect Flag Bits: Note: X can be 0 or 1 Example: MOV A,#88H ADD A,#93H 88 +93 ---11B CY=1 AC=0 10001000 +10010011 -------------00011011 P=0 9C +64 ---100 CY=1 AC=1 Example: MOV A,#38H ADD A,#2FH 38 +2F ---67 CY=0 AC=1 Example: MOV A,#9CH ADD A,#64H 00111000 +00101111 -------------01100111 P=1 10011100 +01100100 -------------00000000 P=0 Addressing Modes Immediate Register Direct Register Indirect Indexed Immediate Addressing Mode MOV MOV MOV MOV MOV A,#65H A,#’A’ R6,#65H DPTR,#2343H P1,#65H Example : Num … MOV MOV … ORG data1: EQU 30 R0,Num DPTR,#data1 100H db “IRAN” Register Addressing Mode MOV Rn, A ;n=0,..,7 ADD A, Rn MOV DPL, R6 MOV DPTR, A MOV Rm, Rn Direct Addressing Mode Although the entire of 128 bytes of RAM can be accessed using direct addressing mode, it is most often used to access RAM loc. 30 – 7FH. MOV MOV MOV MOV R0, 40H 56H, A A, 4 6, 2 ; ≡ MOV A, R4 ; copy R2 to R6 ; MOV R6,R2 is invalid ! SFR register and their address MOV MOV MOV 0E0H, #66H 0F0H, R2 80H,A ; ≡ MOV A,#66H ; ≡ MOV B, R2 ; ≡ MOV P1,A Bit Addressable Page 359,360 Register Indirect Addressing Mode In this mode, register is used as a pointer to the data. MOV A,@Ri MOV @R1,B ; move content of RAM loc.Where address is held by Ri into A ( i=0 or 1 ) In other word, the content of register R0 or R1 is sources or target in MOV, ADD and SUBB insructions. Example: Write a program to copy a block of 10 bytes from RAM location sterting at 37h to RAM location starting at 59h. Solution: MOV R0,37h MOV R1,59h MOV R2,10 L1: MOV A,@R0 MOV @R1,A INC R0 INC R1 DJNZ R2,L1 ; source pointer ; dest pointer ; counter jump Indexed Addressing Mode And On-Chip ROM Access This mode is widely used in accessing data elements of look-up table entries located in the program (code) space ROM at the 8051 MOVC A,@A+DPTR A= content of address A +DPTR from ROM Note: Because the data elements are stored in the program (code ) space ROM of the 8051, it uses the instruction MOVC instead of MOV. The “C” means code. Example: Assuming that ROM space starting at 250h contains “Hello.”, write a program to transfer the bytes into RAM locations starting at 40h. Solution: ORG 0 MOV DPTR,#MYDATA MOV R0,#40H L1: CLR A MOVC A,@A+DPTR JZ L2 MOV @R0,A INC DPTR INC R0 SJMP L1 L2: SJMP L2 ;------------------------------------ORG 250H MYDATA:DB “Hello”,0 END Notice the NULL character ,0, as end of string and how we use the JZ instruction to detect that. Example: Write a program to get the x value from P1 and send x2 to P2, continuously . Solution: ORG 0 MOV DPTR, #TAB1 MOV A,#0FFH MOV P1,A L01: MOV A,P1 MOVC A,@A+DPTR MOV P2,A SJMP L01 ;---------------------------------------------------ORG 300H TAB1: DB 0,1,4,9,16,25,36,49,64,81 END Stack in the 8051 The register used to access the stack is called SP (stack pointer) register. 7FH Scratch pad RAM 30H The stack pointer in the 8051 is only 8 bits wide, which means that it can take value 00 to FFH. When 8051 powered up, the SP register contains value 07. 2FH Bit-Addressable RAM 20H 1FH 18H 17H 10H 0FH 08H 07H 00H Register Bank 3 Register Bank 2 (Stack) Register Bank 1 Register Bank 0 Example: MOV MOV MOV PUSH PUSH PUSH R6,#25H R1,#12H R4,#0F3H 6 1 4 0BH 0BH 0BH 0BH 0AH 0AH 0AH 0AH F3 09H 09H 09H 12 09H 12 08H 08H 08H 25 08H 25 Start SP=07H 25 SP=08H SP=09H SP=08H LOOP and JUMP Instructions DJNZ: Write a program to clear ACC, then add 3 to the accumulator ten time Solution: MOV MOV AGAIN: ADD DJNZ MOV A,#0; R2,#10 A,#03 R2,AGAIN ;repeat until R2=0 (10 times) R5,A Other conditional jumps JZ Jump if A=0 JNZ Jump if A/=0 DJNZ Decrement and jump if register /=0 CJNE A,byte Jump if A/=byte CJNE reg,#data Jump if byte/=#data JC Jump if CY=1 JNC Jump if CY=0 JB Jump if bit=1 JNB Jump if bit=0 JBC Jump if bit=1 and clear bit SJMP and LJMP: LJMP(long jump) LJMP is an unconditional jump. It is a 3-byte instruction in which the first byte is the opcode, and the second and third bytes represent the 16-bit address of the target location. The 2 byte target address allows a jump to any memory location from 0000 to FFFFH. SJMP(short jump) In this 2-byte instruction. The first byte is the opcode and the second byte is the relative address of the target location. The relative address range of 00-FFH is divided into forward and backward jumps, that is , within -128 to +127 bytes of memory relative to the address of the current PC. Example 3-6 Using the following list tile, verify the jump forward address calculation. Line 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 PC 0000 0000 0002 0004 0006 0007 0008 0009 000B 000D 000E 000F 0010 0011 0012 0013 0015 0017 Op-code 7800 7455 6003 08 04 04 2477 5005 E4 F8 F9 FA FB 2B 50F2 80FE AGAIN: NEXT: OVER: HERE: Mnemonic ORG 0000 MOV R0, #0 MOV A, #55H JZ NEXT INC R0 INC A INC A ADD A, #77h JNC OVER CLR A MOV R0, A MOV R1, A MOV R2, A MOV R3, A ADD A, R3 JNC AGAIN SJMP HERE END Operand CJNE , JNC Exercise: Write a program that compare R0,R1. If R0>R1 then send 1 to port 2, else if R0<R1 then send 0FFh to port 2, else send 0 to port 2. CALL Instructions Another control transfer instruction is the CALL instruction, which is used to call a subroutine. LCALL(long call) In this 3-byte instruction, the first byte is the opcode an the second and third bytes are used for the address of target subroutine. Therefore, LCALL can be used to call subroutines located anywhere within the 64K byte address space of the 8051. ACALL (absolute call) ACALL is 2-byte instruction in contrast to LCALL, which is 3 bytes. Since ACALL is a 2-byte instruction, the target address of the subroutine must be within 2K bytes address because only 11 bits of the 2 bytes are used for the address. There is no difference between ACALL and LCALL in terms of saving the program counter on the stack or the function of the RET instruction. The only difference is that the target address for LCALL can be anywhere within the 64K byte address space of the 8051 while the target address of ACALL must be within a 2K-byte range. I/O Port Programming Port 1(pins 1-8) Port 1 is denoted by P1. P1.0 ~ P1.7 We use P1 as examples to show the operations on ports. P1 as an output port (i.e., write CPU data to the external pin) P1 as an input port (i.e., read pin data into CPU bus) A Pin of Port 1 Read latch TB2 Vcc Load(L1) Internal CPU bus D Write to latch Clk P1.X pin Q P1.X Q M1 TB1 P0.x Read pin 8051 IC Hardware Structure of I/O Pin Each pin of I/O ports Internal CPU bus:communicate with CPU A D latch store the value of this pin D latch is controlled by “Write to latch” Write to latch=1:write data into the D latch 2 Tri-state buffer: TB1: controlled by “Read pin” Read pin=1:really read the data present at the pin TB2: controlled by “Read latch” Read latch=1:read value from internal latch A transistor M1 gate Gate=0: open Gate=1: close Tri-state Buffer Output Input Tri-state control (active high) L L H H H H Low Highimpedance (open-circuit) Writing “1” to Output Pin P1.X Read latch Vcc TB2 Load(L1) 2. output pin is Vcc 1. write a 1 to the pin Internal CPU bus D Write to latch Clk 1 Q P1.X pin P1.X Q 0 M1 TB1 Read pin 8051 IC output 1 Writing “0” to Output Pin P1.X Read latch Vcc TB2 Load(L1) 2. output pin is ground 1. write a 0 to the pin Internal CPU bus D Write to latch Clk 0 Q P1.X pin P1.X Q 1 M1 TB1 Read pin 8051 IC output 0 Port 1 as Output(Write to a Port) Send data to Port 1: BACK: MOV A,#55H MOV P1,A ACALL DELAY CPL A SJMP BACK Let P1 toggle. You can write to P1 directly. Reading Input vs Port Latch When reading ports, there are two possibilities: Read the status of the input pin. (from external pin value) MOV A, PX JNB P2.1, TARGET ; jump if P2.1 is not set JB P2.1, TARGET ; jump if P2.1 is set Figures C-11, C-12 Read the internal latch of the output port. ANL P1, A ; P1 ← P1 AND A ORL P1, A ; P1 ← P1 OR A INC P1 ; increase P1 Figure C-17 Table C-6 Read-Modify-Write Instruction (or Table 8-5) See Section 8.3 Reading “High” at Input Pin Read latch 1. TB2 write a 1 to the pin MOV P1,#0FFH Internal CPU bus 2. MOV A,P1 Vcc external pin=High Load(L1) D 1 Q 1 P1.X Write to latch Clk 0 Q M1 TB1 Read pin 3. Read pin=1 Read latch=0 Write to latch=1 8051 IC P1.X pin Reading “Low” at Input Pin Read latch 1. Vcc 2. MOV A,P1 TB2 write a 1 to the pin Load(L1) external pin=Low MOV P1,#0FFH Internal CPU bus D 1 Q 0 P1.X Write to latch Clk Q 0 M1 TB1 Read pin 3. Read pin=1 Read latch=0 Write to latch=1 8051 IC P1.X pin Port 1 as Input(Read from Port) In order to make P1 an input, the port must be programmed by writing 1 to all the bit. BACK: MOV MOV MOV MOV SJMP A,#0FFH P1,A A,P1 P2,A BACK ;A=11111111B ;make P1 an input port ;get data from P1 ;send data to P2 To be an input port, P0, P1, P2 and P3 have similar methods. Instructions For Reading an Input Port Following are instructions for reading external pins of ports: Mnemonics Examples Description MOV A,PX MOV A,P2 Bring into A the data at P2 pins JNB PX.Y,.. JNB P2.1,TARGET Jump if pin P2.1 is low JB PX.Y,.. JB P1.3,TARGET Jump if pin P1.3 is high MOV C,PX.Y MOV C,P2.4 Copy status of pin P2.4 to CY Reading Latch Exclusive-or the Port 1: MOV P1,#55H ;P1=01010101 ORL P1,#0F0H ;P1=11110101 1. The read latch activates TB2 and bring the data from the Q latch into CPU. Read P1.0=0 2. CPU performs an operation. This data is ORed with bit 1 of register A. Get 1. 3. The latch is modified. D latch of P1.0 has value 1. 4. The result is written to the external pin. External pin (pin 1: P1.0) has value 1. Reading the Latch 1. Read pin=0 Read latch=1 Write to latch=0 (Assume P1.X=0 initially) Read latch Vcc TB2 Load(L1) 2. CPU compute P1.X OR 1 0 Internal CPU bus D 1 Write to latch 3. write result to latch Read pin=0 Read latch=0 Write to latch=1 0 Q P1.X Clk 1 0 M1 Q TB1 Read pin 8051 IC 4. P1.X=1 P1.X pin Read-modify-write Feature Read-modify-write Instructions Table C-6 This features combines 3 actions in a single instruction: 1. CPU reads the latch of the port 2. CPU perform the operation 3. Modifying the latch 4. Writing to the pin Note that 8 pins of P1 work independently. Port 1 as Input(Read from latch) Exclusive-or the Port 1: MOV P1,#55H ;P1=01010101 AGAIN: XOR P1,#0FFH ;complement ACALL DELAY SJMP AGAIN Note that the XOR of 55H and FFH gives AAH. XOR of AAH and FFH gives 55H. The instruction read the data in the latch (not from the pin). The instruction result will put into the latch and the pin. Read-Modify-Write Instructions Mnemonics Example ANL ANL P1,A ORL ORL P1,A XRL XRL P1,A JBC PX.Y, TARGET JBC P1.1, TARGET CPL CPL P1.2 INC INC DEC DEC P1 DJNZ PX, TARGET DJNZ P1,TARGET MOV PX.Y,C MOV P1.2,C CLR PX.Y CLR P1.3 SETB PX.Y SETB P1.4 P1 You are able to answer this Questions: How to write the data to a pin? How to read the data from the pin? Read the value present at the external pin. Why we need to set the pin first? Read the value come from the latch(not from the external pin). Why the instruction is called read-modify write? Other Pins P1, P2, and P3 have internal pull-up resisters. P1, P2, and P3 are not open drain. P0 has no internal pull-up resistors and does not connects to Vcc inside the 8051. P0 is open drain. Compare the figures of P1.X and P0.X. However, for a programmer, it is the same to program P0, P1, P2 and P3. All the ports upon RESET are configured as output. A Pin of Port 0 Read latch TB2 Internal CPU bus D Write to latch Clk P0.X pin Q P1.X Q M1 TB1 P1.x Read pin 8051 IC Port 0(pins 32-39) P0 is an open drain. Open drain is a term used for MOS chips in the same way that open collector is used for TTL chips. When P0 is used for simple data I/O we must connect it to external pull-up resistors. Each pin of P0 must be connected externally to a 10K ohm pull-up resistor. With external pull-up resistors connected upon reset, port 0 is configured as an output port. Port 0 with Pull-Up Resistors Vcc Port P0.0 DS5000 P0.1 P0.2 8751 P0.3 P0.4 8951 P0.5 P0.6 P0.7 10 K 0 Dual Role of Port 0 When connecting an 8051/8031 to an external memory, the 8051 uses ports to send addresses and read instructions. 8031 is capable of accessing 64K bytes of external memory. 16-bit address:P0 provides both address A0-A7, P2 provides address A8-A15. Also, P0 provides data lines D0-D7. When P0 is used for address/data multiplexing, it is connected to the 74LS373 to latch the address. There is no need for external pull-up resistors as shown in Chapter 14. 74LS373 PSEN ALE P0.0 P0.7 74LS373 G D OE OC A0 A7 D0 D7 EA P2.0 A8 P2.7 A15 8051 ROM Reading ROM (1/2) P0.0 2. 74373 latches the address and send to OE ROM OC G 74LS373 A0 P0.7 A7 PSEN ALE 1. Send address to ROM D Address D0 D7 EA P2.0 A8 P2.7 A12 8051 ROM Reading ROM (2/2) PSEN ALE P0.0 P0.7 2. 74373 latches the address and send to ROM 74LS373 G D Address OE OC A0 A7 D0 D7 EA 3. ROM send the instruction back P2.0 A8 P2.7 A12 8051 ROM ALE Pin The ALE pin is used for de-multiplexing the address and data by connecting to the G pin of the 74LS373 latch. When ALE=0, P0 provides data D0-D7. When ALE=1, P0 provides address A0-A7. The reason is to allow P0 to multiplex address and data. Port 2(pins 21-28) Port 2 does not need any pull-up resistors since it already has pull-up resistors internally. In an 8031-based system, P2 are used to provide address A8-A15. Port 3(pins 10-17) Port 3 does not need any pull-up resistors since it already has pull-up resistors internally. Although port 3 is configured as an output port upon reset, this is not the way it is most commonly used. Port 3 has the additional function of providing signals. Serial communications signal:RxD, TxD(Chapter 10) External interrupt:/INT0, /INT1(Chapter 11) Timer/counter:T0, T1(Chapter 9) External memory accesses in 8031-based system:/WR, /RD(Chapter 14) Port 3 Alternate Functions P3 Bit Function Pin P3.0 P3.1 P3.2 P3.3 P3.4 P3.5 P3.6 P3.7 RxD TxD INT0 INT1 T0 T1 WR RD 10 11 12 13 14 15 16 17