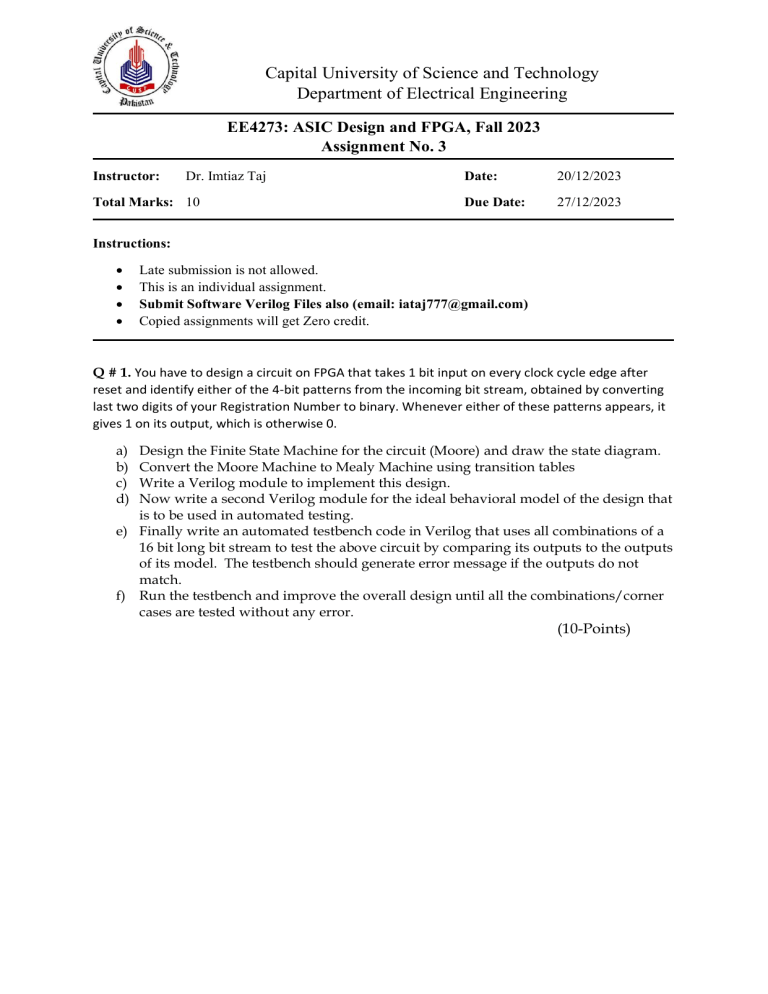

Capital University of Science and Technology Department of Electrical Engineering EE4273: ASIC Design and FPGA, Fall 2023 Assignment No. 3 Instructor: Dr. Imtiaz Taj Total Marks: 10 Date: 20/12/2023 Due Date: 27/12/2023 Instructions: • • • • Late submission is not allowed. This is an individual assignment. Submit Software Verilog Files also (email: iataj777@gmail.com) Copied assignments will get Zero credit. Q # 1. You have to design a circuit on FPGA that takes 1 bit input on every clock cycle edge after reset and identify either of the 4-bit patterns from the incoming bit stream, obtained by converting last two digits of your Registration Number to binary. Whenever either of these patterns appears, it gives 1 on its output, which is otherwise 0. a) b) c) d) Design the Finite State Machine for the circuit (Moore) and draw the state diagram. Convert the Moore Machine to Mealy Machine using transition tables Write a Verilog module to implement this design. Now write a second Verilog module for the ideal behavioral model of the design that is to be used in automated testing. e) Finally write an automated testbench code in Verilog that uses all combinations of a 16 bit long bit stream to test the above circuit by comparing its outputs to the outputs of its model. The testbench should generate error message if the outputs do not match. f) Run the testbench and improve the overall design until all the combinations/corner cases are tested without any error. (10-Points)

![Avoiding Trafficked Labor [English]](http://s2.studylib.net/store/data/027039054_1-3047401815af88cce843a8404da043fb-300x300.png)

![[John.Wakerly].Digital.Design.Principles.Practices.5th](http://s2.studylib.net/store/data/027247669_1-81a86ec10df8e7720f38b90e8be12390-300x300.png)