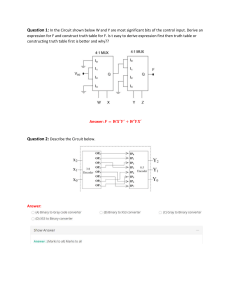

DESIGN OF SEQUENTIAL CIRCUITS DR. D. EZHILARASI DEPT. OF ICE NIT, TRICHY DESIGN COUNTER THAT GOES THRU STATES 0,3,5,6 ELIMINATION OF LOCKOUT 4 BIT RING COUNTER TWISTED RING COUNTER OR JOHNSON COUNTER PULSE TRAIN GENERATORS DIRECT LOGIC PULSE TRAIN GENERATORS DIRECT LOGIC INDIRECT LOGIC USING RIPPLE COUNTER THE FINITE STATE MODEL/MACHINE • It is a machine whose past histories can affect their future behaviour only in a finite number of ways i,e machine with a fixed number of states • Two types of models • Moore circuit- output depends only on present state of the FF • Mealy Circuit- output depends on both the present state of the FFs and the inputs MEALY MODEL MOORE MODEL MEALY TO MOORE CONVERSION MOORE TO MEALY MODEL Moore Model Mealy Model The output is a function of present state only Input changes does not affect the output directly Moore model requires more number of states for implementing same function The output is a function of present state as well as present input Input changes may affect the output of the circuit It requires less number of states for implementing same function ANALYSIS OF CLOCKED SEQUENTIAL CIRCUITS CONSTRUCT TRANSITION TABLE, STATE TABLE & STATE DIAGRAM FOR MOORE CIRCUIT STATE REDUCTION MODEL OF FF’S – D FF T FF SR FF JK FF PROCEDURE FOR THE DESIGN OF SEQUENTIAL CIRCUITS • State diagram • State table • State reduction • Binary value assignment • Number of required FFs • Type of FF • From state table derive circuit excitation and output table • Obtain functions for Input to FFs and output using K map • Draw sequential logic circuit RULES FOR STATE ASSIGNMENT • States having the same next state for a given input conditions should have assignments which can be grouped into logically adjacent cells in K map • States that are the next state of a single state should have assignment which can be grouped into logically adjacent cells in a K map Need: Complexity of combinational circuit depends on binary state assignment Binary values are to be assigned to the states in such a way that it is possible to implement FF input functions using minimum logic gates Binary state assignment is less important to the circuits whose external outputs are taken directly from FF with binary sequence fully specified SELECTION OF FF • Transfer of data (Shift register) - D FF • Complementation (Counter) - T FF • General Application - JK FF • Step 1: Assign binary values to each state • Step 2: Decide required number of FFs • Derive Excitation table • Derive circuit output and FFs output • Draw the sequential logic circuit RANDOM STATE ASSIGNMENT A long sequence of pulses enters a synchronous sequential circuit which is required to produce an output of Z=1 whenever the sequence 1111 occurs. Overlapping sequence are accepted. For example if the input is 01011111, the required output is 00011000 Design the circuit. State table Transition table Transition table From state table derive circuit excitation and output table 1) Detect the sequence a) 1010 b) b)1011 2) Design a synchronous sequential circuit which produces an output Z=1, whenever any of the following input sequences 1100, 1010 or 1001 occurs. The circuit resets to its initial state after a 1 output has been generated.