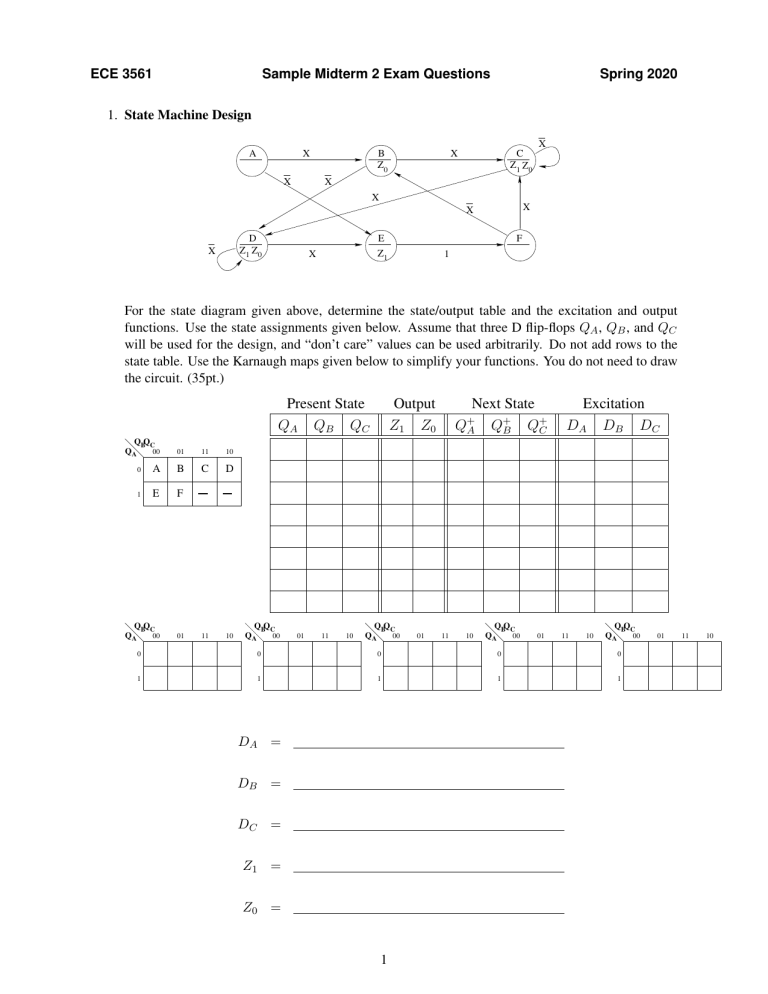

ECE 3561 Sample Midterm 2 Exam Questions Spring 2020 1. State Machine Design A X X B Z0 X X X D Z1 Z0 X X X X E Z1 X C Z1 Z0 F 1 For the state diagram given above, determine the state/output table and the excitation and output functions. Use the state assignments given below. Assume that three D flip-flops QA , QB , and QC will be used for the design, and “don’t care” values can be used arbitrarily. Do not add rows to the state table. Use the Karnaugh maps given below to simplify your functions. You do not need to draw the circuit. (35pt.) Present State QA QB QC QBQC QA 00 01 11 10 0 A B C D 1 E F QBQC QA 00 01 11 10 QBQC QA 00 01 11 10 Output Z 1 Z0 QBQC QA 00 01 Next State Q+ Q+ B C Q+ A 11 10 QBQC QA 00 01 Excitation DA DB DC 11 10 QBQC QA 00 0 0 0 0 0 1 1 1 1 1 DA = DB = DC = Z1 = Z0 = 1 01 11 10 2. State Diagram Draw a state diagram for a clocked synchronous state machine with two inputs (X and RESET ) and two Mealy-type outputs (Y and Z). A binary coded data stream is fed to X (one bit input at every clock). Based on the data stream received up to now, the proper outputs should be asserted as follows: • If the sequence 100 is recognized in X, output Y is asserted, • If the sequence 111 is recognized in X, output Z is asserted, and • If neither 100 nor 111 is recognized, none of the outputs is asserted. RESET will reset the system, i.e., it will take the system to a state where all previous inputs are assumed to be zero. Indicate the meaning of state labels. 2 3. State Machine Design I A I B Z0 I E Z1 I I I I I I D Z1 Z0 I C Z1 For the state diagram given above, determine the state/output table and the excitation and output functions. For state variable assignment, use A = 000, B = 001, C = 010, D = 011, and E = 100. Use three D flip-flops QA , QB , and QC , and use don’t care values for unused states. You do not need to draw the circuit. 3 4. State Machine Design Consider a control circuit that controls the gate arm of a parking lot exit. The controller is connected to two sensor (A and B) that indicate the presence of a vehicle in front of them. One of the sensors (A) is located 0.5m in front of the gate arm, and the other (B) 0.5 behind the gate arm. The gate arm is controlled with the output Z of the controller, where Z=1 keeps the gate open and Z=0 keeps it closed. • The gate opens when a car approaches the gate and triggers sensor A. • Cars are long enough for both sensors to sense vehicles as they pass through the gate. • The gate closes when the passing car is no longer sensed by sensor B. • Between two exiting cars, there is a non-zero space. • The controller prevents cars from entering the parking lot through this gate. • The system should account for the possibility of a car moving backwards after starting to go through the gate, which should lead to closing the gate once it clears sensor A. Draw the state diagram for this circuit as a Moore Machine. 4 5. FPGA Programming (not covered in Midterm 2) The following figure shows a CLB (Configurable Logic Block) in a FPGA device. Assuming that • the external inputs ABCD are connected to G4 G3 G2 G1 and F4 F3 F2 F1 , • the external input E is connected to H1 , and • Y is connected to the external output Z, as shown in the figure, we want to program G(G1 implement the following logic function F4 ), and H(F, G, H1) in order to G4 ), F (F1 Z = B D̄E + B̄DĒ + ABC. E A B C D Z Problem: Fill in the SRAMs on the next page corresponding to G, F, H blocks. Clearly explain your answer. G block F block H block G4 − G1 0000 F4 − F1 0000 H1 G F 0 0 0 0001 0010 0001 0010 0 0 1 0 1 0 0011 0100 0011 0100 0 1 1 1 0 0 0101 0110 0101 0110 1 0 1 1 1 0 0111 1000 1001 0111 1000 1001 1 1 1 1010 1011 1100 1101 1110 1010 1011 1100 1101 1110 1111 1111 5 6. State Minimization Minimize the number of states in the state table below as much as possible. Draw the state diagram for the minimized state table. P.S. Input N.S. Output Q X Q+ Z a 0 b 1 a 1 c 1 b 0 d 0 b 1 f 0 c 0 b 0 c 1 c 1 d 0 b 1 d 1 c 1 e 0 a 0 e 1 f 0 f 0 e 1 f 1 a 0 6 7. State Minimization Minimize the number of states in the state table below as much as possible. Identify all state equivalences explicitly. Draw the state diagram for the minimized state table. P.S. Input N.S. Output Q X Q+ Z a 0 b 0 a 1 f 1 b 0 e 0 b 1 a 0 c 0 d 1 c 1 c 1 d 0 e 0 d 1 f 1 e 0 e 0 e 1 a 0 f 0 d 1 f 1 c 1 g 0 d 0 g 1 c 1 h 0 b 0 h 1 c 1 7 8. Additional Questions from the Text Book In addition to the homework assignments, solving questions from the text book is also recommended. The following questions are examples of recommended questions: Chapter 14: 14.4, 14.5, 14.6, 14.7, 14.8, 14.9, 14.10, 14.11 Chapter 15: 15.1, 15.2, 15.3, 15.6, 15.7, 15.8, 15.10, 15.11, 15.12, 15.13, 15.14 8