Analysis of Random Dopant Fluctuations and Oxide

advertisement

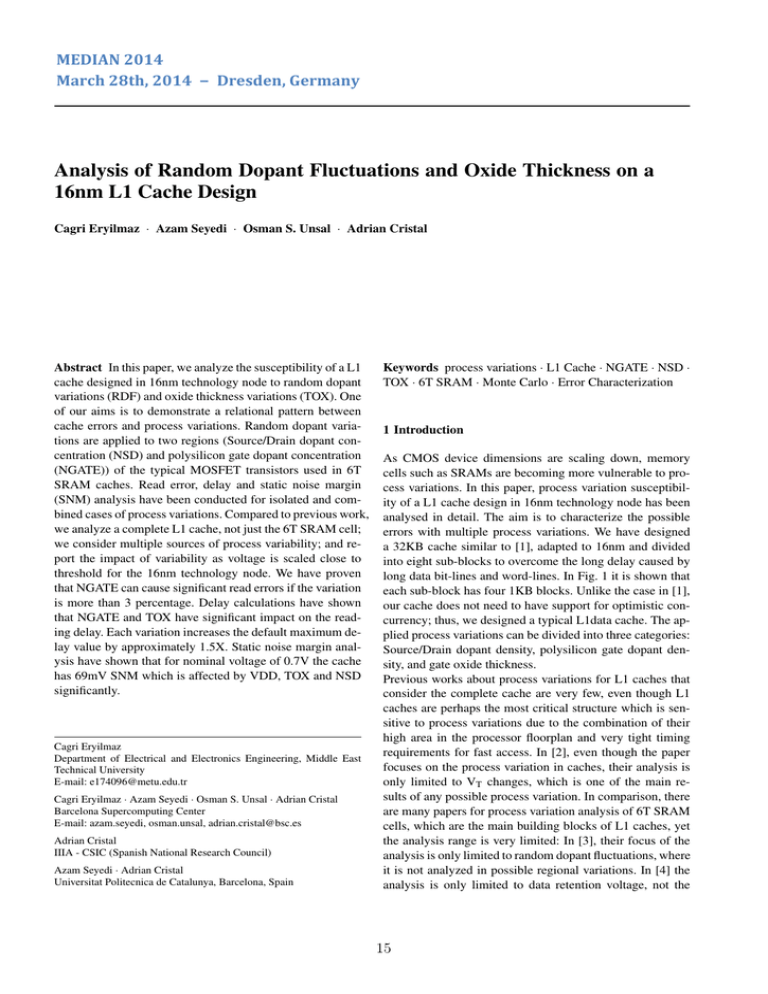

MEDIAN 2014 Noname manuscript No. (will be inserted the editor) March 28th,by2014 − Dresden, Germany Analysis of Random Dopant Fluctuations and Oxide Thickness on a 16nm L1 Cache Design Cagri Eryilmaz · Azam Seyedi · Osman S. Unsal · Adrian Cristal Received: date / Accepted: date Abstract In this paper, we analyze the susceptibility of a L1 cache designed in 16nm technology node to random dopant variations (RDF) and oxide thickness variations (TOX). One of our aims is to demonstrate a relational pattern between cache errors and process variations. Random dopant variations are applied to two regions (Source/Drain dopant concentration (NSD) and polysilicon gate dopant concentration (NGATE)) of the typical MOSFET transistors used in 6T SRAM caches. Read error, delay and static noise margin (SNM) analysis have been conducted for isolated and combined cases of process variations. Compared to previous work, we analyze a complete L1 cache, not just the 6T SRAM cell; we consider multiple sources of process variability; and report the impact of variability as voltage is scaled close to threshold for the 16nm technology node. We have proven that NGATE can cause significant read errors if the variation is more than 3 percentage. Delay calculations have shown that NGATE and TOX have significant impact on the reading delay. Each variation increases the default maximum delay value by approximately 1.5X. Static noise margin analysis have shown that for nominal voltage of 0.7V the cache has 69mV SNM which is affected by VDD, TOX and NSD significantly. Cagri Eryilmaz Department of Electrical and Electronics Engineering, Middle East Technical University E-mail: e174096@metu.edu.tr Cagri Eryilmaz · Azam Seyedi · Osman S. Unsal · Adrian Cristal Barcelona Supercomputing Center E-mail: azam.seyedi, osman.unsal, adrian.cristal@bsc.es Adrian Cristal IIIA - CSIC (Spanish National Research Council) Azam Seyedi · Adrian Cristal Universitat Politecnica de Catalunya, Barcelona, Spain Keywords process variations · L1 Cache · NGATE · NSD · TOX · 6T SRAM · Monte Carlo · Error Characterization 1 Introduction As CMOS device dimensions are scaling down, memory cells such as SRAMs are becoming more vulnerable to process variations. In this paper, process variation susceptibility of a L1 cache design in 16nm technology node has been analysed in detail. The aim is to characterize the possible errors with multiple process variations. We have designed a 32KB cache similar to [1], adapted to 16nm and divided into eight sub-blocks to overcome the long delay caused by long data bit-lines and word-lines. In Fig. 1 it is shown that each sub-block has four 1KB blocks. Unlike the case in [1], our cache does not need to have support for optimistic concurrency; thus, we designed a typical L1data cache. The applied process variations can be divided into three categories: Source/Drain dopant density, polysilicon gate dopant density, and gate oxide thickness. Previous works about process variations for L1 caches that consider the complete cache are very few, even though L1 caches are perhaps the most critical structure which is sensitive to process variations due to the combination of their high area in the processor floorplan and very tight timing requirements for fast access. In [2], even though the paper focuses on the process variation in caches, their analysis is only limited to VT changes, which is one of the main results of any possible process variation. In comparison, there are many papers for process variation analysis of 6T SRAM cells, which are the main building blocks of L1 caches, yet the analysis range is very limited: In [3], their focus of the analysis is only limited to random dopant fluctuations, where it is not analyzed in possible regional variations. In [4] the analysis is only limited to data retention voltage, not the 15 2 other possible failures such as delay. In our paper we aimed to analyze gate dopant density, Source/Drain dopant densities as random dopant fluctuations, region by region, and gate oxide thickness for a complete L1 cache design, where all the peripheral circuits are also included in the analysis so that we could test a real cache structure in 16nm node. Our results are aimed to help the designers of the future caches in 16nm. We conducted extensive Monte Carlo simulations to characterize process variations, as full-scale Monte Carlo simulations are necessary at the 22nm technology node and beyond [13]. Our testing mechanism shows partial differences in a typical MOSFET structure can result in different types of failures in the circuit. It has been found that NSD variations do not cause delay; on the other hand, they significantly increase the static noise margin. NGATE variations are effective on delay for different dopant levels. Even though NGATE is not effective on static noise margin values, we show that significant read errors are observed as a result of NGATE variations, when the variation is more than 3 percentage. On the other hand, gate oxide thickness (TOX) variations have significant impact not only on the delay of the circuit (by increasing it by 1.5X) but also on the SNM (by increasing it 7mv for each ten percentages increase of the density). Even though the main focus of this work is on quantifying the impact of the different types of process variations, it is important to point out that lowering the voltage in a circuit is an important factor since it makes the circuit more vulnerable to variations. For that reason, responses of each process variation is also simulated for different voltage levels, from the nominal voltage of 0.7V to Vccmin of 0.45V for the 16nm technology node [11]. It is important to analyse the impact of variability at various low-voltage levels as near threshold operation provides energy efficiency [12]. This paper makes two main contributions: Cagri Eryilmaz et al. Fig. 1 General view of L1 Cache [1] is defined as the density of the polysilicon which is used for gate electrode [5], [6]. NSD is defined as Source/Drain areas dopant densities. We conducted Monte Carlo simulations in Cadence Spectre circuit simulator to simulate the process variations in the cache. The cache is designed by using 16nm Predictive Technology Model (PTM) [7] and BSIM4 model [5]. The process variations are applied not only to the cells of the cache but also to the sense amplifier, the write/read circuitries and the precharge units of the cache. All sub-blocks of the cache are used for testing purposes and parasitic effects are also included so that testing can be applied properly. All of the variations (TOX, NGATE, and NSD) are applied to PTM model file by putting statistical blocks to initiate Monte Carlo simulations. Parameters of dopant densities and oxide thickness are varied using a Gaussian distribution with standard deviation of 0.07 and 0.12 respectively [8]. 3 Results and Evalutaion 3.1 Delay Propagation delay (tpd ) of 6T SRAM is directly related to Cox which is stated in equation (1) [9]. In Fig. 2 TOX variations are applied for different voltages in Monte Carlo anal1. Regional dopant density analysis. ysis for different values of TOX parameter. For each volt2. L1 cache process variation analysis in 16nm technology age value delay is exponentially increasing with the increase node. of TOX parameter. Moreover, high value of TOX (Monte Carlo Parameter = 1.179) may cause significant exponenIn section II of the paper we define the terms used in the patial increase while lowering the VDD voltage.NSD variaper and give the simulation methodology. The results and tions do not cause a significant change in the circuits delay. evaluation section III is divided into two sub-sections: 1) NSD+TOX variation is applied to circuit for comparison and Delay 2) Read Error and Static Noise Margin. Conclusion it is proven that the effect of NSD variations to delay is negand possible future work are stated at section IV. ligible; however, the change of TOX variable is affecting the delay significantly as stated previously. In Fig. 3, it is again proven for different voltage levels that TOX is dominant 2 Background and Methodology factor compared to NSD. Polysilicon gate dopant density Process variations can be observed in many aspects. In this (NGATE) variations become dominant when gate is doped paper we have applied gate oxide thickness (TOX) variamore than desired. It is obvious that the circuit is affected, tions, Source/Drain dopant density (NSD) and polysilicon please refer to the increase in delay in Table I; however, the gate density (NGATE) variations. Gate oxide thickness is change is linear. If TOX and NGATE variations are applied the thickness of the oxide for typical MOS transistors. NGATE together, it is again proved that TOX is dominant factor of 16 Analysis of Random Dopant Fluctuations and Oxide Thickness on a 16nm L1 Cache Design 3 Fig. 3 Delay of reading bit value 1 when TOX+NSD variations are applied and VDD is swept through 0.7 to 0.45V Fig. 2 Delay of reading bit value 1 from 6T SRAM cell, when TOX variation is applied for voltages from 0.45V to 0.7V. Monte Carlo parameter applied to TOX model variable is swept from 0.80697 to 1.179. determining delay, where the delay is following the pattern of change in TOX variation parameter. In Table I delay values for different cases are provided. It is important to point out that TOX + NGATE case has almost 1.5 times of the delay caused by the TOX solely for maximum delay values. NGATE has different effects if it is heavily or lightly doped, causing the step-like pattern results. This effect stems from the change in flat band voltage which directly affects VT [6]. The threshold voltage is important parameter for IDS , which is one of the parameters for speed, i.e. delay, of the MOSFET circuits. t pd = tT + 1.7 Fo ∗CW +Co L ∗ ((Fo ∗ L2 ) + ∗ ) Uo Cox W (1) 3.2 Read Error and Static Noise Margin NGATE variation is the significant factor of the read errors. Read error is defined as the flipping the stored value or destroying the cell value. In Fig. NSD and NGATE variations on read error rate are given for separate and also combined cases. NGATE causes read errors with the rate of 59 percentage. NGATE + NSD case has 50 percentage read error rate; however, NSD does not cause any read error solely. Static noise margin (SNM) is a critical attribute for memory cells. Our cache has 69mV SNM in nominal voltage of 0.7V. In Fig. 5 and Fig. 6 it is demonstrated that SNM is decreasing with decreasing VDD . SNM has inverse relationship with oxide thickness. In Fig. 5 each ten percentages increase in TOX causes approximately 7mV decrease in SNM. SNM has a direct relationship with the Source/Drain doping concentration (NSD). It is expected that SNM should increase with the increase of NSD. Threshold voltage is increasing with the increase of NSD [3]. Since SNM is directly related to the threshold voltage, SNM is also increasing. In Fig. 7, the pattern of NSD Monte Carlo parameter variation with respect Fig. 4 Read error rates for RDF cases with Gaussian distribution (Sigma=0.07) (f=2GHz) to TOX parameter variation is given. The pattern of the NSD in Fig. 7 can be seen in Fig. 6 where the variation of TOX is below 10 percentage. In Fig. 6 when TOX+NSD variation is applied, overall change in static noise margin over time is small and negligible since they try to change the SNM in opposite directions, where ten percentages increase in NSD and TOX causes approximately 4mV increase and 7mV decrease in SNM respectively. Gate dopant density (NGATE) is not affecting the static noise margin. Since it is not related the substrate, at which the acceptors and donors are, it is expected for NGATE not to have any effect. Monte Carlo simulations have proven that there is no change with the change of NGATE Monte Carlo parameter. 4 Conclusion and Future Work A L1 cache is tested in 16nm technology node and it is exposed to process variations while lowering the VDD . Variations are gate oxide thickness variation (TOX), polysilicon gate doping density (NGATE) and Source-Drain doping density (NSD). The relation, the pattern between the process variations and possible failures, is discussed. TOX variations are exponentially effective on delay and static noise margin. NSD variations are effective on delay linearly. Despite the low standard deviation of NSD, there is a significant increase in delay values. NSD also has an impact on 17 4 Cagri Eryilmaz et al. Table 1 Delays of reading bit value 1 from the 6T SRAM cell. All results are in picosecond. Oxide thickness variations and random dopant fluctuation variations are applied with Gaussian standard deviations 0.12 and 0.07 respectively. Fig. 7 NSD Monte Carlo Parameter variation with respect to TOX variation in Fig. 6. SNM values directly. NGATE has different behavior on affecting the circuit, that is, even though NGATE is not affecting SNM, it is significantly effective on read errors. As future work, we would like to analyse process variations and soft error vulnerability together; towardsthis goal random injections of soft errors, i.e. particle strikes, will be analysed. In another research direction, special architectural design to detect possible variety in a cache will be designed, which it can adjust itself to different recovery mechanism in order to assure reliability in cache. References Fig. 5 SNM analysis with TOX variation. X-Axis represents the Monte Carlo parameter variation applied to nominal 16nm PTM model file. Fig. 6 SNM analysis with TOX +NSD variation. X-Axis represents the Monte Carlo parameter variation applied to nominal 16nm PTM model file 1. A. Seyedi et al. ”Circuit Design of a Dual-Versioning L1 Data Cache for Optimistic Concurrency”, in GLSVLSI 2011. 2. Liu, S.: Formal Engineering for Industrial Software A. Agarwal et al. ”Process Variation in Embedded Memories: Failure Analysis and Variation Aware Architecture”, JSSC 2005. 3. T.-Y. Li et al. ”Process-Variation- and Random-Dopant-Induced Static Noise Margin Fluctuation in Nanoscale CMOS and FinFET SRAM Cells”, in ASQED 2009. 4. ”International Technology Roadmap for Semiconductors”, E. Vatajelu et al. ”Statistical Analysis of 6T SRAM Data Retention Voltage under Process Variation”, in DDECS 2011. 5. T. Morshed et al. ”BSIM4v4.7 MOSFET Model - User Manual”, University of California, Berkeley, 2011, Available:http://wwwdevice.eecs.berkeley.edu/bsim/Files/BSIM4/BSIM470/ 6. R. Dutta et al. ”Effect of Polysilicon Gate Doping Concentration Variation on MOSFET Characteristics”, in CODEC 2012. 7. ”Predictive Technology Model”, Available:http://ptm.asu.edu/. 8. ”International Technology Roadmap for Semiconductors”, Available: www.itrs.net/Links/2007ITRS/Home2007.htm. 9. V. N. Rayapati et al. ”Interconnect Propagation Delay Modelling and Validation for the 16-MB CMOS SRAM Chip”, IEEE Transactions on Components, Packaging1996. 10. R. F. Pierret, ”Semiconductor Device Fundamentals”, AddisonWesley Publishing 1996. 11. F. Hijaz et al. ”Low-Latency Mechanisms for Near-Threshold Operation of Private Caches in Shared Memory Multicores”, Workshop on Near-threshold Computing, Co-located with Micro, December 2012 12. D. Fick et al. ”Centip3De: A 3930DMIPS/W configurable nearthreshold 3D stacked system with 64 arm cortex-M3 cores”, ISSCC 2012 13. Sarah Q. Xu, Kai Xiu, Phil Oldiges, ”Investigation of the Impact of Random Dopant Fluctuation on Static Noise Margin of 22nm SRAM”, SISPAD 2012 18