Investigation Of Poly-si1 Xgex For Dual

advertisement

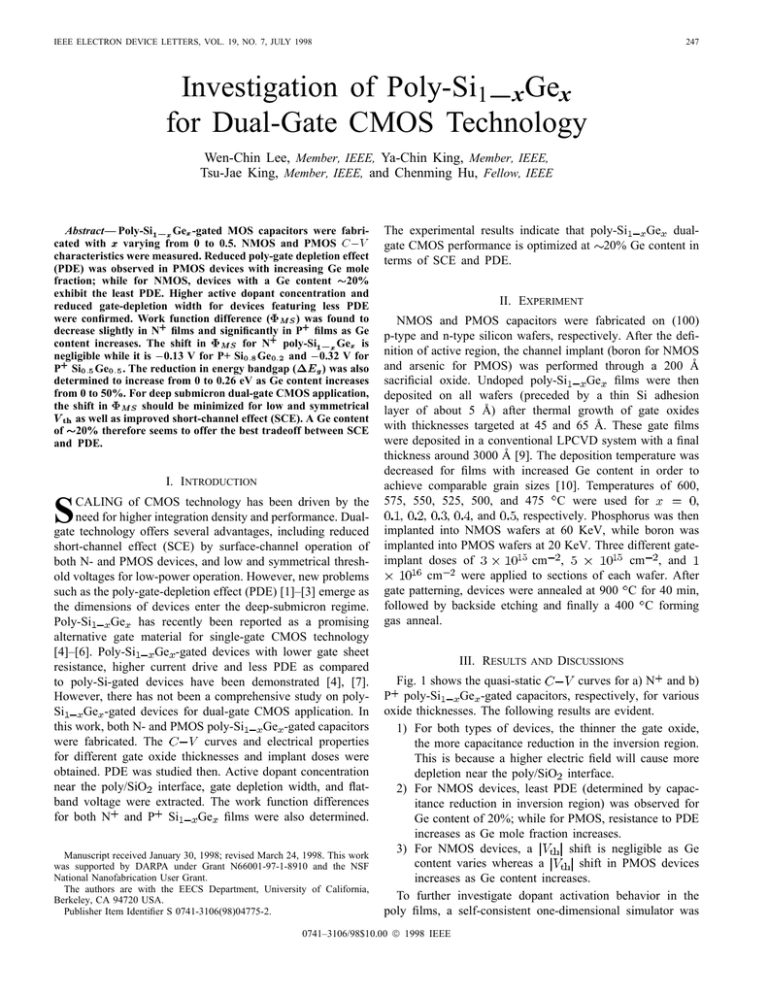

IEEE ELECTRON DEVICE LETTERS, VOL. 19, NO. 7, JULY 1998 247 Investigation of Poly-Si1 xGex for Dual-Gate CMOS Technology Wen-Chin Lee, Member, IEEE, Ya-Chin King, Member, IEEE, Tsu-Jae King, Member, IEEE, and Chenming Hu, Fellow, IEEE Abstract— Poly-Si10x Gex -gated MOS capacitors were fabricated with x varying from 0 to 0.5. NMOS and PMOS C 0V characteristics were measured. Reduced poly-gate depletion effect (PDE) was observed in PMOS devices with increasing Ge mole fraction; while for NMOS, devices with a Ge content 20% exhibit the least PDE. Higher active dopant concentration and reduced gate-depletion width for devices featuring less PDE were confirmed. Work function difference ( M MS S ) was found to decrease slightly in N+ films and significantly in P+ films as Ge + poly-Si Gexx is content increases. The shift in M MS S for N 10x negligible while it is 00.13 V for P+ Si0:8 Ge0:2 and 00.32 V for P+ Si0:5 Ge0:5 . The reduction in energy bandgap ( E g ) was also determined to increase from 0 to 0.26 eV as Ge content increases from 0 to 50%. For deep submicron dual-gate CMOS application, the shift in M MS S should be minimized for low and symmetrical V th as well as improved short-channel effect (SCE). A Ge content of 20% therefore seems to offer the best tradeoff between SCE and PDE. 8 8 1 8 I. INTRODUCTION S CALING of CMOS technology has been driven by the need for higher integration density and performance. Dualgate technology offers several advantages, including reduced short-channel effect (SCE) by surface-channel operation of both N- and PMOS devices, and low and symmetrical threshold voltages for low-power operation. However, new problems such as the poly-gate-depletion effect (PDE) [1]–[3] emerge as the dimensions of devices enter the deep-submicron regime. Ge has recently been reported as a promising Poly-Si alternative gate material for single-gate CMOS technology Ge -gated devices with lower gate sheet [4]–[6]. Poly-Si resistance, higher current drive and less PDE as compared to poly-Si-gated devices have been demonstrated [4], [7]. However, there has not been a comprehensive study on polyGe -gated devices for dual-gate CMOS application. In Si Ge -gated capacitors this work, both N- and PMOS poly-Si curves and electrical properties were fabricated. The for different gate oxide thicknesses and implant doses were obtained. PDE was studied then. Active dopant concentration near the poly/SiO interface, gate depletion width, and flatband voltage were extracted. The work function differences Ge films were also determined. for both N and P Si Manuscript received January 30, 1998; revised March 24, 1998. This work was supported by DARPA under Grant N66001-97-1-8910 and the NSF National Nanofabrication User Grant. The authors are with the EECS Department, University of California, Berkeley, CA 94720 USA. Publisher Item Identifier S 0741-3106(98)04775-2. The experimental results indicate that poly-Si Ge dualgate CMOS performance is optimized at 20% Ge content in terms of SCE and PDE. II. EXPERIMENT NMOS and PMOS capacitors were fabricated on (100) p-type and n-type silicon wafers, respectively. After the definition of active region, the channel implant (boron for NMOS and arsenic for PMOS) was performed through a 200 Å Ge films were then sacrificial oxide. Undoped poly-Si deposited on all wafers (preceded by a thin Si adhesion layer of about 5 Å) after thermal growth of gate oxides with thicknesses targeted at 45 and 65 Å. These gate films were deposited in a conventional LPCVD system with a final thickness around 3000 Å [9]. The deposition temperature was decreased for films with increased Ge content in order to achieve comparable grain sizes [10]. Temperatures of 600, , 575, 550, 525, 500, and 475 C were used for , , , , and , respectively. Phosphorus was then implanted into NMOS wafers at 60 KeV, while boron was implanted into PMOS wafers at 20 KeV. Three different gatecm , cm , and implant doses of cm were applied to sections of each wafer. After gate patterning, devices were annealed at 900 C for 40 min, followed by backside etching and finally a 400 C forming gas anneal. III. RESULTS AND DISCUSSIONS Fig. 1 shows the quasi-static curves for a) N and b) Ge -gated capacitors, respectively, for various P poly-Si oxide thicknesses. The following results are evident. 1) For both types of devices, the thinner the gate oxide, the more capacitance reduction in the inversion region. This is because a higher electric field will cause more depletion near the poly/SiO interface. 2) For NMOS devices, least PDE (determined by capacitance reduction in inversion region) was observed for Ge content of 20%; while for PMOS, resistance to PDE increases as Ge mole fraction increases. shift is negligible as Ge 3) For NMOS devices, a shift in PMOS devices content varies whereas a increases as Ge content increases. To further investigate dopant activation behavior in the poly films, a self-consistent one-dimensional simulator was 0741–3106/98$10.00 1998 IEEE 248 IEEE ELECTRON DEVICE LETTERS, VOL. 19, NO. 7, JULY 1998 (a) (a) (b) (b) 0 Fig. 1. Comparison of measured quasi-static C V for (a) NMOS and (b) PMOS poly-Si10x Gex -gated capacitors. Devices are compared for different gate oxide thicknesses: 47 and 67 Å for the same gate doping concentration. employed. This simulator accounts for both PDE and inversion-layer quantization effects [8]. The active dopant , electric field near the poly/SiO concentration—N interface and flat-band voltage can be obtained by simply curves to the model with high fitting measured sensitivity (within 5% variation of the actual value). By assuming a constant doping concentration, the gate depletion at the interface can be calculated. Fig. 2 width— and (at shows the comparison of extracted N V) data for a) NMOS and b) PMOS capacitors, respectively, with various Ge contents and gate implant doses. The following characteristics were observed. reaches its maximum 1) For NMOS devices, N value at 20% Ge content for various gate implant doses, which might result from the competition between increased secondary grain growth and lowered phosphorus solid solubility with higher Ge content in polyGe [11]; while for PMOS devices, N Si shows a rapid increase as Ge content increases up to 20% and then a slower increase for higher Ge contents. This trend agrees with dopant activation characteristics found in [12] with the difference in the peak location for Ge case attributed to the increasing the N poly-Si grain size as Ge content increases in [12], as compared to the more comparable grain sizes used in this work. 0 Fig. 2. Comparison of extracted Npoly-inter and Xdeplet : (at Vg Vt = 2 V) data for (a) NMOS and (b) PMOS capacitors with various Ge contents and gate implant doses. 2) If higher implant dose is used, higher N and are obtained, as expected. smaller or reduction of 3) Little gain in N is achieved when implant dosage increases from cm to cm , especially for Ge content higher than 20%. , work-function difference From can be extrapolated from ’s for various gate oxide thicknesses. The reduction in energy bandgap can then be for polycalculated by Ge as compared to poly-Si. Here and Si define the shift in for N and P polyGe , respectively. Fig. 3 shows , Si and as a function of Ge content. For N poly-Si Ge , is negligible; while for P poly-Si Ge , is eV for and eV for . was found to decrease as Ge content increases. It is 0.1 eV for 20% Ge and 0.26 eV for 50% Ge. In consideration of the tradeoff between high N and low implant cost, poly-Si Ge gate with a dosage of 10 cm is recommended for both N- and PMOS 5 devices. Furthermore, if sufficient channel doping must be maintained in order to suppress SCE and to obtain symmetrical ’s, small will be necessary. By taking both Ge dual-gate CMOS PDE and SCE into account, poly-Si performance can therefore be optimized at Ge content 20%. LEE et al.: INVESTIGATION OF POLY-SI1 x Gex FOR DUAL-GATE CMOS TECHNOLOGY 249 REFERENCES [1] B. Ricco, R. Versari, and D. Esseni, “Characterization of polysilicongate depletion in MOS structures,” IEEE Trans. Electron Devices, vol. 17. pp. 103–105, Mar. 1996. [2] C.-L. Huang, N. D. Arora, A. I. Nasr, and D. A. Bell, “Effect of polysilicon depletion on MOSFET I –V characteristics,” Electron. Lett., vol. 29, no. 13, pp. 1208–1209, 1993. [3] K. F. Schuegraf, C. C. King, and C. Hu, “Impact of polysilicon depletion in thin oxide MOS technology,” VLSI TSA, pp. 86–90, 1993. [4] T. J. King, J. R. Pfiester, J. D. Shott, J. P. McVittie, and K. C. Saraswat, “Polycrystalline-Si10 Ge -gate CMOS technology,” in IEDM Tech. Dig., 1990, pp. 253–256. [5] N. Kistler and J. Woo, “Symmetric CMOS in fully-depleted siliconon-insulator using P+ -polycrystalline SiGe gate electrodes,” in IEDM Tech. Dig., 1993, pp. 727–730. [6] T. C. Hsiao, A. W. Wang, K. Saraswat, and J. C. S. Woo, “An alternative gate electrode material of fully depleted SOI CMOS for low power applications,” in Proc. 1997 IEEE Int. SOI Conf., 1997, pp. 20–21. [7] Y. V. Ponomarev, C. Salm, J. Schmitz, P. H. Woerlee, and D. J. Gravesteijn, “High-performance deep submicron MOST’s with polycrystalline-(Si,Ge) gates,” VLSI TSA, pp. 311–315, 1997. [8] Y.-C. King, H. Fujioka, S. Kamohara, and C. Hu, “AC charge centroid model for quantization of inversion layer in n-MOSFET,” VLSI TSA, pp. 245–249, 1997. [9] M. Cao, A. Wang, and K. C. Saraswat, “Low pressure chemical vapor deposition of Si10 Ge films on SiO2 ,” J. Electrochem. Soc., vol. 142, no. 5, pp. 1566–1572, 1995. [10] T.-J. King and K. C. Saraswat, “Deposition and properties of lowpressure chemical-vapor deposited polycrystalline silicon–germanium films,” J. Electrochem. Soc., vol. 141, no. 8, pp. 2235–2241, 1994. [11] F. A. Trumbore, “Solid solubilities of impurity elements in germanium and silicon,” Bell Syst. Tech. J., vol. 39, pp. 205–233, 1960. [12] T. J. King, J. P. McVittie, K. C. Saraswat, and J. R. Pfiester, “Electrical properties of heavily doped polycrystalline silicon–germanium films,” IEEE Trans. Electron Devices, vol. 41. pp. 228–232, Feb. 1994. x x Fig. 3. Reduction in poly-Si10x Gex energy bandgap as a function of Ge mole fraction. The error bars represent the deviation of 8 for each poly-Si10 Ge film. MS x x IV. CONCLUSION In summary, reduced poly-gate depletion effects (PDE) was observed in PMOS devices as gate Ge mole fraction is increased; while for NMOS, devices with a Ge content around ) 20% exhibit the least PDE. Work function difference ( was found to decrease slightly in N films and rapidly in P films as Ge content increases. For deep-submicron dualGe gate technology, gate CMOS application with poly-Si is preferable for better control of low and a small shift in , and improved short-channel effect (SCE) as symmetrical well. A Ge content of 20% is therefore the optimum choice in terms of SCE and PDE. x x