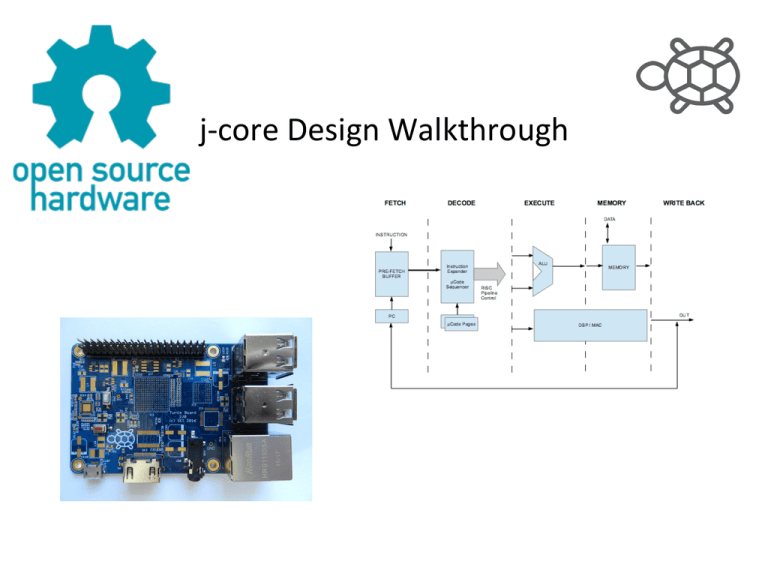

j-core Design Walkthrough - J

advertisement

j-coreDesignWalkthrough Q:WhatpartsofLinuxSystemsare OpenandUnderyourControl? • Modernlaptopshavemorearm/mipsprocessors thanx86 – USBcontroller?Exploitable: hJp://arstechnica.com/security/2014/07/this-thumbdrive-hacks-computersbadusb-exploit-makes-devices-turn-evil/ – Harddrivecontroller?Exploitable: hJp://hackaday.com/2013/08/02/sprite_tm-ohm2013-talk-hacking-hard-drivecontroller-chips/ • Systemmanagementmode,ACPI… • Doyoutrustyour<bigvendor’s>RNG? TakingBackControlofHWandSW Whatistheminimumsystem thatcanrunLinux? Thedefiniaonofa‘CPU’ (forthepurposesofthistalk) • HasaFlat32bitmemoryspace – Allpointers‘justwork’(noseparatespaces) • AportofGCC – Regular,efficient32-16-8bitint-short-char • Executesinstrucaons‘fastenough’ – ServicingstreamingEthernettraffic:about30MIPs SystemRequirements • CPU(ofcourse) • Memory – 8megsRAMrunspracacalLinuxworkloads – lessispossible,butawkward • Storage(loadkernel+initramfsintomemory) • SomeformofI/O – Usually,andatfirst,justaUART • ATimer(interrupt). Thingsyoudon’tneed • Anythingelse,actually – Video,audio,keyboard,persistentstorage • AnMMU,orany‘fancy’CPUfeatures. – FPU,SMP,evencacheisopaonal AHistoryLesson TheLinux/MicrocontrollerprojectisaportofLinuxtosystems withoutaMemoryManagementUnit(MMU). uClinuxfirstportedtotheMotorolaMC68328:DragonBallIntegrated Microprocessor.Thefirsttargetsystemtosuccessfullybootisthe PalmPilotusingaTRGSuperPilotBoardwithacustomboot-loader createdspecificallyforourLinux/PalmPilotport. (January1998) Whatdidwedo? • NewSH2instrucaonsetcompaablecoredesignkit – called"j2"becausetrademarkshaven'texpired. – clean-roomimplementaaon,iniaallybyCanadianengineers • builtfordesignreuse • ThenhiredoriginalSuperHteammemberstoworkonitamerwards – SourceisVHDLusingprogrammingmodeldevelopedbyEuropeanSpace Agency • Verilogislowlevellikeassembly,VHDLisaHLL • DesignKitcontainshighlevelabstracaonsforfuturecores • SOCbuildersystem – Linkstogetherperipheralsautomaacally • E.g.Serial,mmc,Ethernet • CanproduceFPGAbitstream,ASICRTL,Cemulatorsource • SMPcapablebutnotfinishedyet Whyrecreateexisangarchitecture? -Toolsexist:compiler,kernel,debugger,strace... -LeveragemassiveR&DoutlayinSuperH -5stageRISC(fullHarvardarchitecture) -instrucaonsetdensity(16bitfixedlength) -simplehighlyopamizeddesign -originaldesigners/implementerssallaround - Oldchipsarepriorartvs."breathingispatented” CodeDensity:Efficiency Source:hJp://web.eece.maine.edu/~vweaver/papers/iccd09/iccd09_density.pdf • There*Are*othermetrics,bitnoneactually maJermore(unlesssomethingisbroken) -Note:ARMpaidmillionstoHitachitouseSuperHpatentsin Thumbinstrucaonset…whichjustexpired. PatentExpiraaon • SuperHISAhadahugeeffortputintoit – SeeaboveaboutefficientGCC. • TheSuperHarchitecturewasdevelopedbyHitachia quartercenturyago. • LastpatentonSH2(SegaSaturn)expiredinOctober 2014. – That’swhywecanreleasethisnow – lastSH4(Dreamcast)patentexpiresin2016. • SuperHISAwastheblueprintforARMThumb ThebasicSuperHdesign: 5stage‘classical’RISCpipeline,withsomeaddiaons PreJysimpletoimplement,excepttheInstrucaonDecoder/Expander FPGAfloorplans:Spartan6&Kintex7 JSeriesComputaaonCoreClusterRoadmap Unit:ArithmeacOperaaonsperSecond 2TOps J4 32b RISC SMP + SIMD Array 0.5TOps DriverAssist Subsystem,Customer inAutomoave 128GOps 32GOps J2+ 32b RISC SMP + S-Core DSP Array 8GOps 2GOps 500MOps 125MOps 2014 J2 SignalProcessingIoT NextGeneraaonPower Transmissionand Distribuaon, Medical, InfrastructureSensors FirstDevice: SmartEnergyInstruments IoT/EnergyManagementSoC FPGAandASICimplementaaons 32b RISC GenericIoTDevices 2015 2016 2017 CalendarYear DemonstraaonPlazorms • Ourj2processorcorecanrunlinuxonlow-costFPGA Spartan6plazormssuchasNumatoLabs’Mimas2 • Wearelaunchingacustomdevelopmentboard(TurtleBoard) withthesameformfactorasRaspberryPi • (PleasesupportoutKickstarter) So,howdoyouuseitforanything? • VHDLandbuildsystemareunderaBSDlicense • JustuseanFPGA:$15getsyouUP,$40SMP+DSP – Plusanyperipheralyourapplicaaonrequires • Makeanychipyouwant – Royaltyfree • 180nmASICofSOCwe'redemoingcosts<10yen – Processoronly,about2andahalfcents • Disposablecompuangat"freetoyinside"level • ThinkIoT:‘TrillionSensorNetwork’economics,butrunningLinux • j-core.org,nommu.org(uclinux-ng), • Source,documentaaon,tutorials,mailinglists • Weassumeyou'veneverdonehardwarebefore. – Sallabitsparsebutfillingsitesoutaswego • Patcheswelcome.Noquesaontoostupid. PracacalHardware:FPGAsandASICs Source:Xilinx2014 How:VHDL,notVerilog AlthoughVerilogismorecommonlyusedincertain geographies.. • VHDListhepreferredlanguageindevelopmentsiniaatedor ledbytheEuropeanSpaceAgency. • TheVHSICHardwareDescripaonLanguage(VHDL)isaformal notaaonintendedforuseinallphasesofthecreaaonof electronicsystems.Becauseitisbothmachinereadableand humanreadable,itsupportsthedevelopment,verificaaon, synthesis,andtesangofhardwaredesigns,the communicaaonofhardwaredesigndata,andthe maintenance,modificaaon,andprocurementofhardware. These2thingsarenotthesame… • Actually… • It’saboutthetype system. • Verilogdon’thaveone (tospeakof) • InVHDL,everything*isa derivedtype. • Even+is‘just’and overloadedoperator. Goingfurther:StructuredVHDLDesignMethod • Inordertoovercomethelimitaaonsoftheclassical'dataflow' designstyle(largenumberofconcurrentVHDLstatements andprocesses,leadingtobadreadabilityandincreased simulaaoname),a'two-process'codingmethodisproposed: oneprocesscontainsallcombinaaonallogic,whereasthe otherprocessinfersall(andonly)theregisters. • Theuseofrecordtypestoincreasereadabilityandthesafe useofvariablestoreducesimulaaoname.Themethodhas beenappliedonseveraldesignsmadebyorforESA. -JiriGaisler,hDp://www.gaisler.com/doc/vhdl2proc.pdf AvoidingCommonErrors • Wedevelopedapre-processorperltool(v2p)toavoid latches,andothersimilarcodingerrors. – The.vhm fileisadialectofvhdl;sensiavitylistsaregeneratedbythe perlscript • ThishasresultedinhighlyreliableRTL,andgreatlyincreased theefficiencyofourinternaldevelopmentprocess EvenFurther:AutomatedISA-> RTLSim->FPGA->ASIC->SWToolsFlow CPU Generator ISPin .ods RTL Code SoC Generator Preprocess Processor Docs Wrapper RTL SoC Spec.ods Docs C Headers LinuxOS DevTree Synth RTL ToolChains FPGA Synth GHDL RTLSimulator StdCell Synthesis FPGA Verificaaon ASICFlow 2015/03/15 Docs Somware FirmwareFlow 23 ISAGenerator Whatcanyoudowiththisnow? • Downloadbitstream+vmlinux/initramfs,install onfpgaboard,bootkerneltoshellprompt • HOWTOswithbackgroundinfo – WheretoorderFPGAboard(s) – Downloadandinstallxilinx/digilenttools • Freedownloadforlinux/mac,butalasnoopensource bitstreamcompileryet.OpenOCDinstalleristodoitem. – Buildnewbitstreamfromsource – ProgramnommuLinux(gcc/binuals/musltoolchain) CodewalkThrough • SimpleVHDLExample – Simulaaon – Synthesisexample • SoCGeneratorInput – Peripheralsandbusses • CPUCorecodeorganizaaon – PipelineandISAdecodergenerator • CPURTLSimulaaon – RuntheRTLwithouthardware J-Core.org • WatchforaGitRepositoryandamailinglist: J-Core@J-Core.org hJp://Lists.J-Core.org