frac.-n synthesizer

advertisement

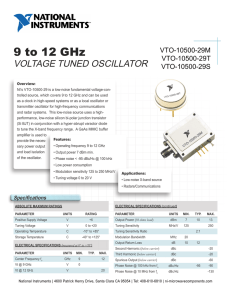

IMST Research Development Products Services SiGe INTEGRATED 8...12 GHz CHIP g FRAC.-N SYNTHESIZER OVERVIEW This SiGe fractional-N synthesizer has been developed for space applications such as satellite frequency converters. It features an on-board VCO (8...12 GHz or 17...20 GHz) and works with a dual-loop concept (coarse and fine regulation loop). It is protected against irradiation (triple mode redundancy) and aging. The chip delivers 0 dBm output power and can be programmed in the µHz-area in order to provide very high frequency accuracy and stability. Using any external VCO between 100 MHz and 20 GHz the chip can be used as an standalone PLL. In addition to the main frequency output port the chip also features (a f/2 output) port (e.g. 4...6 GHz) with a 6 dB better phase noise. FEATURES: APPLICATIONS: • Dual loop concept • Excellent phase noise performance • Integrated VCO • SPI and XILINX interface • Radiation hard • Frequency converters • PLLs • Frequency generators • Radar and sensor systems IMST GmbH Carl-Friedrich-Gauss-Str.2 47475 Kamp-Lintfort Germany T +49-2842-981-0 F +49-2842-981-199 E contact@imst.com I www.imst.com Copyright©2008 IMST GmbH - All rights reserved. Subject to technical changes without notice. IMST Research Development Products Services g Technical Data General Operation voltage: Power consumption: Dimensions (LxWxH): Technology: Interface SPI (serial processor interface): XLINX Prom: Tripple mode redundancy: Performance Data Frequency range: f/2 output: Temperature range: Phase noise integer mode (typ.): Phase noise fractional mode (typ.): Spurs: Harmonics: Loop-Filter: Sigma Delta Modulator: Charge pump current: Subbands: Temperature and aging compensation: Reference frequency: External VCO: Frequency accuracy: 8...12 GHz and 17...20 GHz (6 dB better phase noise) -40 ... +85 °C -100 dBc/Hz in loop, LBW 300 kHz, -110 dBc/Hz @ 1 MHz free running -95 dBc/Hz loop, -110 dBc/Hz @ 1 MHz free running < -60 dBc < -20 dBc/Hz dual loop, passive or active fine loop 1, 2, 3 or 4 stage (programmable) 8 bit programmable 8 subbands at 9 and 11 GHz, each subband 1 GHz bandwidth automatically done by dual-loop concept 50...100 MHz, up to 300 MHz with reference divider 100 MHz up to 20 GHz 1 µHz, 40 bit accumulators Typical phase noise performance (integer mode) IMST GmbH Carl-Friedrich-Gauss-Str.2 47475 Kamp-Lintfort Germany read/write, master slave 3.3.V and 5.5 V ~ 900 mW 6 mm x 1.5 mm x 0.6 mm IHP value (VD) BiCMOS + 0.25 µm CMOS T +49-2842-981-0 F +49-2842-981-199 E contact@imst.com I www.imst.com Illustration of bare die