UCN5816 - Allegro Microsystems

advertisement

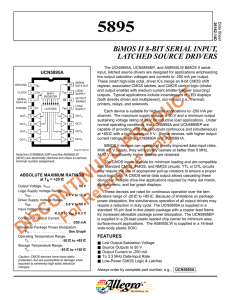

5816 4-TO-16 LINE LATCHED DECODER/DRIVERS UCN5816EP The UCN5816A and UCN5816EP 4-to-16 line latched decoder/ drivers combine low-power CMOS inputs and logic with 16 highcurrent, high-voltage bipolar outputs. The CMOS inputs cause minimal loading and are compatible with standard CMOS, PMOS, and NMOS logic. TTL or DTL circuits may require the use of appropriate pull-up resistors to ensure an input logic high. The logic operates over a supply range of 5 V to 12 V. A CHIP ENABLE function can be used with two devices for 5-to-32 line decoding applications. 5 IN D IN C IN B 27 26 CHIP ENABLE 1 28 STROBE 2 ST 3 LOGIC SUPPLY 4 OE DIODE 0-7 COMMON V DD OUTPUT ENABLE T C U Y D L O N R O P E D C E N U E N ER I T N EF O R C R S I O D F — LATCHES K IN A 25 DIODE 8-15 COMMON OUT0 6 K 24 OUT1 7 23 OUT 15 OUT2 8 22 OUT 14 OUT3 9 21 OUT 13 OUT4 10 20 OUT 12 OUT 5 11 19 OUT 11 OUT 10 18 17 OUT 9 15 GROUND OUT 8 16 14 GROUND OUT 7 13 OUT 6 12 DECODER Dwg. PP-030 The 16 bipolar power outputs are open-collector 60 V Darlington drivers capable of sinking 350 mA continuously. Internal transientsuppression diodes provide protection for use with inductive loads. For ink-jet printer applications, the A5817SEP addressable 28-line decoder/driver is recommended. The UCN5816A is supplied in a 28-pin dual in-line plastic package with 0.600" (15.24 mm) row spacing. The UCN5816EP is furnished in a 28-lead plastic chip carrier (quad pack) for minimum-area surfacemount applications. Both devices will drive 350 mA loads continuously over the full operating temperature range. FEATURES ABSOLUTE MAXIMUM RATINGS at TA = 25°C Output Voltage, VCE . . . . . . . . . . . . . . 60 V Logic Supply Voltage, VDD . . . . . . . . . 15 V Input Voltage Range, VIN . . . . . . . . . . . -0.3 V to VDD + 0.3 V Output Current, IC . . . . . . . . . . . . . 500 mA Package Power Dissipation, PD . . . . . . . . . . . . . . . . . . . See Graph Operating Temperature Range, TA . . . . . . . . . . . . . . . -20°C to +85°C Storage Temperature Range, TS . . . . . . . . . . . . . . -55°C to +150°C Caution: CMOS devices have input static protection but are susceptible to damage when exposed to extremely high static electrical charges. ■ ■ ■ ■ ■ ■ Addressable Data Entry 60 V Minimum Output Breakdown CMOS, PMOS, NMOS, TTL Compatible Inputs Low-Power CMOS Logic and Latches Output Transient Protection Output Enable and Strobe Functions Always order by complete part number: Part Number Package UCN5816A 28-Pin DIP UCN5816EP 28-Lead PLCC Data Sheet 26186.10 5816 4-TO-16 LINE LATCHED DECODER/DRIVERS 5816 4-TO-16 LINE LATCHED DECODER/DRIVERS UCN5816A 3 ST LOGIC SUPPLY 4 OUTPUT ENABLE OE 24 IN A DIODE 0-7 COMMON 6 K 23 DIODE 8-15 COMMON OUT 0 7 22 OUT15 OUT 1 8 21 OUT14 OUT 2 9 20 OUT13 OUT 3 10 19 OUT 12 OUT 4 11 18 OUT11 12 17 OUT10 OUT 6 13 16 OUT 9 14 15 OUT 8 OUT 5 OUT 7 K DECODER 2.0 1.5 1.0 /W °C 55 5 = INB A 25 θJ V DD ,R P' 'E IN C IX FF SU 26 LATCHES 2.5 /W °C 45 IND ALLOWABLE PACKAGE POWER DISSIPATION IN WATTS STROBE 27 = CE GROUND A θJ 2 28 R ', 'A 1 CHIP ENABLE IX FF SU GROUND 3.0 0.5 0 25 Dwg. PP-031 50 75 100 125 150 AMBIENT TEMPERATURE IN °C Dwg. GP-028-1A TYPICAL INPUT CIRCUITS VDD TYPICAL OUTPUT DRIVER V DD K IN OUT IN Dwg. EP-010-4A Dwg. EP-010-3 Dwg. EP-021-4 115 Northeast Cutoff, Box 15036 Worcester, Massachusetts 01615-0036 (508) 853-5000 W Copyright © 1984, 1995, Allegro MicroSystems, Inc. 5816 4-TO-16 LINE LATCHED DECODER/DRIVERS ELECTRICAL CHARACTERISTICS at TA = 25°C, VDD = 5 V (unless otherwise specified). Characteristic Output Leakage Current Output Saturation Voltage Input Voltage Symbol ICEX VCE(SAT) Supply Current RIN IDD(ON) IDD(OFF) Clamp Diode IR Leakage Current Clamp Diode Forward Voltage VF Min. Units VCE = 60 V, TA = +25°C — — 50 µA IC = 100 mA — 0.9 1.1 V IC = 200 mA — 1.1 1.3 V IC = 350 mA, VDD = 7.0 V — 1.3 1.6 V -0.3 — 0.8 V VDD = 12 V 10.5 — — V VDD = 5.0 V 3.5 — 5.3 V VDD = 12 V 50 200 — kΩ VDD = 5.0 V 100 600 — kΩ VDD = 12 V, Outputs Open — 2.0 3.0 mA VDD = 5.0 V, Outputs Open — 1.0 1.5 mA All Drivers OFF, All Inputs = 0 V, OE = VDD = 5.0 V — — 100 µA All Drivers OFF, All Inputs = 0 V, OE = VDD = 12 V — — 200 µA VR = 60 V, TA = +25°C — — 50 µA VR = 60 V, TA = +70°C — — 100 µA IF = 350 mA — 1.5 2.0 V VIN(0) VIN(1) Input Resistance Test Conditions Limits Typ. Max. 5816 4-TO-16 LINE LATCHED DECODER/DRIVERS CLEAR F STROBE A C OUTPUT ENABLE B C B C A G B G INN D E E OUTN p/o Dwg. No. A-10,895A TIMING CONDITIONS (Logic Levels are VDD and Ground) A. Minimum Data Active Time Before Strobe Enabled (Data Set-Up Time) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50 ns B. Minimum Data Active Time After Strobe Disabled (Data Hold Time) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50 ns C. Minimum Strobe Pulse Duration . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125 ns D. Typical Time Between Strobe Activation and Output On to Off Transition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 500 ns Information present at the inputs is transferred to the latches when the STROBE is high. The latches will continue to accept new data as long as the STROBE is held high. With the STROBE in the low state, no information can be loaded into the latches. Depending on the four address inputs, the 4-to-16 line decoder enables one of the 16 output sink drivers. When the OUTPUT ENABLE is high, all of the outputs are disabled (OFF) without affecting the information stored in the latches. When the OUTPUT ENABLE is low, the outputs are controlled by the information in the latches. When the CHIP ENABLE is low, all of the outputs are disabled (OFF). With two decoder/drivers and an inverter, the CHIP ENABLE function can be used for 5-to-32 line decoding applications. E. Typical Time Between Strobe Activation and Output Off to On Transition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 500 ns G. Minimum Data Pulse Duration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 225 ns TRUTH TABLE STROBE 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 0 X X CHIP ENABLE 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 0 X IND (MSB) 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 X X X INC INB 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 X X X 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 X X X INA (LSB) 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 X X X OUTPUT ENABLE 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 X 1 OUTPUTS (OFF unless otherwise specified) OUT0ON OUT1 ON OUT2 ON OUT3 ON OUT4 ON OUT5 ON OUT6 ON OUT7 ON OUT8 ON OUT9 ON OUT10 ON OUT11 ON OUT12 ON OUT13 ON OUT14 ON OUT15 ON QO All OFF All OFF QO = The output condition prior to the high-to-low transition of the STROBE input. X = Irrelevant 115 Northeast Cutoff, Box 15036 Worcester, Massachusetts 01615-0036 (508) 853-5000