For the Latest Version of my C.V. Please this PDF

advertisement

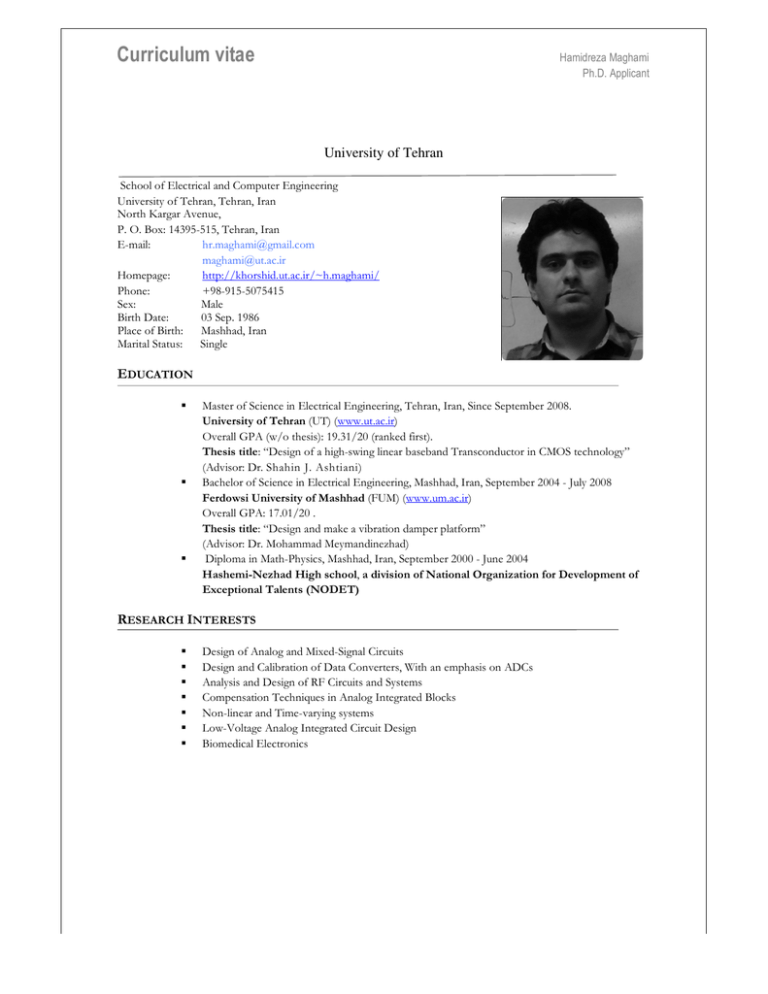

Curriculum vitae Hamidreza Maghami Ph.D. Applicant University of Tehran School of Electrical and Computer Engineering University of Tehran, Tehran, Iran North Kargar Avenue, P. O. Box: 14395-515, Tehran, Iran E-mail: hr.maghami@gmail.com maghami@ut.ac.ir Homepage: http://khorshid.ut.ac.ir/~h.maghami/ Phone: +98-915-5075415 Sex: Male Birth Date: 03 Sep. 1986 Place of Birth: Mashhad, Iran Marital Status: Single EDUCATION Master of Science in Electrical Engineering, Tehran, Iran, Since September 2008. University of Tehran (UT) (www.ut.ac.ir) Overall GPA (w/o thesis): 19.31/20 (ranked first). Thesis title: “Design of a high-swing linear baseband Transconductor in CMOS technology” (Advisor: Dr. Shahin J. Ashtiani) Bachelor of Science in Electrical Engineering, Mashhad, Iran, September 2004 - July 2008 Ferdowsi University of Mashhad (FUM) (www.um.ac.ir) Overall GPA: 17.01/20 . Thesis title: “Design and make a vibration damper platform” (Advisor: Dr. Mohammad Meymandinezhad) Diploma in Math-Physics, Mashhad, Iran, September 2000 - June 2004 Hashemi-Nezhad High school, a division of National Organization for Development of Exceptional Talents (NODET) RESEARCH INTERESTS Design of Analog and Mixed-Signal Circuits Design and Calibration of Data Converters, With an emphasis on ADCs Analysis and Design of RF Circuits and Systems Compensation Techniques in Analog Integrated Blocks Non-linear and Time-varying systems Low-Voltage Analog Integrated Circuit Design Biomedical Electronics Curriculum vitae Hamidreza Maghami Ph.D. Applicant HONORS Ranked 1st among all graduate electrical engineering students in M.Sc./Electronics Program, University of Tehran, Tehran, Iran. Ranked 68th in national exam for entrance in Master of Science program among more than 15000 students. Ranked 643th in National Universities Entrance Exam, Sep. 2004. Qualified as a member of National Organization for Developing Exceptional Talents (NODET), 1997-2004. Publications K. Nanbakhsh, H. R. Maghami, S. Sheikhaei, “A Low power 10-bit 100MS/s Pipelined ADC Using Correlated Level Shifting”, Accepted in CCECE 2011 Conference, IEEE Canada. H. R. Maghami, S. J. Ashtiani, “A New High Linear Widely Tunable Triode Transconductor”, Accepted in ICEE 2011 Conference, IEEE Tehran, Iran P. Payandeh-Nia, H. R. Maghami, S. Sheikhaei, “High Speed CML Latch Using Active Inductor in 0.18µm CMOS Technology”, Accepted in ICEE 2011 Conference, IEEE Tehran, Iran RESEARCH EXPERIENCES AND ACADEMICS PROJECTS Spring 2009, Design and simulation of a 1.8V 10-Bit 35MS/s Pipelined ADC with less than 13mW power using CLS (Correlated Level Shifting) method, ADC Course (HSPICE/MATLAB). Spring 2009, Design and simulation of a 1.8V 4Bit 2Gs/s Flash ADC in 0.18µm CMOS (ܸ =1.2ܸି ), ADC Course (HSPICE/MATLAB). Fall 2009, Design and simulation of a 2 GHz single-ended, inductive-degenerated common source LNA with an on-chip transformer load in 0.13µm CMOS, RFIC Design Course (ADS) Fall 2009, Design and simulation of a 2.6 GHz CMOS class-F power amplifier with harmonic control network, RFIC Design Course (ADS) Fall 2009, Design and simulation of a 0.18µm CMOS power amplifier for Ultra-Wideband(UWB) systems, RFIC Design Course (ADS) Fall 2009, Design and simulation of a 20 GHz power amplifier in 0.13µm CMOS, RFIC Design Course (ADS) Fall 2008, A 40 MS/s Sample & Hold Circuit with 90dB SNDR using a Class A/AB two stage folded-cascode OTA with less than 7mW power in 0.18µm CMOS, IC Design Course (HSPICE/MATLAB). Spring 2009, Propose and simulation of new dynamic body biasing methodologies for low power design, Low Power IC Design Course (HSPICE) Fall 2008, Design & Simulation FIFO1 & FIFO2 with Verilog and Synthesis of them with Leonardo, VLSI course (Verilog, Leonardo) Spring 2007, Design and implementation of a Advanced Encryption Standard (AES) processor on FPGA, VHDL Design Course (Active-HDL, ISE) Curriculum vitae Hamidreza Maghami Ph.D. Applicant Teaching Experiences: Linear Analog Integrated Circuits, Teaching Assistant, Fall 2009, School of ECE, University of Tehran, Presented by: Dr. S. J. Ashtiani. Communication Circuits, Teaching Assistant, Fall 2010, Spring 2010, School of ECE, University of Tehran, Presented by: Dr. M.Kamarei. Electronics II, Teaching Assistant, Fall 2010, Fall 2009, School of ECE, University of Tehran, Presented by: Dr. A. Afzali-Kusha. Electrical Circuits I, Teaching Assistant, Fall 2006, Ferdowsi University of Mashhad, Presented by: Dr. R. Lotfi. Electronics Lab II, Teaching Assistant, Fall 2009, Spring 2010, School of ECE, University of Tehran, Presented by: Dr. S. J. Ashtiani. Graduate Courses: • • • • • • • “Analog Integrated Circuits Design (IC Design)”, Prof. S. J.Ashtiani, Fall 2008, 19.2/20. (ranked 2nd) “ Silicon On Insulator (SOI)”, Prof. B. Forouzande, Fall 2008, 20/20. (ranked 1st) “VLSI Circuits”, Prof. M. Fakhraei, Fall 2008, 18/20. “Design of Data Converters (ADC/DAC)”, Prof. S. J.Ashtiani, Spring 2009, 20/20. (ranked 1st) “Low Power IC Design”, Prof. A. Afzali-Kusha, Spring 2009, 19.5/20. (ranked 1st) “Large Area Electronics”, Prof. S. J.Ashtiani, Spring 2009, 18.9/20. “RF IC Design”, Prof. S. Sheikhaei, Fall 2010, 18.9/20. COMPUTER SKILLS IC Design and Simulation HSPICE, ADS(Advanced Design System software by Agilent) Circuit Design and Simulation PSPICE, ORCAD, SIMULINK Programming Tools Matlab, C/C++, Verilog, Pascal, QBasic. EDA Tools Modelsim, Active-HDL, ISE, Programming Languages MATLAB, C++, VHDL, Verilog Application packages and other CAD Tools Leonardo, L-Edit, S-Edit, PROTEL, QCA Designer Curriculum vitae Hamidreza Maghami Ph.D. Applicant LANGUAGE SKILLS AND QUALIFICATIONS Native in Farsi, Fluent in English, Familiar with Arabic. REFERENCES Prof. Shahin J. Ashtiani Assistant Professor, Email: sashtiani@ut.ac.ir Prof. Reza Lotfi Associated Professor, E-mail: rlotfi@ieee.org Prof. Ali Afzali-Kusha Professor, E-mail: afzali@ut.ac.ir Prof. Mahmoud Kamarei Professor, E-mail: kamarei@ut.ac.ir Prof. Behjad Forouzande Assistant Professor, E-mail: bforooz@ut.ac.ir

![Amir Shams [ card ] 02](http://s2.studylib.net/store/data/005340099_1-e713f7ae67edd60d4c53ae5bb9448166-300x300.png)