AD8432 - Kalmeijer, Rob

advertisement

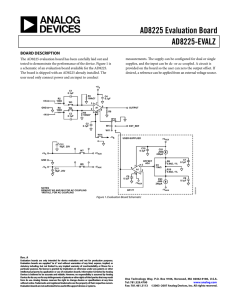

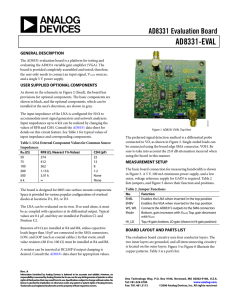

Dual-Channel Ultralow Noise Amplifier with Selectable Gain and Input Impedance AD8432 Low noise Input voltage noise: 0.85 nV/√Hz Current noise: 2.0 pA/√Hz High speed 200 MHz bandwidth (G = 12.04 dB) 295 V/µs slew rate Selectable gain G = 12.04 dB (×4) G = 18.06 dB (×8) G = 21.58 dB (×12) G = 24.08 dB (×16) Active input impedance matching Integrated input clamp diodes Single-ended input, differential output Supply range: 4.5 V to 5.5 V Low power: 60 mW/channel FUNCTIONAL BLOCK DIAGRAM ENB VPS1 VPS2 COMM BIAS AD8432 INH1 IND1 OPH1 LNA1 OPL1 GMH1 GOH1 GOL1 GML1 INL1 INH2 OPH2 IND2 LNA2 OPL2 GMH2 GOH2 GOL2 GML2 INL2 08341-001 FEATURES Figure 1. APPLICATIONS CW Doppler ultrasound front ends Low noise preamplification Predriver for I/Q demodulators and phase shifters Wideband analog-to-digital drivers GENERAL DESCRIPTION The AD8432 is a dual-channel, low power, ultralow noise amplifier with selectable gain and active impedance matching. Each channel has a single-ended input, differential output, and integrated input clamps. By pin strapping the gain setting pins, four accurate gains of G = 12.04 dB, 18.06 dB, 21.58 dB, and 24.08 dB (×4, ×8, ×12, and ×16, respectively) are possible. A bandwidth of 200 MHz at G = 12.04 dB makes this amplifier well suited for many high speed applications. The exceptional noise performance of the AD8432 is made possible by the active impedance matching. Using a feedback network, the input impedance of the amplifiers can be adjusted to match the signal source impedance without compromising the noise performance. Impedance matching and low noise in the AD8432 allow designers to create wider dynamic range systems that are able to detect even very low level signals. The AD8432 achieves 0.85 nV/√Hz input-referred voltage noise for a gain of 12.04 dB. The AD8432’s ultralow noise, low distortion, gain accuracy, and channel-to-channel matching are ideal for high performance ultrasound systems and for processing I/Q demodulator signals. The AD8432 operates on a single supply of 5 V at 24 mA. It is available in a 4 mm × 4 mm, 24-lead LFSCP. The LFCSP features an exposed paddle that provides a low thermal resistance path to the PCB, which enables more efficient heat transfer and increases reliability. The operating temperature range is −40°C to +85°C. Rev. A Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners. One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. www.analog.com Tel: 781.329.4700 Fax: 781.461.3113 ©2009-2010 Analog Devices, Inc. All rights reserved. AD8432 TABLE OF CONTENTS Features .............................................................................................. 1 Gain Setting Technique ............................................................. 18 Applications ....................................................................................... 1 Active Input Resistance Matching............................................ 19 Functional Block Diagram .............................................................. 1 Applications Information .............................................................. 21 General Description ......................................................................... 1 Typical Setup ............................................................................... 21 Revision History ............................................................................... 2 I/Q Demodulation Front End ................................................... 23 Specifications..................................................................................... 3 Differential-to-Single-Ended Conversion............................... 24 Absolute Maximum Ratings ............................................................ 5 Evaluation Board ............................................................................ 25 Thermal Resistance ...................................................................... 5 Gain Setting ................................................................................. 25 Maximum Power Dissipation ..................................................... 5 Schematic..................................................................................... 26 ESD Caution .................................................................................. 5 Power Supply............................................................................... 27 Pin Configuration and Function Descriptions ............................. 6 Input Termination ...................................................................... 27 Typical Performance Characteristics ............................................. 7 Output .......................................................................................... 27 Test Circuits ..................................................................................... 16 Outline Dimensions ....................................................................... 28 Theory of Operation ...................................................................... 18 Ordering Guide .......................................................................... 28 Low Noise Amplifier (LNA) ..................................................... 18 REVISION HISTORY 2/10—Rev. 0 to Rev. A Changes to General Description .................................................... 1 Changes to Figure 5, Figure 6, Figure 7, Figure 8 ......................... 7 Added Figure 27, Figure 29, and Figure 31, Renumbered Sequentially ..................................................................................... 11 Added Figure 33 and Figure 35..................................................... 12 Changes to Figure 58 ...................................................................... 16 10/09—Revision 0: Initial Version Rev. A | Page 2 of 28 AD8432 SPECIFICATIONS VS = 5 V, TA = 25°C, RS = RIN = 50 Ω, RFB =150 Ω, CSH = 47 pF, RSH = 15 Ω, RL = 500 Ω (per SE output), CL = 5 pF (per SE output), G = 12.04 dB (single-ended input to differential output), f = 1 MHz, unless otherwise specified. Table 1. Parameter DYNAMIC PERFORMANCE Gain Range Gain Error −3 dB Small Signal Bandwidth −3 dB Large Signal Bandwidth Slew Rate (Rising Edge) Slew Rate (Falling Edge) Overdrive Recovery Time DISTORTION/NOISE PERFORMANCE Input Voltage Noise Input Current Noise Noise Figure Unterminated Active Termination Output Referred Noise Harmonic Distortion 1 MHz (VOUT = 1 V p-p) 1 MHz (VOUT = 2 V p-p) 10 MHz (VOUT = 1 V p-p) 10 MHz (VOUT = 2 V p-p) Conditions Min Input to differential output (selectable gain) Input to single output (selectable gain) 12.04 6.02 RIN unterminated, RFB = ∞, CSH = 0 pF, RSH = 0 Ω G = 12.04 dB G = 18.06 dB G = 21.58 dB G = 24.08 dB VOUT = 2 V p-p VOUT = 2 V p-p, f = 10 MHz VOUT = 2 V p-p, f = 10 MHz Typ Max Unit 0.1 24.08 18.06 1 dB dB dB 200 90 50 32 42 295 170 10 MHz MHz MHz MHz MHz V/µs V/µs ns RFB = ∞ RFB = ∞ 0.85 2.0 nV/√Hz pA/√Hz RS = 50 Ω, RFB = ∞ RS = RIN = 50 Ω, RFB = 150 Ω RS = 50 Ω, RFB = 226 Ω, RIN = 75 Ω RS = 50 Ω, RFB = 301 Ω, RIN = 100 Ω RS = 50 Ω, RFB = 619 Ω, RIN = 200 Ω RS = 50 Ω, RFB = 3.57 kΩ, RIN = 1 kΩ G = 12.04 dB, RFB = ∞ G = 18.06 dB, RFB = ∞ G = 21.58 dB, RFB = ∞ G = 24.08 dB, RFB = ∞ 2.8 4.8 4.2 3.2 2.1 2.3 3.4 6.8 10.2 13.6 dB dB dB dB dB dB nV/√Hz nV/√Hz nV/√Hz nV/√Hz HD2 HD2, RS = 50 Ω, RIN unterminated HD3 HD3, RS = 50 Ω, RIN unterminated HD2 HD2, RS = 50 Ω, RIN unterminated HD3 HD3, RS = 50 Ω, RIN unterminated HD2 HD2, RS = 50 Ω, RIN unterminated HD3 HD3, RS = 50 Ω, RIN unterminated HD2 HD2, RS = 50 Ω, RIN unterminated HD3 HD3, RS = 50 Ω, RIN unterminated −67 −74 −103 −106 −65 −72 −103 −92 −66 −62 −78 −73 −60 −56 −72 −65 dBc dBc dBc dBc dBc dBc dBc dBc dBc dBc dBc dBc dBc dBc dBc dBc Rev. A | Page 3 of 28 AD8432 Parameter Two-Tone IMD3 Distortion 10 MHz 1 MHz Input 1dB Compression Point Output Third-Order Intercept 1 MHz 10 MHz 1 MHz 10 MHz Crosstalk DC PERFORMANCE Input Offset Voltage Input Offset Voltage Drift INPUT CHARACTERISTICS Input Voltage Range Input Resistance Input Capacitance Input Common-Mode Voltage OUTPUT CHARACTERISTCS Output Common-Mode Voltage Output Offset Voltage Output Voltage Swing Output Resistance Output Resistance in Shutdown Mode Output Short-Circuit Current Enable Response Time POWER SUPPLY Supply Voltage Quiescent Current Over Temperature Supply Current in Shutdown Mode Power Dissipation PSRR Conditions RS = 50 Ω, RIN unterminated VOUT = 1 V p-p, f1 = 9.5 MHz, f2 = 10.5 MHz VOUT = 2 V p-p, f1 = 9.5 MHz, f2 = 10.5 MHz VOUT = 1 V p-p, f1 = 0.9 MHz, f2 = 1.1 MHz VOUT = 2 V p-p, f1 = 0.9 MHz, f2 = 1.1 MHz f = 1 MHz f = 10 MHz Min VOUT = 1 V p-p of composite tones VOUT = 2 V p-p of composite tones VOUT = 1 V p-p of composite tones VOUT = 2 V p-p of composite tones VOUT = 1 V p-p of composite tones, reference to 50 Ω VOUT = 2 V p-p of composite tones, reference to 50 Ω VOUT = 1 V p-p of composite tones, reference to 50 Ω VOUT = 2 V p-p of composite tones, reference to 50 Ω VOUT = 1 V p-p, f = 1 MHz −6.25 AC-coupled RFB = 150 Ω RFB = 226 Ω RFB = 301 Ω RFB = 619 Ω RFB = 3.57 kΩ RFB = ∞, f = 100 kHz Typ Max −89.1 −66.0 −88.9 −73.7 7.5 7.7 dBc dBc dBc dBc dBm dBm 29.7 28.2 23.2 24.2 42.7 41.2 36.2 37.2 102 dBV rms dBV rms dBV rms dBV rms dBm dBm dBm dBm dB +1 300 +6.25 1.2 50 75 100 200 1 6.2 6 3.25 −25 Single-ended, either output Single-ended, either output RL = 10 Ω differential ENBON (enable high to output on) ENBOFF (enable low to output off) 4.5 ENB = 5 V TA = −40°C TA = +85°C ENB = GND G = 24.08 dB, f = 100 kHz, no bypass capacitors Rev. A | Page 4 of 28 Unit 2.5 +4 4.8 <0.1 2.5 77 200 200 5 24 21 27 50 120 −82 mV µV/°C V p-p Ω Ω Ω Ω kΩ kΩ pF V +25 5.5 100 V mV V p-p Ω kΩ mA µs µs V mA mA mA µA mW dB AD8432 ABSOLUTE MAXIMUM RATINGS MAXIMUM POWER DISSIPATION Table 2. Parameter Voltage Supply Voltage Input Voltage Power Dissipation Temperature Operating Temperature Storage Temperature Package Glass Transition Temperature (TG) Lead Temperature (Soldering, 60 sec) Rating 5.5 V 0 V to VPS 120 mW –40°C to +85°C –65°C to +150°C 150°C 300°C Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. The maximum safe power dissipation for the AD8432 is limited by the associated rise in junction temperature (TJ) on the die. At approximately 150°C, which is the glass transition temperature, the properties of the plastic change. Even temporarily exceeding this temperature limit may change the stresses that the package exerts on the die, permanently shifting the parametric performance of the amplifiers. Exceeding a temperature of 150°C for an extended period can cause changes in silicon devices, potentially resulting in a loss of functionality. ESD CAUTION THERMAL RESISTANCE θJA is specified for the worst-case conditions, that is, a device soldered in a circuit board for surface-mount packages. The θJA value in Table 3 assumes a 4-layer JEDEC standard board with zero airflow. Table 3. Thermal Resistance1 Parameter 40-Lead LFCSP 1 θJA 57.9 θJC 11.2 θJB 35.9 ΨJT 1.1 Unit °C/W 4-layer JEDEC board (2S2P). Rev. A | Page 5 of 28 AD8432 INH1 1 18 GOL1 INL1 2 17 OPL1 AD8432 IND1 3 16 COM1 TOP VIEW (Not to Scale) COMM 4 15 COM2 GML2 12 GMH2 11 9 OPH2 GOH2 10 IND2 7 14 OPL2 13 GOL2 VPS2 8 INL2 5 INH2 6 NOTES 1. EXPOSED PAD MUST BE CONNECTED TO GROUND. Figure 2. Pin Configuration Table 4. Pin Function Descriptions Pin No. 1 2 3, 7 4 5 6 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 Mnemonic INH1 INL1 IND1, IND2 COMM INL2 INH2 VPS2 OPH2 GOH2 GMH2 GML2 GOL2 OPL2 COM2 COM1 OPL1 GOL1 GML1 GMH1 GOH1 OPH1 VPS1 ENB EPAD Description LNA1 Noninverting Input. LNA1 Inverting Input (AC-Coupled to Ground). Integrated Input Clamping Back-to-Back Diodes. Input Ground. LNA2 Inverting Input (AC-Coupled to Ground). LNA2 Noninverting Input. 5 V Supply. Noninverting Output of LNA2. Gain Setting Pin for LNA2. Gain Setting Pin for LNA2. Gain Setting Pin for LNA2. Gain Setting Pin for LNA2. Inverting Output of LNA2. LNA2 Output Ground. LNA1 Output Ground. Inverting Output of LNA1. Gain Setting Pin for LNA1. Gain Setting Pin for LNA1. Gain Setting Pin for LNA1. Gain Setting Pin for LNA1. Noninverting Output of LNA1. 5 V Supply. Enable. Exposed pad must be connected to ground. Rev. A | Page 6 of 28 08341-002 20 GMH1 19 GML1 22 OPH1 21 GOH1 24 ENB 23 VPS1 PIN CONFIGURATION AND FUNCTION DESCRIPTIONS AD8432 TYPICAL PERFORMANCE CHARACTERISTICS VS = 5 V, TA = 25°C, RS = RIN = 50 Ω, RFB =150 Ω, CSH = 47 pF, RSH = 15 Ω, RL =500 Ω (per SE output), CL = 5 pF (per SE output), G = 12.04 dB (single-ended input to differential output), f = 1 MHz, unless otherwise specified. 24 30 24 18 18 12 6 6 GAIN (dB) GAIN (dB) 12 0 –6 0 –6 –12 –12 –24 = 24.08dB = 21.58dB = 18.06dB = 12.04dB –30 1 RIN UNTERMINATED RIN = 200Ω RIN = 100Ω RIN = 50Ω –18 10 100 1k FREQUENCY (MHz) –24 1 10 100 1k FREQUENCY (MHz) Figure 3. Small Signal Differential Gain vs. Frequency, RIN Unterminated 08341-056 G G G G 08341-003 –18 Figure 6. Small Signal Frequency Response vs. RIN, G = 21.58 dB 24 30 21 24 18 18 15 12 9 GAIN (dB) 6 3 0 0 –6 –3 –12 –12 1 RIN UNTERMINATED RIN = 200Ω RIN = 100Ω RIN = 50Ω –18 10 100 500 FREQUENCY (MHz) –24 08341-004 –9 1 10 100 1k FREQUENCY (MHz) Figure 4. Small Signal Frequency Response vs. RIN, G = 12.04 dB 08341-057 RIN UNTERMINATED RIN = 200Ω RIN = 100Ω RIN = 50Ω –6 Figure 7. Small Signal Frequency Response vs. RIN, G = 24.08 dB 24 30 18 24 12 18 12 GAIN (dB) 6 0 –6 6 0 –6 –12 –12 RIN UNTERMINATED RIN = 200Ω RIN = 100Ω RIN = 50Ω –18 –24 1 10 G G G G –18 100 1k FREQUENCY (MHz) 08341-055 GAIN (dB) 6 Figure 5. Small Signal Frequency Response vs. RIN, G = 18.06 dB = 24.08dB = 21.58dB = 18.06dB = 12.04dB –24 1 10 100 1k FREQUENCY (MHz) Figure 8. Differential Gain vs. Frequency, VOUT = 1 V p-p, RIN = 50 Ω Rev. A | Page 7 of 28 08341-058 GAIN (dB) 12 AD8432 30 240 24 230 INPUT IMPEDANCE (Ω) 18 6 0 –6 220 210 200 190 180 –12 –18 –24 = 24.08dB = 21.58dB = 18.06dB = 12.04dB 1 170 10 100 160 0.1 08341-011 G G G G 1k FREQUENCY (MHz) Figure 9. Differential Gain vs. Frequency, VOUT = 2 V p-p, RIN = 50 Ω G G G G = 24.08dB = 21.58dB = 18.06dB = 12.04dB 1 10 FREQUENCY (MHz) 08341-031 GAIN (dB) 12 Figure 12. Input Impedance RIN vs. Frequency, 200 Ω Active Termination 55 10 54 INPUT IMPEDANCE (kΩ) INPUT IMPEDANCE (Ω) 53 52 51 50 49 48 1 47 1 10 FREQUENCY (MHz) 0.1 0.1 10 3.5 3.0 OUTPUT IMPEDANCE (Ω) 110 105 100 95 G G G G = 24.08dB = 21.58dB = 18.06dB = 12.04dB 2.5 2.0 1.5 1.0 0.5 1 FREQUENCY (MHz) 10 0 0.1 08341-030 INPUT IMPEDANCE (Ω) 1 Figure 13. Input Impedance RIN vs. Frequency, Unterminated 115 85 0.1 = 24.08dB = 21.58dB = 18.06dB = 12.04dB FREQUENCY (MHz) Figure 10. Input Impedance RIN vs. Frequency, 50 Ω Active Termination 90 G G G G 08341-032 = 24.08dB = 21.58dB = 18.06dB = 12.04dB 1 10 FREQUENCY (MHz) Figure 11. Input Impedance RIN vs. Frequency, 100 Ω Active Termination Rev. A | Page 8 of 28 Figure 14. Output Impedance vs. Frequency 100 08341-033 45 0.1 G G G G 08341-029 46 AD8432 1.00 0.1 0.1 1 10 100 FREQUENCY (MHz) 0.90 0.85 0.80 0.75 0.70 –50 10 100 OUTPUT VOLTAGE NOISE (nV/√Hz) 1k SOURCE RESISTANCE (Ω) 70 90 90 12 G = 21.58dB 10 8 G = 18.06dB 6 4 G = 12.04dB –30 –10 10 30 50 70 TEMPERATURE (°C) Figure 16. Input-Referred Voltage Noise vs. Source Resistance (RS) Figure 19. Output Voltage Noise vs. Temperature 1.6 f = 1MHz G = 24.08dB G = 21.58dB 10 G = 18.06dB G = 12.04dB 1.2 1.0 0.8 0.6 0.4 0.2 1 1 10 100 1k SOURCE RESISTANCE (Ω) Figure 17. Output-Referred Voltage Noise vs. Source Resistance (RS) 0 0.01 G G G G = 24.08dB = 21.58dB = 18.06dB = 12.04dB 0.1 1 10 FREQUENCY (MHz) Figure 20. Input Voltage Noise vs. Frequency Rev. A | Page 9 of 28 100 08341-221 INPUT VOLTAGE NOISE (nV/√Hz) 1.4 08341-035 OUTPUT-REFERRED VOLTAGE NOISE (nV/√Hz) 50 G = 24.08dB 14 2 –50 08341-036 INPUT-REFERRED VOLTAGE NOISE (nV/√Hz) RS THERMAL NOISE ALONE 100 30 16 f = 1MHz 1 10 Figure 18. Input Voltage Noise vs. Temperature 1 0.1 –10 TEMPERATURE (°C) Figure 15. Output Impedance vs. Frequency in Disable Mode 10 –30 08341-037 1 0.95 08341-038 INPUT VOLTAGE NOISE (nV/√Hz) 10 08341-034 OUTPUT IMPEDANCE (kΩ) 100 AD8432 –40 20 G G G G 16 HD2, 10MHz HD2, 1MHz HD3, 10MHz HD3, 1MHz MEASUREMENT LIMIT –50 –60 14 DISTORTION (dBc) OUTPUT VOLTAGE NOISE (nV/√Hz) 18 = 24.08dB = 21.58dB = 18.06dB = 12.04dB 12 10 8 6 –70 –80 –90 4 –100 0.1 1 10 100 FREQUENCY (MHz) Figure 21. Output Voltage Noise vs. Frequency 0 –110 08341-222 0 0.01 0 1.0 1.5 2.0 2.5 3.0 3.5 4.0 4.5 VOUT (V p-p) Figure 24. Harmonic Distortion vs. Differential Output Voltage, G = 12.04 dB –40 LOW TONE HIGH TONE –10 0.5 08341-225 2 –50 –20 –60 DISTORTION (dBc) IMD3 (dBc) –30 –40 –50 –60 –70 –70 HD2, 10MHz HD2, 1MHz HD3, 10MHz HD3, 1MHz MEASUREMENT LIMIT –80 –90 –80 –100 1 10 100 FREQUENCY (MHz) Figure 22. IMD3 vs. Frequency 50 –110 08341-223 –100 0 1.0 1.5 2.0 2.5 3.0 3.5 4.0 4.5 VOUT (V p-p) Figure 25. Harmonic Distortion vs. Differential Output Voltage, G = 24.08 dB –50 G = 24.08dB G = 12.04dB 45 0.5 08341-226 –90 40 –60 DISTORTION (dBc) 30 25 20 15 –70 –80 HD2, HD2, HD3, HD3, 5 0 1 10 FREQUENCY (MHz) 100 Figure 23. Output Third-Order Intercept vs. Frequency 10MHz, 10MHz, 10MHz, 10MHz, 2V p-p 1V p-p 2V p-p 1V p-p –90 0 5 10 15 CL (pF) 20 25 08341-227 10 08341-224 OIP3 (dBm) 35 Figure 26. Harmonic Distortion at 10 MHz vs. Capacitive Load (CL), G = 12.04 dB Rev. A | Page 10 of 28 AD8432 –50 –50 HD2, HD2, HD3, HD3, 2V p-p 1V p-p 2V p-p 1V p-p HD2, HD2, HD3, HD3, –55 DISTORTION (dBc) –70 –80 –90 10MHz, 10MHz, 10MHz, 10MHz, 2V p-p 1V p-p 2V p-p 1V p-p –60 –65 –70 –100 0 5 10 15 20 25 CL (pF) –75 08341-269 –110 0 200 400 600 800 1000 1200 1400 1600 1800 2000 RL (Ω) Figure 27. Harmonic Distortion at 1 MHz vs. Capacitive Load (CL), G = 12.04 dB 08341-229 DISTORTION (dBc) –60 1MHz, 1MHz, 1MHz, 1MHz, Figure 30. Harmonic Distortion at 10 MHz vs. Resistive Load (RL), G = 12.04 dB –60 –40 –50 HD2, HD2, HD3, HD3, –65 1MHz, 1MHz, 1MHz, 1MHz, 1V p-p 2V p-p 2V p-p 1V p-p –60 DISTORTION (dBc) DISTORTION (dBc) –70 –70 –80 –90 –75 –80 –85 2V p-p 1V p-p 2V p-p 1V p-p –90 –100 0 5 10 15 20 25 30 35 CL (pF) –95 0 200 400 600 800 1000 1200 1400 1600 1800 2000 RL (Ω) 08341-271 10MHz, 10MHz, 10MHz, 10MHz, 08341-228 HD2, HD2, HD3, HD3, Figure 31. Harmonic Distortion at 1 MHz vs. Resistive Load (RL), G = 12.04 dB Figure 28. Harmonic Distortion at 10 MHz vs. Capacitive Load (CL), G = 24.08 dB –50 –60 –55 –70 DISTORTION (dBc) –80 –90 –100 –65 –70 –75 –80 –85 HD2, HD2, HD3, HD3, –120 0 5 10 15 20 25 1MHz, 1MHz, 1MHz, 1MHz, 30 1V p-p 2V p-p 2V p-p 1V p-p HD2, HD2, HD3, HD3, –90 35 CL (pF) Figure 29. Harmonic Distortion at 1 MHz vs. Capacitive Load (CL), G = 24.08 dB –95 0 200 400 600 800 10MHz, 10MHz, 10MHz, 10MHz, 2V p-p 1V p-p 2V p-p 1V p-p 1000 1200 1400 1600 1800 2000 RL (Ω) Figure 32. Harmonic Distortion at 10 MHz vs. Resistive Load (RL), G = 24.08 dB Rev. A | Page 11 of 28 08341-230 –110 08341-270 DISTORTION (dBc) –60 AD8432 –60 –70 HD2, HD2, HD3, HD3, –65 1MHz, 1MHz, 1MHz, 1MHz, 1V p-p 2V p-p 2V p-p 1V p-p –75 –80 –85 CROSSTALK (dB) DISTORTION (dBc) –70 –75 –80 –90 –95 –100 –105 –85 –110 –90 0 200 400 600 800 1000 1200 1400 1600 1800 2000 RL (Ω) –120 0.1 1 10 100 FREQUENCY (MHz) Figure 36. Channel Crosstalk vs. Frequency Figure 33. Harmonic Distortion at 1 MHz vs. Resistive Load (RL), G = 24.08 dB –50 1V/DIV –70 –90 HD2, HD2, HD3, HD3, 10MHz, 10MHz, 10MHz, 10MHz, 2V p-p 1V p-p 2V p-p 1V p-p –100 2 4 6 8 10 12 14 16 18 GAIN (V/V) 100ns/DIV Figure 34. Harmonic Distortion at 10 MHz vs. Gain –50 HD2, HD2, HD3, HD3, Figure 37. Overdrive Recovery, G = 12.04 dB 2V p-p 1V p-p 2V p-p 1V p-p 1V/DIV –70 –80 –90 –110 2 4 6 8 10 12 14 16 GAIN (V/V) 18 Figure 35. Harmonic Distortion at 1 MHz vs. Gain 100ns/DIV Figure 38. Overdrive Recovery, G = 24.08 dB Rev. A | Page 12 of 28 08341-013 –100 08341-273 DISTORTION (dBc) –60 1MHz, 1MHz, 1MHz, 1MHz, 08341-132 –80 08341-231 DISTORTION (dBc) –60 08341-232 –95 08341-272 –115 AD8432 CL = 5pF CL = 10pF CL = 15pF CL = 20pF CL = 30pF G = 24.08dB 50mV/DIV 200mV/DIV G = 21.58dB G = 18.06dB 10ns/DIV 08341-017 08341-014 G = 12.04dB 10ns/DIV Figure 39. Small Signal Transient Response vs. Gain, VIN = 100 mV p-p Figure 42. Small Signal Transient Response vs. Capacitive Load (CL), G = 24.08 dB 10ns/DIV 08341-018 08341-015 50mV/DIV 100mV/DIV RL = 499Ω RL = 249Ω RL = 24.9Ω RL = 15Ω RL = 10Ω 10ns/DIV Figure 40. Small Signal Transient Response, G = 12.04 dB Figure 43. Small Signal Transient Response vs. Resistive Load (RL), G = 12.04 dB CL = 15pF CL = 10pF CL = 5pF 10ns/DIV Figure 41. Small Signal Transient Response vs. Capacitive Load (CL), G = 12.04 dB 08341-019 10ns/DIV 08341-016 50mV/DIV 50mV/DIV RL = 499Ω RL = 249Ω RL = 24.9Ω RL = 15Ω RL = 10Ω Figure 44. Small Signal Transient Response vs. Resistive Load (RL), G = 24.08 dB Rev. A | Page 13 of 28 AD8432 CL = 30pF CL = 20pF CL = 15pF CL = 10pF CL = 5pF G = 18.06dB 08341-020 50mV/DIV 500mV/DIV G = 21.58dB G = 24.08dB 10ns/DIV 08341-023 G = 12.04dB 10ns/DIV Figure 45. Small Signal Transient Response vs. Gain, VOUT = 200 mV p-p Figure 48. Large Signal Transient Response vs. Capacitive Load (CL), G = 24.08 dB RL = 499Ω RL = 249Ω RL = 24.9Ω RL = 15Ω G = 24.08dB 500mV/DIV 500mV/DIV G = 21.58dB G = 18.06dB 10ns/DIV 08341-024 08341-021 G = 12.04dB 10ns/DIV Figure 46. Large Signal Transient Response vs. Gain, VIN = 125 mV p-p Figure 49. Large Signal Transient Response vs. Resistive Load (RL), G = 12.04 dB RL = 499Ω RL = 249Ω RL = 24.9Ω RL = 15Ω RL = 10Ω 10ns/DIV Figure 47. Large Signal Transient Response vs. Capacitive Load (CL), G = 12.04 dB 08341-025 10ns/DIV 08341-022 500mV/DIV 500mV/DIV CL = 20pF CL = 15pF CL = 10pF CL = 5pF Figure 50. Large Signal Transient Response vs. Resistive Load (RL), G = 24.08 dB Rev. A | Page 14 of 28 AD8432 G = 12.04dB 140 G = 18.06dB G = 21.58dB G = 24.08dB 500mV/DIV SUPPLY CURRENT (µA) 120 100 80 60 40 10ns/DIV 0 –60 –40 –20 0 20 40 60 80 100 TEMPERATURE (°C) Figure 51. Large Signal Transient Response vs. Gain, VOUT = 2 V p-p Figure 54. Supply Current vs. Temperature in Disable Mode –20 ENB 5V/DIV –30 1 PSRR (dB) –40 –50 –60 OUTPUT 50mV/DIV –70 2 –80 0.1 1 10 100 FREQUENCY (MHz) TIME (100µs/DIV) 08341-252 –100 0.01 08341-248 G = 24.08dB NO BYPASS CAPS –90 Figure 55. Small Signal Enable Response Figure 52. PSRR vs. Frequency 30 ENB 5V/DIV 1 26 OUTPUT 500mV/DIV 24 2 20 –60 –40 –20 0 20 40 60 TEMPERATURE (°C) 80 100 TIME (100µs/DIV) Figure 56. Large Signal Enable Response Figure 53. Supply Current vs. Temperature Rev. A | Page 15 of 28 08341-251 22 08341-027 SUPPLY CURRENT (mA) 28 08341-028 08341-026 20 AD8432 TEST CIRCUITS 0.1µF RFB 1MHz (10MHz LPF) INH OPH AD8432 0.1µF INL 0.1µF 1.7MHz (10.7MHz) G=1 RL 50Ω LP 56.2Ω AD8130 LNA1 CSH HP 475Ω RL 50Ω 08341-046 0.1µF OPL INH INL RSH 1MHz (10MHz) SPECTRUM ANALZYER DUAL FILTER 0.1µF Figure 57. Harmonic Distortion vs. Resistive Load (RL) Measurements 0.1µF RFB DUAL FILTER SPECTRUM ANALYZER LP 50Ω 1MHz (10MHz LPF) RSH OPL INL OPH 0.1µF CL 26.1Ω 487Ω HP 1:1 IN LNA1 1.7MHz (10.7MHz) CL 26.1Ω RL Figure 58. Harmonic Distortion vs. Capacitive Load (CL) Measurements NETWORK ANALYZER 50Ω OUT 50Ω 0.1µF RSH 499Ω 0.1µF INH OPL AD8432 0.1µF 5pF DIFF PROBE 0.1µF OPH INL CSH IN 0.1µF 499Ω LNA1 08341-047 RFB 5pF Figure 59. Frequency Response Measurements SPECTRUM ANALYZER 0.1µF 0.1µF INH OPL INL OPH 50Ω 1kΩ 0.1µF AD8432 LNA1 50Ω 0.1µF AD8432 CSH 487Ω 0.1µF 1kΩ AD8129 G = 10 Figure 60. Voltage Noise Measurements Rev. A | Page 16 of 28 08341-048 1MHz (10MHz) 0.1µF INH 08341-049 0.1µF AD8432 5pF 0.1µF RFB 10MHz X MULTIPLIER 0.1µF INH OPL 0.1µF 499Ω DIFF PROBE OSCILLOSCOPE CH1 RSH Y INL CSH OPH AD8432 1MHz LNA1 0.1µF 499Ω 5pF 08341-050 0.1µF Figure 61. Overdrive Recovery Measurements 499Ω 50Ω 0.1µF OUT RSH 0.1µF INH OPL INL OPH CSH 0.1µF 5pF 499Ω AD8432 0.1µF LNA1 08341-051 NETWORK ANALYZER 5pF 0.1µF RFB Figure 62. Input Impedance vs. Frequency Measurements 0.1µF RFB NETWORK ANALYZER 0.1µF 0.1µF INH RSH INL CSH OPH 0.1µF AD8432 499Ω LNA1 08341-052 0.1µF 50Ω OPL Figure 63. Output Impedance vs. Frequency Measurements RFB 0.1µF SPECTRUM ANALYZER INH1 OPL1 0.1µF +IN 1kΩ RS INL1 0.1µF AD8432 OUT 50Ω –IN OPH1 0.1µF 1kΩ AD8129 G = 10 LNA1 Figure 64. Noise Figure Measurements Rev. A | Page 17 of 28 08341-054 0.1µF AD8432 THEORY OF OPERATION LOW NOISE AMPLIFIER (LNA) differential gain of G = 12.04 dB, the maximum input voltage allowed is 1.2 V p-p. The AD8432 is a dual-channel, ultralow noise amplifier with integrated pin-strappable, gain-setting resistors. The resistors can be externally connected to achieve differential gains of 12.04 dB, 18.06 dB, 21.58 dB, and 24.08 dB (×4, ×8, ×12, and ×16, respectively). A simplified schematic of an LNA is shown in Figure 65. Clamping the inputs ensures quick recovery from large input voltages. The input back-to-back diodes, which are integrated inside the die (IND1 and IND2), should be used for the lowest gain configuration (12.04 dB) to protect the input from overdriving. They should be connected after the source resistance or before the INH coupling capacitor. The LNA is driven with a single-ended input and measured differentially at the output. The inverting input INL must be ac-coupled to ground through a capacitor for proper operation. The LNA cannot be driven differentially due to the asymmetry of the internal gain setting resistors. The gain from the inverting input INL to the single-ended output (OPH or OPL) does not match the gain from the noninverting input INH to the singleended output. The use of a fully differential topology and negative feedback minimizes distortion. A differential signal enables smaller swings at each output, which results in reduction of third-order distortion. The AD8432 is a voltage feedback amplifier. Due to gain bandwidth product (GBW), a decrease in bandwidth should be expected as the gain increases. Table 5 displays the values of the −3 dB bandwidth for each gain with unterminated input impedance. The AD8432 inputs have a dc bias voltage of 3.25 V, which is generated internally. The inputs must be ac-coupled through a series capacitor to maintain the dc bias level of the inputs. Likewise, the AD8432 outputs have a dc bias voltage of 2.5 V. An ac coupling capacitor in series with each single-ended output is recommended to prevent improper loading of the outputs. The AD8432 inputs have a dc bias voltage of 3.25 V, which is generated internally. The inputs must be ac-coupled through a series capacitor to maintain the dc bias level of the inputs (see CINL and CINH in Figure 65). GAIN SETTING TECHNIQUE Pin strapping is used to set the gain of the amplifier. Gain setting resistors are integrated in the LNA and are accessible externally through the GOH, GMH, GML, and GOL pins. By externally shorting these pins, and thereby shorting or connecting the internal resistors, the AD8432 can be configured for four different gains. Table 5 shows which pins must be connected to achieve the desired gain. The AD8432 supports a differential output voltage of 4.8 V p-p for the common-mode output voltage of 2.5 V. Therefore, for a CFB RFB VPS I I OPL OPH INL Q1 Q2 CINH RSH INH RG4 48Ω RG3 24Ω RG2 12Ω RG1 12Ω RG7 48Ω RG6 24Ω RG5 24Ω CINL CSH RS GND GOH GMH I I GND GML GOL GND Figure 65. Simplified Schematic of LNA Rev. A | Page 18 of 28 08341-039 VS AD8432 Table 5. Gain Setting Using a Pin-Strapping Technique and −3 dB Bandwidth for Each Gain Configuration Differential Gain (dB) 12.04 Single Gain (dB) 6.02 −3 dB BW (MHz) 200 RG1 (Ω) 12 RG2 (Ω) 12 18.06 12.04 90 12 12 21.58 15.56 50 12 12 24.08 18.06 32 12 12 RG3 (Ω) Connect GMH to GOH 24 Connect GMH to GOH 24 RG4 (Ω) Connect GOH to OPH Connect GOH to OPH 48 RG5 (Ω) 24 48 24 The single-ended gain from INH to OPH (see Figure 65) is defined as 48 INH LNA VOUT VIN UNTERMINATED RIN RS INH LNA R + RG6 + RG7 = − G5 RG1 VOUT RS VIN RESISTIVE TERMINATION The values of the seven gain resistors were chosen so that both single-ended gains are equal. For example, to set a gain of 12.04 dB (G = ×4) differentially, the gain from INH to each output (OPH, OPL) should be 6.02 dB (G = ×2). RFB RIN RS INH LNA VOUT VIN INH to OPH: For RG1 = RG2 = RG, then ACTIVE IMPEDANCE MATCH R G1 + R G2 2 × RG = =2 R G1 RG Figure 66. Input Resistance Matching To achieve this active impedance match, connect a feedback resistor, RFB, between the INH and OPL (see Figure 66). RIN is given in Equation 1, where G/2 is the single-ended gain. INH to OPL: For RG1 = RG and RG5 = 2 × RG, then G OPL − INH = − Connect GML to GOL 24 RIN R + RG2 + RG3 + RG4 = G1 RG1 G OPH − INH = 24 RS The single-ended gain from INH to OPL is defined as G OPL − INH 24 RG7 (Ω) Connect GOL to OPL Connect GOL to OPL 48 08341-009 G OPH − INH RG6 (Ω) Connect GML to GOL 24 2 × RG RG5 =− = −2 RG1 RG R IN = ACTIVE INPUT RESISTANCE MATCHING The AD8432 reduces noise and optimizes signal power transfer by using active input termination to perform signal source resistance matching. The primary purpose of input impedance matching is to optimize the input signal power transfer. With resistive termination, the input noise increases due to the thermal noise of the terminating resistor and the increased contribution of the input voltage noise generator of the LNA. With active impedance matching, however, the contributions of both are smaller than they are for resistive termination by a factor of 1/(1 + ½ LNA) gain. The noise figure (NF) for the three terminating schemes is shown in Figure 67. R FB G 1+ 2 (1) In addition, to further reduce the input resistance, there is an internal resistance of 6.2 kΩ in parallel with the source resistance, such that R IN = R FB R G INTERNAL 1+ 2 (2) Equation 3 should be used to calculate RFB accurately for a desired input resistance and single-ended gain. Refer to Table 6 for calculated results for RFB for several input resistance and gain combinations. ⇒ R FB Rev. A | Page 19 of 28 G R IN 1 + 2 = , R INTERNAL = 6.2 kΩ R IN 1− R INTERNAL (3) AD8432 8 The user must determine the level of matching accuracy desired and adjust RFB accordingly. The RFB and CFB network presents a load to OPL that OPH does not see. The user can add an identical load on OPH to improve slightly the distortion caused by this imbalance. 7 NOISE FIGURE (dB) 6 RESISTIVE TERMINATION (RS = RIN) 5 4 There is a feedback capacitor (CFB) in series with RFB (see Figure 65) because the dc levels of the positive output and the positive input are different. At higher frequencies, the value of the feedback capacitor must be considered. ACTIVE IMPEDANCE MATCH 3 2 UNTERMINATED 1 (SIMULATED RESULTS) 100 1k 08341-267 0 50 RS (Ω) Figure 67. Noise Figure vs. RS for Resistive, Active Match, and Unterminated Inputs 18 16 NOISE FIGURE (dB) 14 The unterminated bandwidth (RFB = ∞) is 200 MHz. The AD8432 has a low input-referred voltage noise of 0.85 nV/√Hz at the lowest gain, 12.04 dB (unterminated configuration). To achieve such low noise, the dual amplifier consumes 24 mA, resulting in a power consumption of 120 mW. RIN = 1kΩ RIN = 200Ω RIN = 100Ω RIN = 75Ω RIN = 50Ω RIN = UNTERMINATED 12 10 8 6 4 2 (SIMULATED RESULTS) 100 1k RS (Ω) 08341-268 0 50 Figure 68. Noise Figure vs. RS for Various Values of RIN, Actively Matched Table 6. Feedback Resistance for Several RIN and Gain Combinations Desired RIN (Ω) 50 75 100 200 1k 50 100 50 100 50 100 Differential Gain (V/V) 4 4 4 4 4 8 8 12 12 16 16 Single-Ended Gain, G/2 (V/V) 2 2 2 2 2 4 4 6 6 8 8 Exact RFB (Ω), Equation 2 151.2 227.8 304.9 620 3.58 k 252 508.2 352.9 711.5 453.7 914.8 Rev. A | Page 20 of 28 RFB (Ω), 1% Standard Value 150 226 301 619 3.57 k 250 511 357 715 453 909 Actual RIN (Ω), Equation 2 49.6 74.4 98.7 199.7 998.4 49.6 100.5 50.6 100.5 49.9 99.4 AD8432 APPLICATIONS INFORMATION The unterminated input impedance of the AD8432 is 6.2 kΩ. Any input resistance between 50 Ω and 6.2 kΩ can be synthesized using active impedance matching. The AD8432 LNA provides precision gain and ultralow noise performance with minimal external components. Because it is a high performance part, care must be taken to ensure that it is configured optimally to attain the best performance and dynamic range for the system. At the lowest gain (12.04 dB), the gain response exhibits some peaking at higher frequencies. A resistor-capacitor shunt network (RC) at the input (see RSHx and CSHx in Figure 69) is recommended to reduce gain peaking and enhance stability at higher frequencies. TYPICAL SETUP The internal bias circuitry of the AD8432 sets the input bias voltage at 3.25 V and the output bias voltage at 2.5 V. It is important to ac couple the inputs through a capacitor to maintain the internal dc bias levels. When active input termination is used (RFB), a decoupling capacitor (CFB) is required to isolate the input and output bias voltages of the LNA. A typical value for CFB is 0.1 µF, but a smaller value capacitor is more appropriate at higher frequencies. Table 7 shows the recommended values of RFB, CSH, and RSH for all four gains and several input impedance combinations. The values for the CSH and RSH network are determined empirically and can be customized as needed to optimize performance. As RIN increases, the value of CSH diminishes, and for higher input impedance values, no capacitor may be required. CFB1 0.1µF RFB1 FB 120nH G = 12dB 0.1µF 0.1µF ENB VPS1 COMM VPS2 BIAS FB 120nH 0.1µF IN1 RSH1 15Ω CSH1 47pF INH1 IND1 LNA1 0.1µF IN2 RSH2 15Ω CSH2 47pF OPL1 INL1 GMH1 GOH1 GOL1 GML1 INH2 IND2 OPH2 0.1µF FB 120nH LNA2 INL2 0.1µF 0.1µF OPH1 OPL2 GMH2 GOH2 GOL2 GML2 OUT1+ RL CL OUT1– 0.1µF 0.1µF OUT2+ RL CL OUT2– 0.1µF RFB2 08341-040 AD8432 CFB2 0.1µF Figure 69. Typical AD8432 Setup, G = 12.04 dB Rev. A | Page 21 of 28 AD8432 Table 7. External Component Selections for Common Input Impedance RIN (Ω) 50 75 100 200 1k Unterminated, RS = 50 Ω Unterminated, RS = 0 Ω Gain (dB) 12 18 21 24 12 18 21 24 12 18 21 24 12 18 21 24 12 18 21 24 12 18 21 24 12 18 21 24 RFB (Ω) 150 249 357 453 226 383 536 681 301 511 715 909 619 1.02 k 1.43 k 1.87 k 3.57 k 5.9 k 8.25 k 10.7 k ∞ ∞ ∞ ∞ ∞ ∞ ∞ ∞ CSH (pF) 47 30 None None 36 None None None 30 None None None 18 None None None 10 None None None None None None None None None None None Rev. A | Page 22 of 28 RSH (Ω) 15 15 None None 15 None None None 15 None None None 15 None None None 10 None None None None None None None None None None None −3 dB BW (MHz) 176 116 117 87 167 144 100 72 164 134 90 63 164 116 74 51 160 99 61 43 178 95 59 40 210 96 55 38 AD8432 I/Q DEMODULATION FRONT END 4LOP and 4LON pins of the AD8339, has a frequency 4× that of the RF inputs. The AD8339 downconverts the RF signals, generates quadrature, and phase-shifts the resultant I and Q signals. The AD8432 low noise amplifiers can be used to drive the differential RF inputs of the dual AD8333 or the quad AD8339 I/Q demodulators. The primary application for the AD8339 is phased array beamforming in medical ultrasound, specifically in CW Doppler processing. Other applications include phased array radar and smart antennas for mobile communications. The I and Q outputs of the AD8339 are current outputs. A transimpedance amplifier, such as the AD8021, processes the outputs and performs several functions, including the following: • • • AD8021 Q1 0.1µF 20Ω RF1P 787Ω Q1OP 2.2nF AD8339 AD8432 RF1N In beamforming applications, the I and Q outputs of a number of receiver channels are summed, which increases the system dynamic range by 10 log10 (N), where N is the number of channels being summed. The external RC feedback network of the AD8021 is a 100 kHz low-pass filter as shown in Figure 70. See the AD8333 and AD8339 datasheets for more details on implementing I/Q demodulators. 2.2nF I1OP 20Ω 787Ω 0.1µF 4LO 08341-041 I1 0.1µF AD8021 Current-to-voltage conversion Summation amplifier for multiple channels Active low-pass filter Figure 70. Block Diagram of AD8432 and AD8339 Application for Ultrasound Beamforming Evaluation boards are available for the AD8432 and the AD8339 to facilitate system level design and testing. A detailed reference schematic of the setup is shown in Figure 71. The AD8432 is shown in this configuration with a gain of 12.04 dB, with unterminated inputs. If active termination is preferred, use an RFB and CFB network as discussed in the Theory of Operation section. The IND1/IND2 clamping diodes can be connected to IN1/IN2 to protect the LNA input from being overdriven. Because of its low output noise and low distortion, the AD8432 ensures minimal degradation in dynamic range while amplifying the RF input signal. At the lowest gain of 12.04 dB, the AD8432 contributes only 3.4 nV/√Hz output voltage noise. Figure 70 shows a simplified block diagram of one channel of the AD8432 driving the AD8339. The AD8432 outputs can be connected directly to the AD8339 RF inputs through 20 Ω resistors. A differential clock signal, 4LO, which is applied to the 4LO 0.1µF 0.1µF 0.1µF IN1 RSH1 15Ω CSH1 47pF VPS1 VPS2 BIAS INH2 RSH2 15Ω CSH2 47pF IND2 VPOS VNEG 4LOP 2 7 OPH1 20Ω RF1P Q1OP OPL1 20Ω RF1N I1OP 0.1µF Q1 + Q2 3 4 0.1µF +5V OPL2 GMH2 GOH2 GOL2 GML2 INL2 0Ω + −5V OPH2 LNA2 6 AD8021 GMH1 GOH1 GOL1 GML1 0.1µF 0.1µF 787Ω 0.1µF – LNA1 INL1 IN2 0.1µF 2.2nF COMM INH1 IND1 0.1µF +5V 20Ω RF2P 787Ω Q2OP 0.1µF 20Ω RF2N 2.2nF I2OP 2 7 – AD8339 6 AD8021 0Ω I1 + I2 + G = –1.3dB AD8432 3 4 LPF fC = 100kHz G = 12dB 0.1µF −5V Figure 71. Schematic of the AD8432 (G = 12.04 dB) and AD8339 Application for Ultrasound Beamforming Rev. A | Page 23 of 28 08341-043 ENB −5V +5V AD8432 DIFFERENTIAL-TO-SINGLE-ENDED CONVERSION A transformer or balun can also be used to convert the differential output of the AD8432 to a single-ended output. Transformers have lower distortion; however, care must be taken to properly match the impedance of the transformer. The test circuit for distortion measurements in Figure 58 uses an ADTT1-1 transformer to perform differential-to-single-ended conversion. Some applications require the low noise and high dynamic range of the AD8432; however, they may also require a singleended output, rather than a differential output. The AD8129 or AD8130 differential receiver amplifier can be used for the differential-to-single-ended conversion of the AD8432 output, as shown in Figure 72. The AD8129 is a low noise, high gain (10 or greater) amplifier intended for applications over very long cables, where signal attenuation is significant. The AD8130 is stable at a gain of 1 and can be used for applications where lower gains are required. The AD8129 and AD8130 have user-adjustable gain, set by the ratio of two resistors, to help compensate for losses in the transmission line. 0.1µF 0.1µF 0.1µF IN1 VPS1 COMM INL1 0.1µF G = 12 dB +VS AC-COUPLING CAPS SERIES 20Ω RESISTORS IF DRIVING (AD8432 HAS 2.5V OUTPUT BIAS) HIGH CAP LOAD INH1 IND1 RSH1 15Ω CSH1 47pF VPS2 BIAS LNA1 GMH1 GOH1 GOL1 GML1 OPH1 20Ω 0.1µF OPL1 20Ω 0.1µF 499Ω 1 8 499Ω 4 5 + – + – 7 6 VOUT1 2 AD8130 499Ω RESISTORS PROVIDE BIAS CURRENT PATH AND TERMINATION IF NECESSARY –VS Figure 72. AD8432 Differential-to-Single-Ended Conversion Using the AD8129/AD8130 with Unity Gain Rev. A | Page 24 of 28 08341-044 ENB AD8432 EVALUATION BOARD Figure 73 shows the AD8432 evaluation board, and the schematic diagram is shown in Figure 74. Using the board is a convenient and fast way to verify system design and assess the performance of the AD8432 under user-specific operating conditions. The board provides access to all LNA inputs, outputs, and gain setting pins. The board is shipped in a typical G = 12.04 dB configuration but is designed to allow customization of the setup as required. The AD8432-EVALZ requires a single 5 V power supply. An on-board switch (S1) allows VPS to drive the enable (ENB) input. GAIN SETTING Table 8 outlines the resistors or headers that must be installed or shorted for each gain configuration. Table 8. Gain Setting Using Resistors or Headers R1 R2 R3 R4 1 LNA2 R9 W9 R10 W10 R11 W11 R12 W12 4 X1 X1 X1 X1 X = shorting the indicated header or resistor. 08341-045 Headers (W5 to W12) are provided across the gain setting pins and can be shorted using jumpers to allow gain setting quickly and easily. Alternately, it is recommended to short the gain setting pins using surface-mount (0402), 0 Ω resistors (R1 to R4, R9 to R12) that eliminate the small parasitic capacitances from longer trace lengths to the headers. As shipped, the evaluation board is configured for G = 12.04 dB with these 0 Ω resistors. LNA1 W5 W6 W7 W8 Figure 73. Evaluation Board Rev. A | Page 25 of 28 Gain (V/V) 8 12 X1 X1 X1 X1 16 Figure 74. Schematic Rev. A | Page 26 of 28 7 IND2 VPS2 9 OPH2 8 VPS2 L4 CFB2 0.1µF 120nH FB DNI OPH2 VPOS W4 12 GML2 W9 W10 GOH2 GMH2 R9 R10 0Ω 0Ω 10 GOH2 C4 0.1µF PIN 0 EXPOSED PADDLE (TIED TO GND) TOP VIEW (Not to Scale) AD8432 11 GMH2 RFB2 DNI C6 0.1µF ENB 24 RSH2 15Ω CSH2 47pF INH2 6 INL2 5 COMM 4 VPS1 23 INH2 COMM INL2 IND1 3 INL1 2 INH1 1 R2 0Ω GML1 19 W2 INL1 C1 0.1µF RSH1 15Ω OPH1 22 C2 0.1µF CSH1 47pF R1 0Ω R3 0Ω W7 GML2 W11 R11 0Ω 13 GOL2 14 OPL2 15 COM2 16 COM1 17 OPL1 18 GOL1 GOH1 GMH1 W5 W6 GML1 OPH1 GND BANANA GND JACK GOH1 21 PRB2 PRB1 S1 C3 ENB 0.1µF VPS1 C5 PIN 1 0.1µF INH1 IDENTIFIER ENABLE DISABLE +5V L3 120nH FB W3 VPOS GMH1 20 L2 IN2 120nH FB W1 L1 IN1 120nH FB GND1 GND2 GND3 RFB1 DNI CFB1 0.1µF DNI BANANA JACK VPOS GOL2 R12 0Ω COM1 R4 0Ω GOL1 W12 OPL2 OPL1 W8 R13 DNI PRB4 R14 DNI R6 DNI PRB3 R5 DNI RL3 DNI RL4 DNI RL2 DNI RL1 DNI CL3 C13 DNI 0.1µF DNI CL4 DNI C14 0.1µF DNI CL2 C10 DNI 0.1µF DNI CL1 DNI GND4 GND5 GND6 C11 0.1µF DNI C12 0.1µF DNI C8 0.1µF DNI C7 0.1µF DNI C9 0.1µF DNI R15 453Ω DNI 6 T2 4 2 R16 453Ω DNI R8 453Ω DNI 6 T1 4 2 R7 453Ω DNI TEST POINT AD8432 EVALUATION BOARD SCHEMATIC OPH2 R18 0Ω VOUT2 3 DNI 1 OPL2 OPL1 R17 0Ω VOUT1 3 DNI 1 OPH1 AD8432 SCHEMATIC 08341-042 AD8432 POWER SUPPLY OUTPUT The AD8432 should be powered by a single 5 V supply connected to the VPOS terminal. Separate supplies can be used for VPS1, VPS2, and ENB, or they can all be tied to VPOS by shorting the W3 and W4 headers and the S1 switch. Ferrite beads and decoupling capacitors are installed for isolation, protection, and power supply noise reduction. The AD8432 evaluation board provides the space to configure the output loading conditions required by the user, by populating the given footprints (for example, RL1, RL2, C7, and C8). SMA connectors are available at the outputs, and space for a transformer is also available for differential-to-single-ended conversion. INPUT TERMINATION Active input impedance matching can be realized by installing a feedback resistor (RFB), the value of which is determined by the gain and source impedance, as described in the Theory of Operation section. CFB provides the necessary ac coupling between the input and output when using active termination; a 0.1 µF capacitor value is recommended. The RFB and CFB network presents a load to OPL, and an equivalent load at OPH can be used to balance the differential output. The 4-pin headers, PRB3 and PRB4, are placed close to the AD8432, and they provide a way for monitoring the differential output or the single-ended output using a high impedance differential probe. The two inner pins of the headers are connected to OPL/OPH, and the two outer pins of the headers are connected to ground. There are several footprints provided to install ac coupling capacitors at the outputs (C7 to C14). The AD8432 outputs are biased internally at 2.5 V. To maintain the dc bias level, use coupling capacitors between the outputs and the load. Input clamping diodes (IND1 and IND2) can be connected to the inputs by shorting the connection on the W1 and W2 headers. The diodes provide overvoltage protection to the input and enable faster overdrive recovery times, especially at the lowest gain (12.04 dB). Rev. A | Page 27 of 28 AD8432 OUTLINE DIMENSIONS PIN 1 INDICATOR 4.10 4.00 SQ 3.90 0.30 0.25 0.18 0.50 BSC PIN 1 INDICATOR 24 19 18 1 2.65 2.50 SQ 2.45 EXPOSED PAD TOP VIEW 0.80 0.75 0.70 0.50 0.40 0.30 13 12 0.25 MIN BOTTOM VIEW 0.05 MAX 0.02 NOM COPLANARITY 0.08 SEATING PLANE 6 7 FOR PROPER CONNECTION OF THE EXPOSED PAD, REFER TO THE PIN CONFIGURATION AND FUNCTION DESCRIPTIONS SECTION OF THIS DATA SHEET. COMPLIANT TO JEDEC STANDARDS MO-220-WGGD. 112108-A 0.20 REF Figure 75. 24-Lead Lead Frame Chip Scale Package [LFSCP_WQ] 4 mm × 4 mm, Very Very Thin Quad (CP-24-7) Dimensions shown in millimeters ORDERING GUIDE Model 1 AD8432ACPZ-R7 AD8432ACPZ-RL AD8432ACPZ-WP AD8432-EVALZ 1 Temperature Range −40°C to +85°C −40°C to +85°C −40°C to +85°C Package Description 24-Lead LFCSP_WQ, 7” Tape and Reel 24-Lead LFCSP_WQ, 13” Tape and Reel 24-Lead LFCSP_WQ, Waffle Pack Evaluation Board Z = RoHS Compliant Part. ©2009-2010 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. D08341-0-2/10(A) Rev. A | Page 28 of 28 Package Option CP-24-7 CP-24-7 CP-24-7